MOSFETs and CMOS Inverter¶

Goal¶

- Measure threshold voltage and Ids-Vgs in forced saturation configuration.

- Measure the Ids-Vds curves for a multiple Vgs values.

- An understanding of MOSFET switching circuits.

- Build a CMOS inverter.

- Experiment with overlocking and underclocking a CMOS circuit

- More experience with the ELVIS II, Labview and the oscilloscope

- Continue to develop professional lab skills and written communication skills.

Required Components¶

Required Soft Front Panels (SFPs)¶

- 2-wire I-V analyzer

- FGEN

- Scope

- DMM

- Digital Writer

Overview¶

A thorough treatment of MOSFETs can be found in Chapter 4 of the ELEC 2210 textbook, Microelectronics Circuit Design by R.C. Jaeger.

Transistor Characteristics¶

In this lab, we will first measure the I-V characteristics of MOSFETs, including:

- Ids-Vgs in a saturation by connection configuration, e.g. with gate tied to the drain, from which we can determine threshold voltage.

- Ids-Vds curves for multiple gate-to-source voltages (Vgs), from which we can observe linear and saturation operation regions.

Using measured threshold voltage and Ids-Vds curves, we can then check how well first-order MOSFET theory holds up in real devices and get a practical feel of the limitation of first-order theoretical MOSFET equation.

The MOSFETs we will use in this experiment are from ALD1105, an IC containing two n-MOSFETs and two p-MOSFETs. A circuit symbol description of the two pairs of transistors from the data sheet is shown below in figure 1.

Note each transistor has four terminals: drain (D), source (S), gate (G), and substrate, which is called body (B) in our text. As we learned in class, all the n-MOSFETs on an IC share the same p-type body, which needs to be tied to the lowest voltage in a system to keep all the source/drain to body PN junctions zero or reverse biased.

Similarly, all the p-MOSFETs on an IC share the same n-type body, which needs to be tied to the highest voltage in a system to keep all the source/drain to body PN junctions zero or reverse biased.

The pin diagram seen in figure 2 shows the package layout and various pin connections for ALD1105.

MOSFET as a Switch¶

A MOSFET is a natural voltage-controlled switch, as illustrated in figure 3. A high gate voltage turns on the MOSFET channel, allowing current to flow between drain and source, thereby turning a load, which can be a LED, a speaker or a fan.

The amount of current the MOSFET can provide depends on the transistor physical properties such as width, length, oxide thickness, etc., the gate voltage, and the load.

CMOS Inverter¶

MOSFETs are mostly used in CMOS circuits. There are many advantages of CMOS, with the biggest being zero standby power consumption, at least ideally.

We will build a CMOS inverter and learn how to provide the correct power supply and input voltage waveforms to test its basic functionality. For a given supply VDD, your voltage low should be zero, and voltage high should be VDD.

By default, the function generator gives an output that varies from -VPP/2 to +VPP/2, with VPP being peak-to-peak voltage. For a square wave, the voltage low is -VPP/2, voltage high is +VPP/2. You can set the DC offset to VPP/2 to make voltage low 0.

We will build complex CMOS logic gates and sequential CMOS circuits from scratch using transistors in other labs.

Pre-Lab¶

- Using the datasheet, determine the values of the threshold voltage range, the maximum continuous drain current ID, the maximum drain-source voltage, and the maximum allowed power dissipation, Ptot.

- In which region should the MOSFET be operating when it is a closed switch? Why? In which region should it be operating when it is an open switch? Why?

- Draw a pin-level wiring diagram of a CMOS inverter. Use the pair of NMOS and PMOS gates on the right side of the ALD1105 IC.

- For a VDD of 3V, 5V, 7V, sketch the input waveforms required to test the functionality of the CMOS inverter. Determine the VPP and dc offset setting required for function generator.

Lab Exercise¶

There are 6 parts and a bonus. Have your GTA sign off on each part before proceeding to the next part.

Vtn and Ids-Vgs in Saturation¶

On the data sheet, the threshold voltage is defined to be the value of Vgs when ID = 1 uA when the transistor is biased at saturation. The data sheet uses the notation Vgs(th) for the threshold voltage, whereas our text uses the notation Vtn.

We can force a transistor to work in saturation by connecting the drain and gate. We can then measure the I-V curve of this diode-like circuit using the 2-wire analyzer. The threshold voltage can then be determined from the voltage at which current equals a set threshold.

Proceed as follows:

- Obtain a ALD1105 IC. Using the data sheet as a guide, identify the drain, gate, and source terminals of the NMOS transistor using Pins 1-4.

- Power off ELVIS II board.

- Connect the gate to the drain, the drain to DUT+ and the Source and Substrate to DUT- as seen below:

Open the 2-wire Analyzer SFP.

Turn on the ELVIS II.

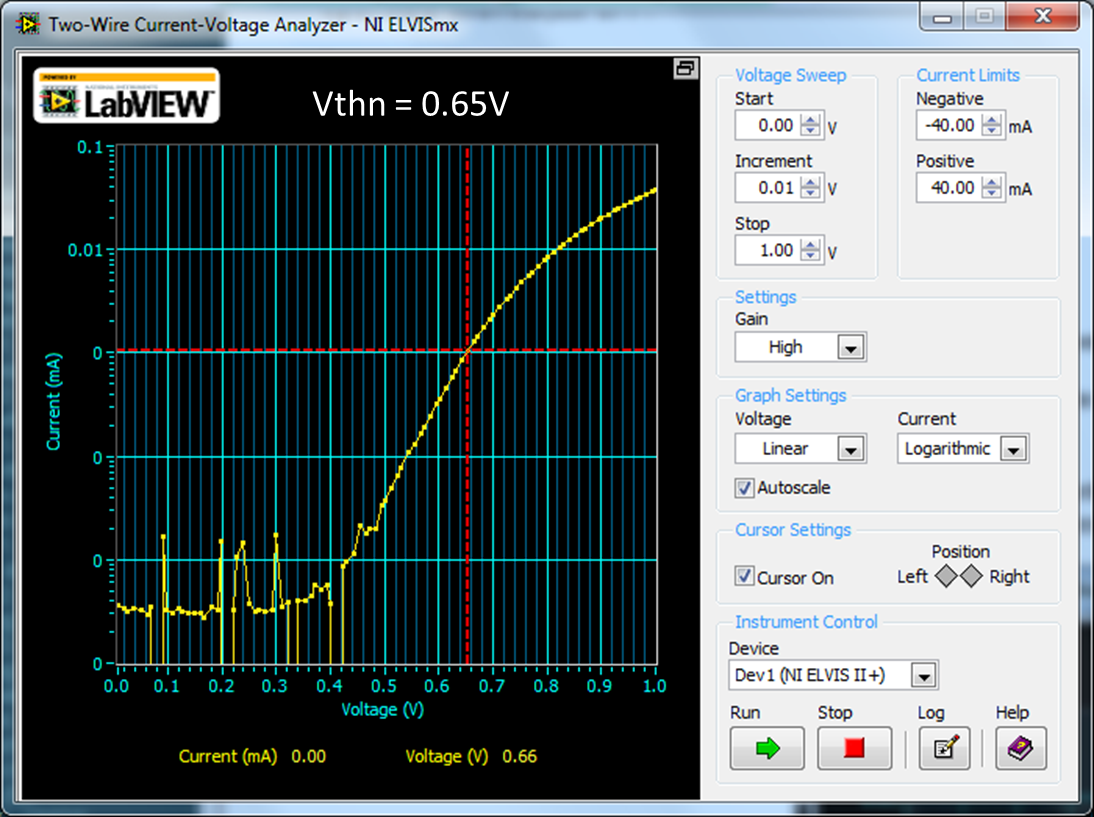

Run the 2-wire analyzer using the following settings.

- Increment = .01 V

- Start = 0 V, Stop = 1V

- Gain = High

- Current = Logarithmic

The high gain setting is necessary to accurately measure low current levels required for threshold voltage determination.

In the 2-wire SFP select the Cursor On box. This will allow you to see the current and voltage values at specific points. Using this check the voltage value at the point where Id = 1uA. Does your value of Vtn fall within the range specified on the data sheet?

As you can see from the screen shots provided below, some significant figures are lost on the y-axis as very small current readings are measured. This is the result of the ELVIS II unit measuring correct values but the y-axis being unable to display below a certain threshold.

What to do in the lab report

Include all screen shots.

Determine Vtn. Compare with data sheet threshold voltage specifications.

Ids vs Vds using SFPs¶

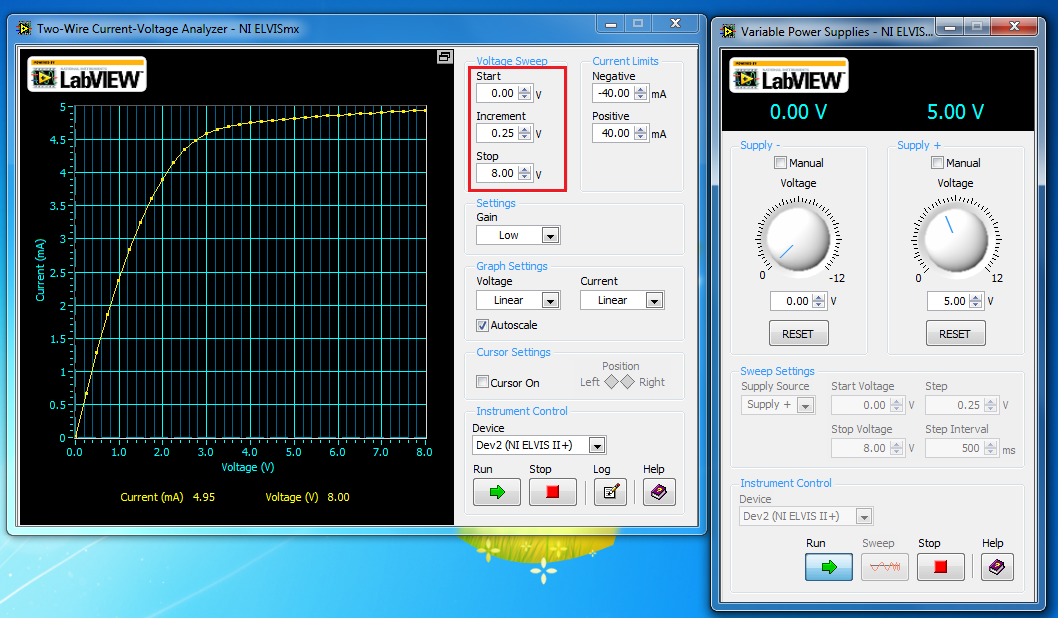

In this part you will be using the 2-Wire SFP and the same NMOS from the previous experiment in order to trace Ids as a function of Vds for several values of Vgs.

Proceed as follows:

Make sure the ELVIS II power is turned off.

Connect the gate to the VPS+.

Connect the body to the source.

Connect the drain to DUT+.

Connect the source/body to DUT-.

The DUT- is at a virtual ground, so the source is at approximately ground. Do NOT connect DUT- to ground, however, as it will interfere with the 2-wire measurement to be used.

Open the 2-Wire SFP and Variable Power Supply SFP.

Set the VPS+ to 5 V and click Run.

Prepare the 2-wire analyzer using the following settings:

- Increment = .25 V

- Start = 0 V, Stop = 8V

- Gain = Low

Power on the ELVIS II board.

Click the Run button on the 2-Wire SFP.

Repeat this process 2 more times changing the VPS to different values of your own choice, e.g. 6V and 8V, to see the different curves. A sample curve is shown below.

What to do in the lab report

Submit all screen shots.

Ids-Vds Using Custom Labview Program¶

In the previous section, the gate voltage had to be adjusted manually. To automate the measurement, we desire to have a curve tracer program like the 3-wire analyzer SFP that came with ELVIS II we had used earlier to measure bipolar transistors.

Unfortunately, that 3-wire curve tracer SFP is designed to work with bipolar transistors only. To make your lab easier, I have written a customized MOSFET curve tracer program.

Proceed as follows:

- Make sure the ELVIS II power is turned off.

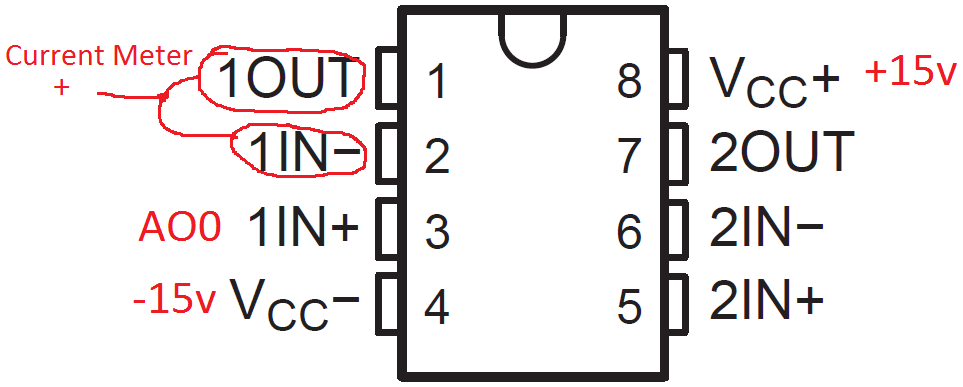

- Make the connections to an rc4558 op-amp as shown in figure 7.

- Connect AO1 to the ALD1105 NMOS gate (pin 2), connect the current meter common terminal to the NMOS drain (pin 1), and connect the NMOS source and body (pins 3 and 4) to ground.

- Open the LabVIEW program provided here.

- Use the following settings:

- Vgs start = 2V, Vgs stop = 6V, no. of Vgs steps = 5

- Vds start = 0V, Vds step = 8V, no. of Vds steps = 30

- Power on the ELVIS II board.

- Click the Run button on the toolbar in the top or select Operate->Run from the title menu. Your should see a graph similar to the one shown below in figure 8.

- Save a screen shot.

- Power off the ELVIS breadboard.

- Connect AO1 to the PMOS gate (pin 6), connect the current meter common terminal to the PMOS drain (pin 5), and connect the PMOS source and body (pins 7 and 11) to ground.

- Open the LabVIEW program provided here.

- Use the following settings:

- Vgs start = -2V, Vgs stop = -6V, no. of Vgs steps = 5

- Vds start = 0V, Vds step = -8V, no. of Vds steps = 30

- Power on the ELVIS II board.

- Click run.

- Save a screenshot.

What to do in the lab report

Submit all screen shots.

Find the Vds at which the drain current saturates, defined as Vdsat, for all Vgs measured.

Compare measured Vdsat with 1st order theory, i.e. Vdsat = Vgs-Vtn. Use Vtn determined earlier.

MOSFET Switching Circuits¶

Here we experiment with turning on and off a LED and a speaker with a n-MOSFET.

An LED¶

Make sure the ELVIS II power is turned off.

Construct the circuit shown in figure 9 using the ALD1105.

Use a 330

series resistor and 5V supply voltage.

series resistor and 5V supply voltage.Connect the Function Generator to the Gate.

Connect the Analog Input (AI) Channels as shown in the diagram.

Power on the ELVIS II board.

Open the Function Generator SFP.

Set the Frequency to 5 Hz, the Amplitude to 10 V, and the DC offset to 5 V.

Open the Scope SFP. Set the inputs.

Click Run on both panels.

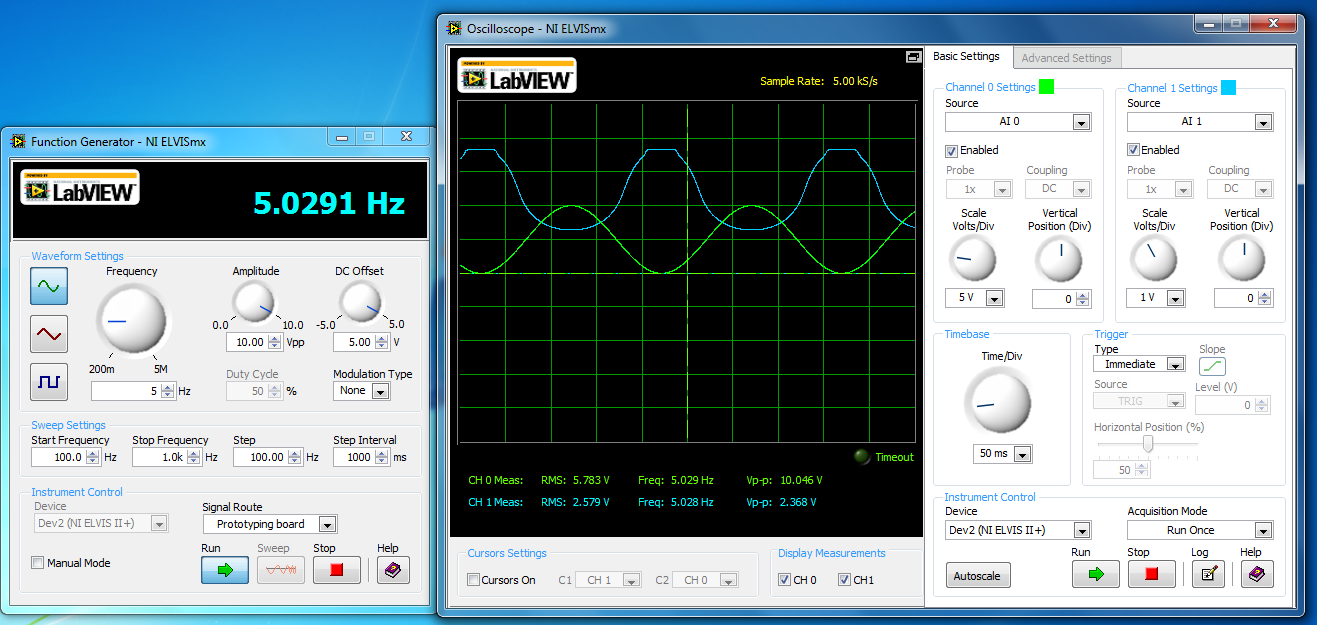

Set the frequency to about 5 Hz initially, and then try different blink rates. Your scope should look similar to the graph in figure 10.

What to do in the lab report

Submit all screenshots.

Measure Vgs and Vds when the LED is on and when it is off.

Identify which region, linear or saturation, the MOSFET is operating in when the LED is turned on and when it is turned off. Use the measured Ids-Vgs curves for this purpose instead of first-order theory.

CMOS Inverter¶

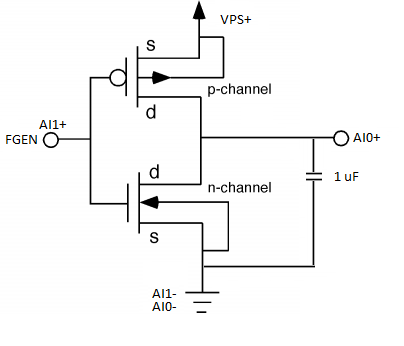

Let us now construct and test a CMOS inverter from scratch using the ALD1105. Proceed as follows:

Make sure the ELVIS II power is turned off.

Construct the circuit shown in figure 11 using the pin-level diagram from the pre-lab.

Connect the Analog Input (AI) Channels as shown in the diagram.

Power on the ELVIS II board.

Open the Function Generator SFP and VPS SFP.

Set the Frequency to 5 Hz, the VPP to 5V, and the DC offset to 2.5 V. Select square wave. The VPP and DC offset combination gives a voltage low of 0 and voltage high of 5V.

Note

It is important to notice that the DC offset should always be 1/2 the Vpp. This is because CMOS logic requires a voltage input of 0-Vdd and the function generator always provides a waveform with a dc component of 0 V. That is, “positive” peak is at Vpp/2, and “negative” peak is at -Vpp/2. Therefore, it is necessary to always provide an offset equal to 1/2 Vpp to move the “negative” peak, or the voltage low to 0..

Open the Scope SFP.

Click Run on both panels.

Your output should look similar to figure 12.

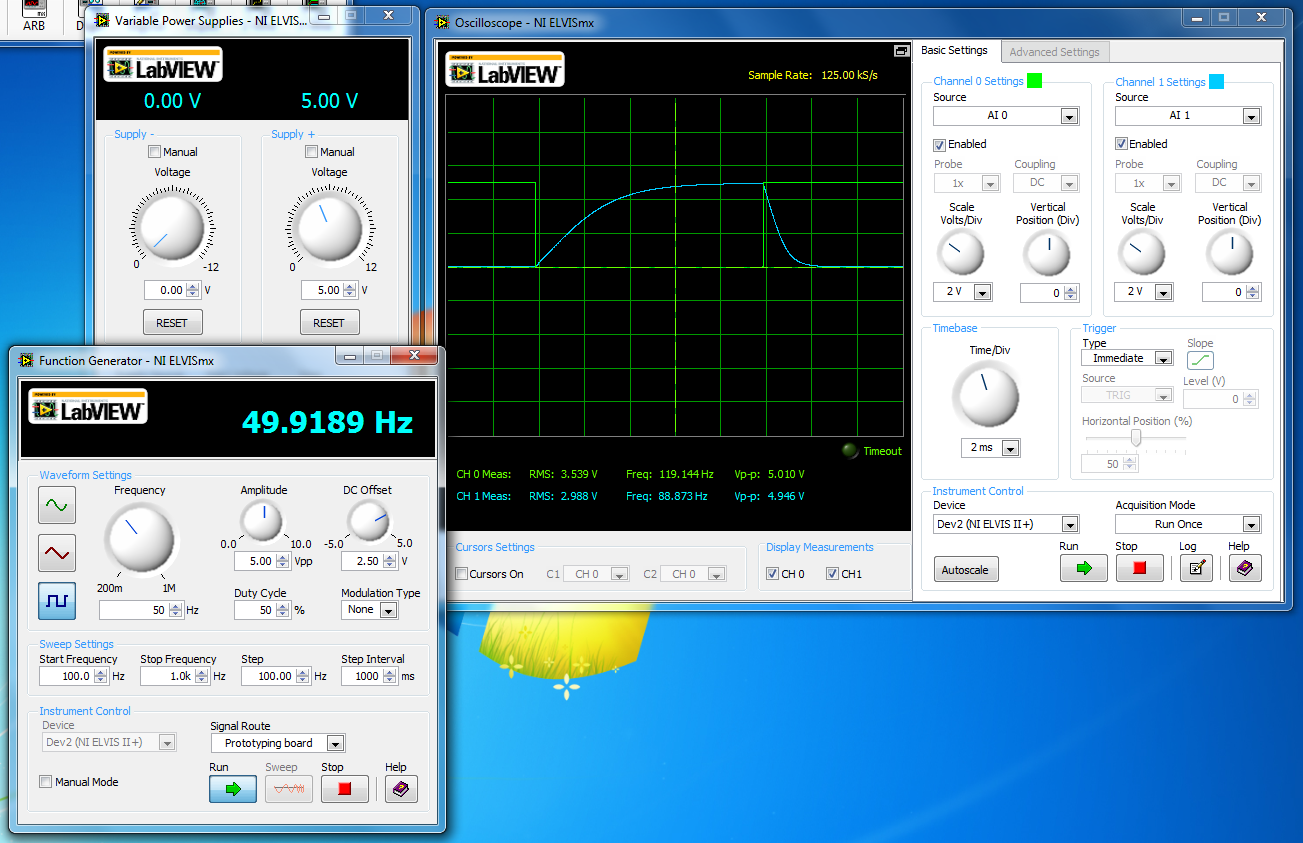

Add a capacitor load between the output and ground. A value of 1 uF is good to start with. Adjust frequency until you can see a clear rise and fall of the output signal. Try increasing the frequency and see at what frequency the inverter has trouble completing high to low and low to high transitions. Take screen shots.

Vary VPS+ and FGEN settings to test the same CMOS inverter for VDD=3V. Take screen shots.

Vary VPS+ and FGEN settings to test the same CMOS inverter for VDD=7V. Take screen shots.

The inverter will be used in the next part.

What to do in the lab report

Attach screen shots for working frequencies, and for too high frequencies such that transitions between 0 and VDD are not complete.

Attach screen shots for different VDD.

Discuss the impact of VDD on the low-to-high delay and high-to-low delay of the inverter.

CMOS Inverter Voltage Transfer Curve¶

Now the voltage transfer curve of the inverter will be measured using LabVIEW.

Remove the capacitor from the previous step.

Connect the input of the inverter to AO0 instead of FGEN, as shown in figure 13.

Download the LabVIEW program here.

- Use the following settings:

Vin start = 0v Vin stop = 5v nsteps = 30

Save a screenshot of the graph.

Right click on the graph and export the data for later analysis.

What to do in the lab report

Show 1 screenshot.

At what input voltage does the output transition to logic low?

Bonus¶

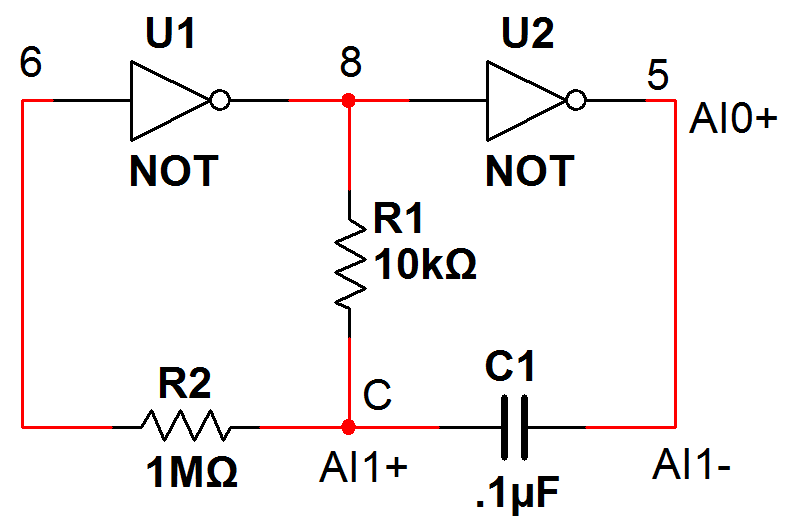

Consider the circuit shown in figure 14. Can you tell what it does?

First, assume the voltage at the input to the first inverter is zero. The output of the first inverter will be Vdd and the output of the second inverter will be zero. The capacitor will begin to charge. Because the input to a CMOS inverter is very high impedance, the resistor R2 can be ignored. Thus, the input to the first inverter is close to the voltage at node C. When node C reaches 1/2 Vdd, the inverters will change states, and the voltage at the output of the second inverter will now be Vdd. Because the voltage across the capacitor cannot change quickly, the voltage at the bottom center node will now be Vdd + Vcap, or about 3/2 Vdd. Because the output of the first inverter is now zero, the capacitor will begin to discharge through R1, and the opposite side will be charged. When the voltage at node C drops to 1/2 Vdd (making the voltage across the capacitor -1/2 Vdd), the inverters will change states. The output of the second inverter will be 0v again, and the voltage at node C will now be 0 + Vcap or 0 -1/2 Vdd. The capacitor will begin to charge through R1 until node C reaches 1/2 Vdd and the process repeats.

In summary, the output of the inverters will oscillate between 0 and Vdd. Therefore, this circuit is an oscillator.

Construct the circuit shown in figure 14. The two inverters can be built from a CD4007 by making the following connections: (4,7);(1,5);(3,8,13);(14,2);(14,Vdd);(7,Ground). You may find the diagram shown below in figure 15 helpful.

Connect AI0- to ground.

Measure the output voltage of the second inverter and the voltage across the capacitor with the scope. Save a screenshot.

Measure the output voltage of the second inverter and the voltage at node C with the scope. Save a screenshot.

Experiment with different values of C1 and R1 and try to determine their relationship to the frequency of the output.

What to do in the lab report

Show 1 screenshot.

How does changing R1 and C1 affect the frequency of the output?