# Lecture 6 - Modeling of Memory and Register Files

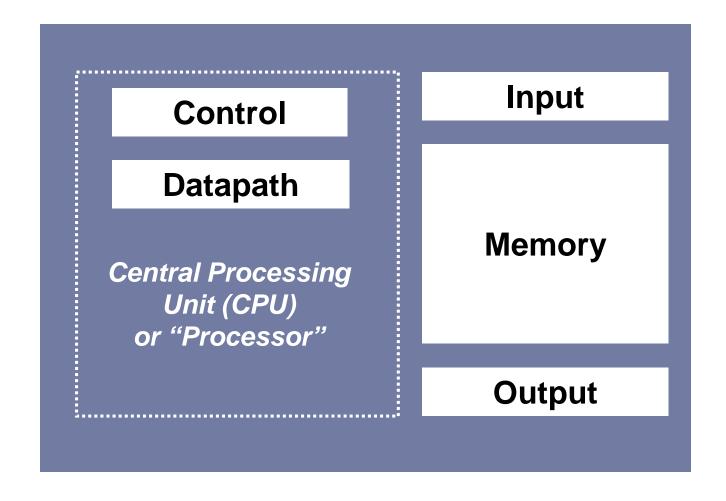

# A typical Computing System

### Types of Computer Memories

#### From the cover of:

A. S. Tanenbaum, *Structured Computer Organization, Fifth Edition*, Upper Saddle River, New Jersey: Pearson Prentice Hall, 2006.

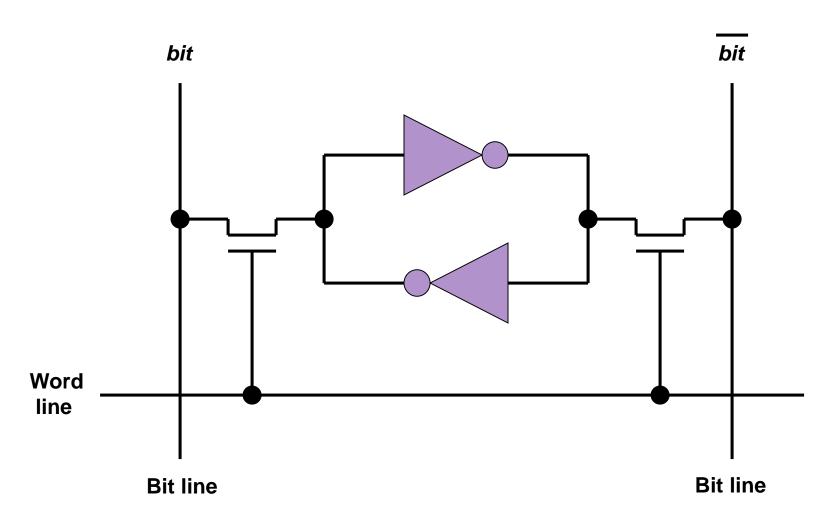

## Random Access Memory (RAM)

#### Six-Transistor SRAM Cell

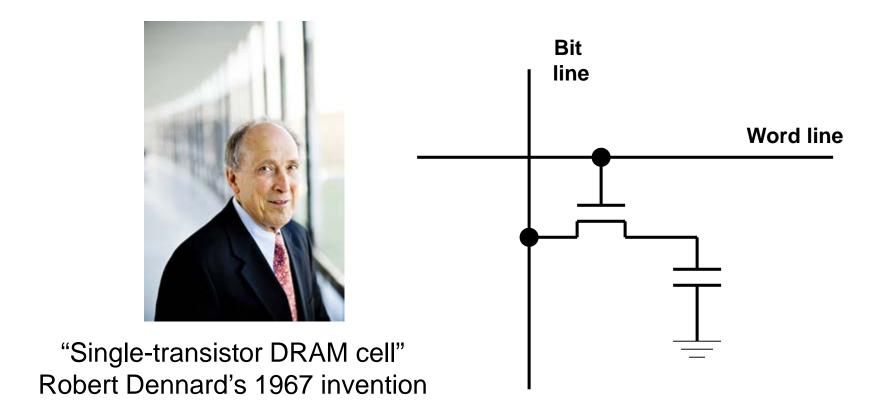

# Dynamic RAM (DRAM) Cell

## **Electronic Memory Devices**

| Memory technology          | Typical access time         | \$ per GiB in<br>2012 |

|----------------------------|-----------------------------|-----------------------|

| SRAM semiconductor memory  | 0.5–2.5 ns                  | \$500-\$1000          |

| DRAM semiconductor memory  | 50–70 ns                    | \$10–\$20             |

| Flash semiconductor memory | 5,000–50,000 ns             | \$0.75–\$1.00         |

| Magnetic disk              | 5,000,000—<br>20,000,000 ns | \$0.05-\$0.10         |

#### For more on memories:

Semiconductor Memories: A Handbook of Design, Manufacture and Application, by Betty Prince, Wiley 1996.

*Emerging Memories: Technologies and Trends*, by Betty Prince, Springer 2002.

## **DRAM** Evolution

| Year<br>introduced | Chip size | \$ per GiB  | Total access time to a new row/column | Average column access time to existing row |

|--------------------|-----------|-------------|---------------------------------------|--------------------------------------------|

| 1980               | 64 KiB    | \$1,500,000 | 250 ns                                | 150 ns -                                   |

| 1983               | 256 KiB   | \$500,000   | 185 ns                                | 100 ns                                     |

| 1985               | 1 MeB     | \$200,000   | 135 ns                                | 40 ns                                      |

| 1989               | 4 MeB     | \$50,000    | 110 ns                                | 40 ns                                      |

| 1992               | 16 MeB    | \$15,000    | 90 ns                                 | 30 ns                                      |

| 1996               | 64 MeB    | \$10,000    | 60 ns                                 | 12 ns                                      |

| 1998               | 128 MeB   | \$4,000     | 60 ns                                 | 10 ns                                      |

| 2000               | 256 MeB   | \$1,000     | 55 ns                                 | 7 ns                                       |

| 2004               | 512 MeB   | \$250       | 50 ns                                 | 5 ns                                       |

| 2007               | 1 GiB     | \$50        | 45 ns                                 | 1.25 ns                                    |

| 2010               | 2 GiB     | \$30        | 40 ns                                 | 1 ns                                       |

| 2012               | 4 GiB     | \$1         | 35 ns                                 | 0.8 ns                                     |

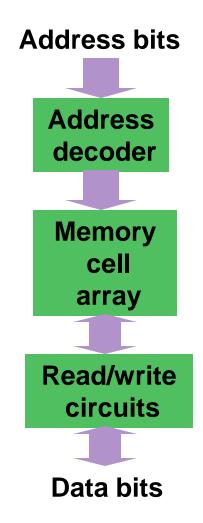

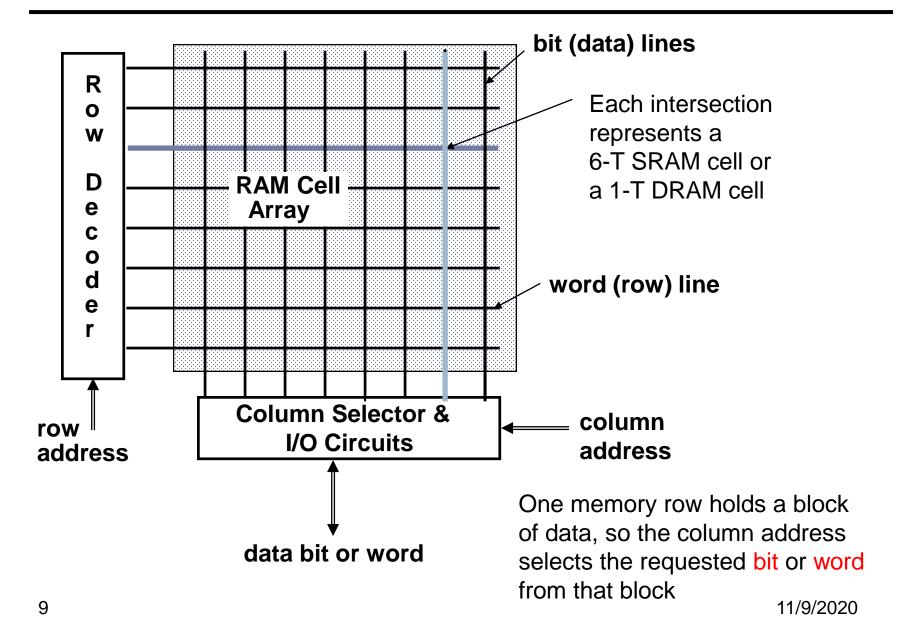

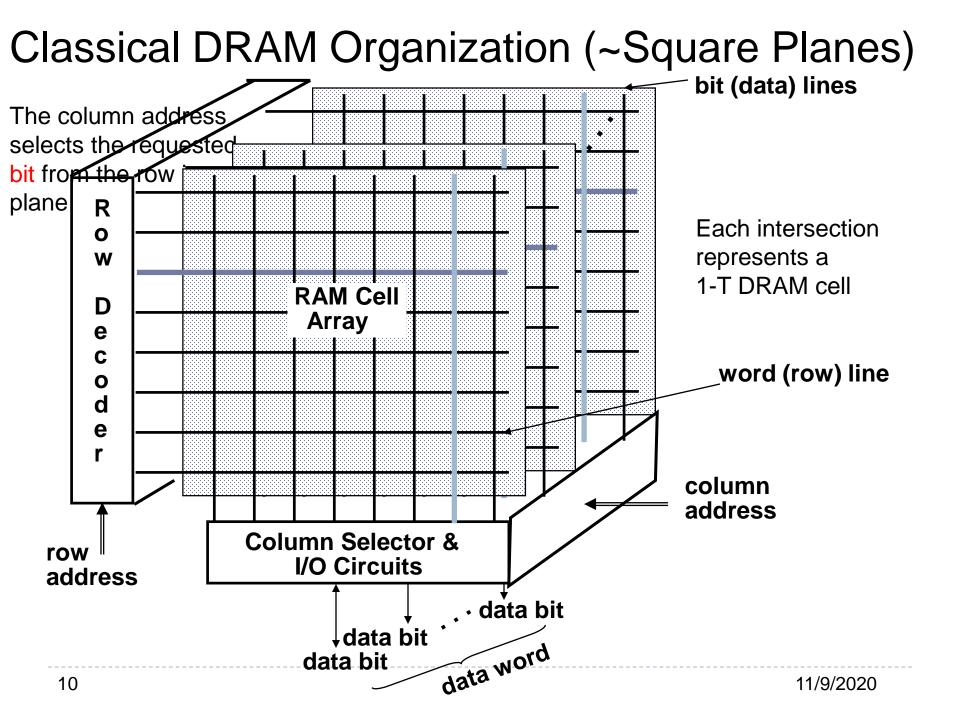

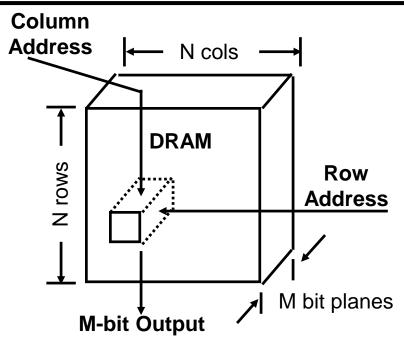

# Classical RAM Organization (~Square)

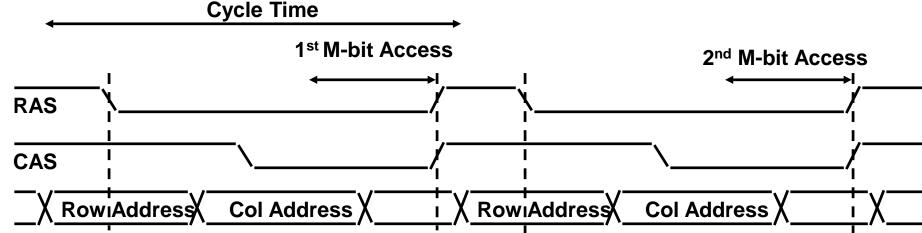

#### Classical DRAM Operation

- DRAM Organization:

- N rows x N column x M-bit

- Read or Write M-bit at a time

- Each M-bit access requires a RAS / CAS cycle

11

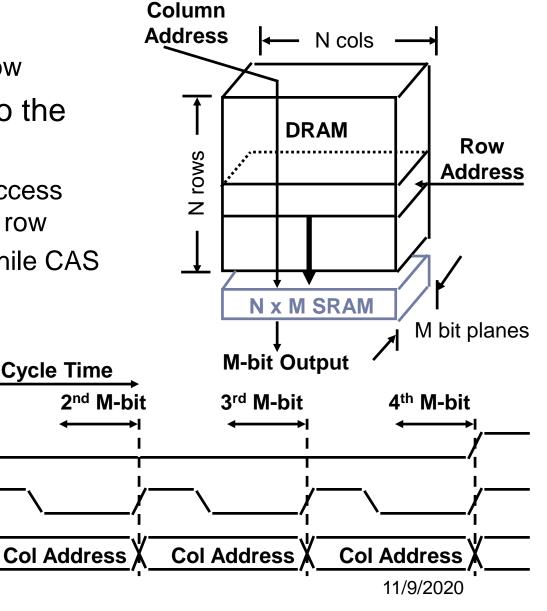

#### Page Mode DRAM Operation

- Page Mode DRAM

- N x M SRAM to save a row

- After a row is read into the SRAM "register"

- Only CAS is needed to access other M-bit words on that row

- RAS remains asserted while CAS is toggled

1<sup>st</sup> M-bit Access

Col Address X

**Cycle Time**

RowiAddress

**RAS**

CAS

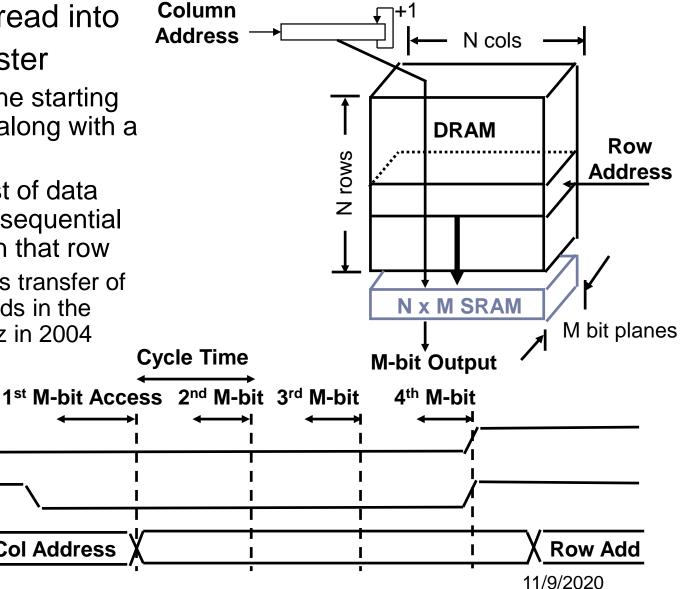

# Synchronous DRAM (SDRAM) Operation

- After a row is read into the SRAM register

- Inputs CAS as the starting "burst" address along with a burst length

- Transfers a burst of data from a series of sequential addresses within that row

- A clock controls transfer of successive words in the burst – 300MHz in 2004

XRow Address X Col Address

**RAS**

CAS

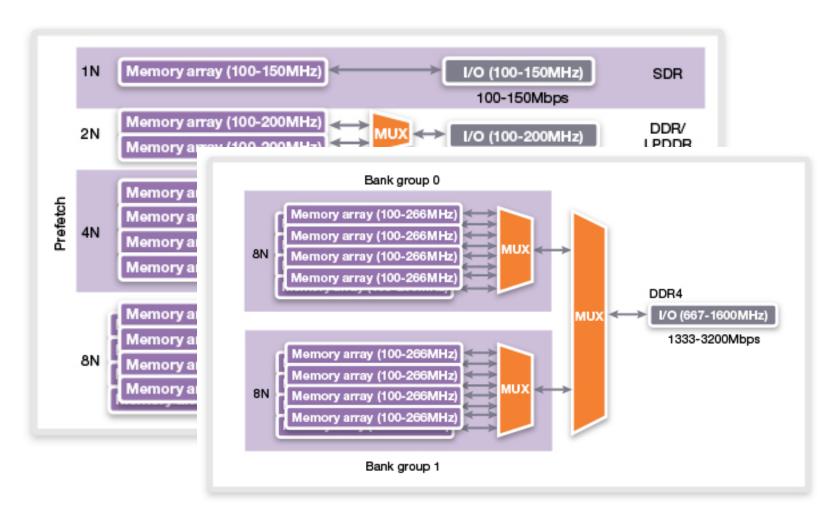

#### Other SDRAM Architectures

- Test 2 Friday Hav

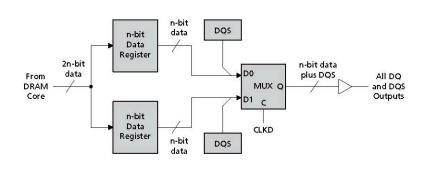

- Double Data Rate SDRAMs DDR-SDRAMs

- Double data rate because they transfer data on both the rising and falling edge of the clock

- Most widely used form of SDRAMs

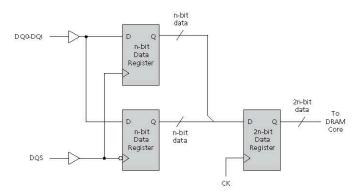

- For DDR memory, 2n prefetch architecture means

- > Internal bus width is twice of external bus width

- > Hence, internal column access freq can be half of external data rate

- For users, 2n prefetch means that data access occurs in pairs

- ➤ A single READ fetches two data words

- ➤ A single WRITE, two data words must be provided

Figure 1. Simplified Block Diagram of 2n-Prefetch READ

Figure 2. Simplified Block Diagram of 2n-Prefetch WRITE

#### Other SDRAM Architectures- Cont.

## Memory Synthesis

- Approaches:

- Random logic using flip-flops or latches

- Register files in data paths

- RAM standard components

- RAM compilers

- Computer "register files" are often just multi-port RAMs

- ARM CPU: 32-bit registers R0-R15 => 16 x 32 RAM

- MIPS CPU: 32-bit registers R0-R31 => 32 x 32 RAM

- Communications systems often use dual-port RAMs as transmit/receive buffers

- FIFO (first-in, first-out RAM)

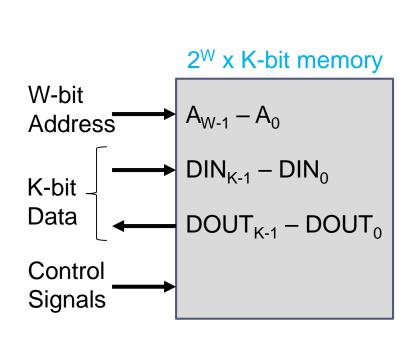

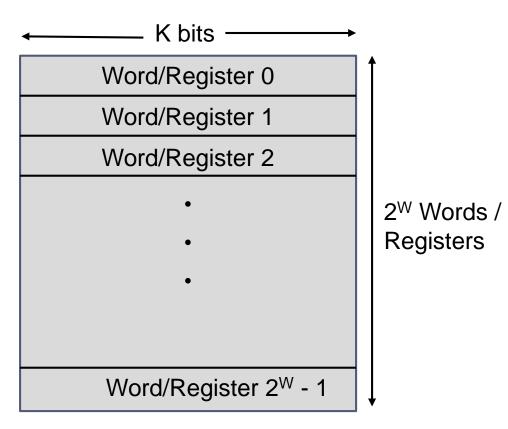

# Basic memory/register array

```

-- 2<sup>W</sup> x K-bit memory VHDL struture

signal MemArray: array (0 to 2**W – 1) of std_logic_vector(K-1 downto 0);

-- ARM register file is 16 32-bit registers

signal ARMregisterFile: array (0 to 15) of std_logic_vector(31 downto 0);

```

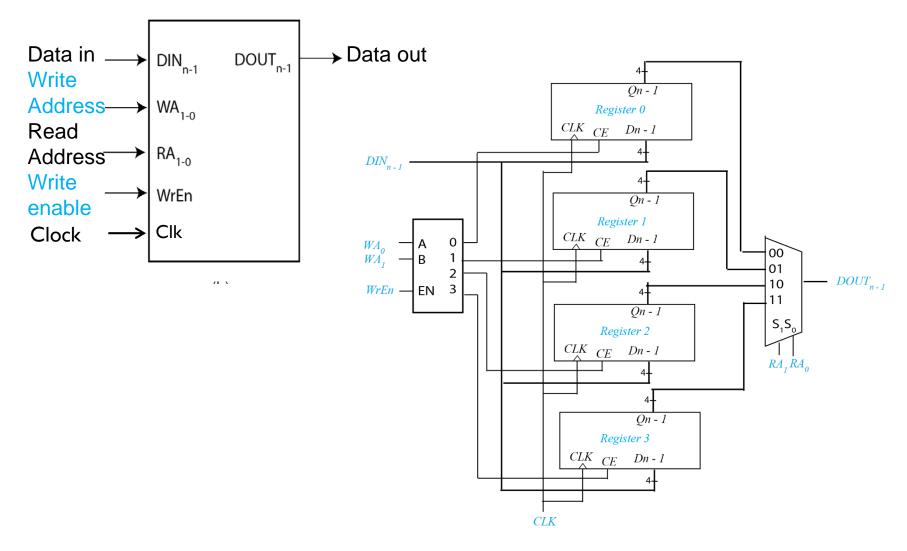

# Example: 4 x n-bit register file

#### Technology-independent RAM Models

-- N x K RAM is 2-dimensional array of N K-bit words library IEEE; **ADDR** use IEEE.std\_logic\_1164.all; DIN  $N \times K$ use IEEE.std\_numeric\_std.all; RAM DOUT WR entity RAM is generic (K: integer:=8; -- number of bits per word W: integer:=8); -- number of address bits; N = 2<sup>N</sup>W port ( in std\_logic; -- active high write enable WR: ADDR: in std\_logic\_vector (W-1 downto 0); -- RAM address in std\_logic\_vector (K-1 downto 0); -- write data DIN: DOUT: out std\_logic\_vector (K-1 downto 0)); -- read data end entity RAM;

11/9/2020

#### RAM Models in VHDL

```

architecture RAMBEHAVIOR of RAM is

subtype WORD is std_logic_vector ( K-1 downto 0);

-- define size of WORD

type MEMORY is array (0 to 2**W-1) of WORD;

-- define size of MEMORY

signal RAM256: MEMORY;

-- RAM256 as signal of type MEMORY

begin

process (WR, DIN, ADDR)

variable RAM_ADDR_IN: natural range 0 to 2**W-1; -- translate address to integer

begin

RAM_ADDR_IN := to_integer(UNSIGNED(ADDR));

-- convert address to integer

if (WR='1') then

-- write operation to RAM

RAM256 (RAM ADDR IN) <= DIN :

end if:

DOUT <= RAM256 (RAM ADDR IN);

-- continuous read operation

end process;

end architecture RAMBEHAVIOR;

Multi-port RAM (two parallel outputs):

DOUT1 <= RAM256(to_integer(UNSIGNED(ADDR1));

DOUT2 <= RAM256(to_integer(UNSIGNED(ADDR2));

```

#### Initialize RAM at start of simulation

```

process (WR, DIN, ADDR)

variable RAM_ADDR_IN: natural range 0 to 2**W-1; -- to translate address to integer

variable STARTUP: boolean := true;

-- temp variable for initialization

begin

if (STARTUP = true) then -- for initialization of RAM during start of simulation

RAM256 \le (0 \Rightarrow "00000101", --initializes first 4 locations in RAM

1 => "00110100", -- to specific values

2 => "00000110", -- all other locations in RAM are

3 => "00011000", -- initialized to all 0s

others => "00000000");

DOUT <= "XXXXXXXXX"; -- force undefined logic values on RAM output

STARTUP :=false; -- now this portion of process will only execute once

else

-- "Normal" RAM operations

```

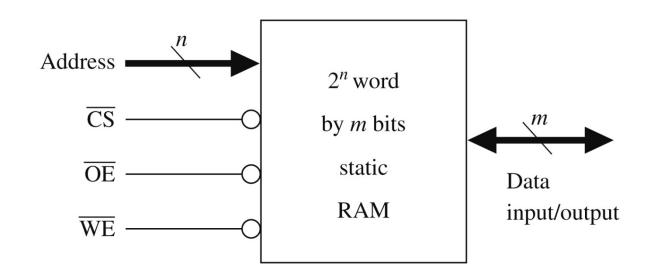

#### RAM with bidirectional data bus

FIGURE 8-14: Block Diagram of Static RAM

TABLE 8-7: Truth Table for Static RAM

| CS | ŌĒ | WE | Mode            | I/O pins |

|----|----|----|-----------------|----------|

| Н  | Χ  | X  | not selected    | high-Z   |

| L  | Н  | Н  | output disabled | high-Z   |

| L  | L  | Н  | read            | data out |

| L  | X  | L  | write           | data in  |

# Single-port distributed RAM

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std_logic_unsigned.all;

entity rams 04 is

clk: in std logic;

port (

64x16

we : in std logic;

LUT

a : in std_logic_vector(5 downto 0);

do

di : in std_logic_vector(15 downto 0);

RAM

we

do: out std_logic_vector(15 downto 0));

end rams_04;

clk

architecture syn of rams 04 is

type ram_type is array (63 downto 0) of std_logic_vector (15 downto 0);

signal RAM : ram_type;

begin

process (clk)

begin

if (clk'event and clk = '1') then

if (we = '1') then

RAM(conv_integer(a)) <= di;

end if:

end if:

end process:

do <= RAM(conv_integer(a));</pre>

end syn;

From Xilinx "Synthesis and Simulation

Design Guide"

```

#### FIGURE 6-18: Behavioral VHDL Code That Typically Infers LUT-Based Memory

```

library IEEE;

use IEEE.numeric_bit.all;

entity Memory is

port(Address: in unsigned(6 downto 0);

CLK, MemWrite: in bit;

Data_In: in unsigned(31 downto 0);

Data_Out: out unsigned(31 downto 0));

end Memory;

architecture Behavioral of Memory is

type RAM is array (0 to 127) of unsigned(31 downto 0);

signal DataMEM: RAM; -- no initial values

begin

process(CLK)

begin

if CLK'event and CLK = '1' then

if MemWrite = '1' then

DataMEM(to_integer(Address)) <= Data_In; -- Synchronous Write</pre>

end if:

end if;

end process;

Data_Out <= DataMEM(to_integer(Address)); -- Asynchronous Read</pre>

end Behavioral:

```

#### **Block RAM inferred**

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std logic unsigned.all;

addr

entity rams 01 is

di

clk: in std logic;

port (

we : in std logic;

do

64x16

en: in std logic;

addr : in std_logic_vector(5 downto 0);

BRAM

di: in std_logic_vector(15 downto 0);

we

do: out std_logic_vector(15 downto 0));

en

end rams_01;

clk

architecture syn of rams_01 is

type ram_type is array (63 downto 0) of std_logic_vector (15 downto \frac{1}{100}

signal RAM: ram type;

begin

process (clk)

begin

if clk'event and clk = '1' then

if en = '1' then

if we = '1' then

RAM(conv_integer(addr)) <= di;

end if:

do <= RAM(conv_integer(addr)); -- read-first operation</pre>

end if:

end if:

end process;

end syn;

From Xilinx "Synthesis and Simulation

Design Guide"

```

#### FIGURE 6-19: Behavioral VHDL Code That Typically Infers Dedicated Memory

```

library IEEE;

use IEEE.numeric_bit.all;

entity Memory is

port(Address: in unsigned(6 downto 0);

CLK, MemWrite: in bit;

Data In: in unsigned(31 downto 0);

Data Out: out unsigned(31 downto 0));

end Memory:

architecture Behavioral of Memory is

type RAM is array (0 to 127) of unsigned(31 downto 0);

signal DataMEM: RAM: -- no initial values

begin

process(CLK)

begin

if CLK'event and CLK = '1' then

if MemWrite = '1' then

DataMEM(to integer(Address)) <= Data In; -- Synchronous Write

end if:

Data Out <= DataMEM(to integer(Address)); -- Synchronous Read

end if:

end process:

end Behavioral;

```

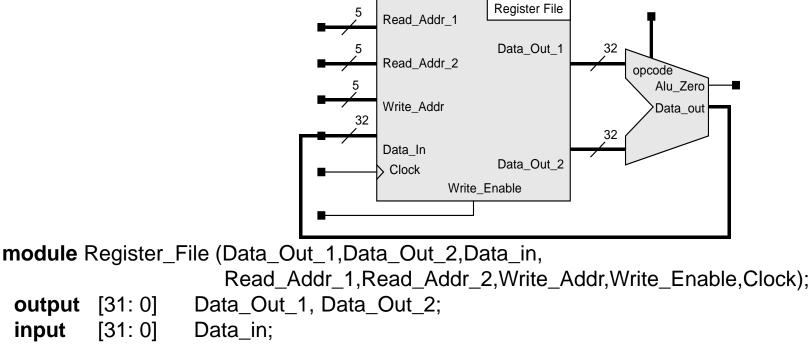

# Register File in Verilog

```

output [31: 0]

Data Out 1, Data Out 2:

input

[31: 0]

Data in:

input

[4: 0]

Read_Addr_1, Read_Addr_2, Write_Addr;

input

Write Enable, Clock:

[31: 0] Reg File [31: 0]; // 32bit x32 word memory declaration

reg

assign Data_Out_1 = Reg_File[Read_Addr_1];

assign Data_Out_2 = Reg_File[Read_Addr_2];

always @ (posedge Clock) begin

if (Write_Enable) Reg_File [Write_Addr] <= Data_in;</pre>

end

endmodule

```

# "Concept of Memory" in Verilog

- Memory

- Declaration an array of words

- E.g. reg [31:0] data\_out; // one 32-bit word

reg [31:0] Reg\_file [31:0]; // 32x32 bit word memory

- Verilog does not support 2-dimensional array

- However, a word in a Verilog memory can be addressed directly

E.g., Reg\_file [12]

- A cell bit in a word can also be addressed indirectly by first loading the word into a buffer register then addressing the bit of the word

E g Data out = Reg file [12]:

```

E.g. Data_out = Reg_file [12];

Data_out [1:0]

```

Decoder are synthesized automatically by synthesis tool in Reg\_file[] to decode the address which locates a specific register

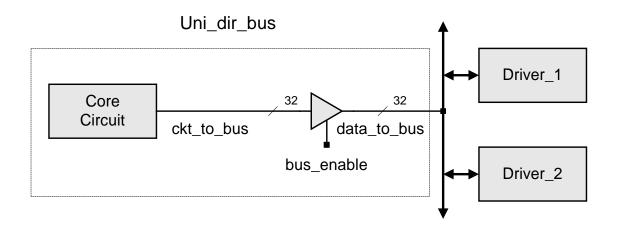

#### **Bus Interface**

#### Unidirectional Bus

Michael D. Ciletti, Advanced digital design with the Verilog HDL.

#### Bus Interface

**Bidirectional Bus**

```

module Bi_dir_bus (data_to_from_bus, send_data, rcv_data);

inout

[31: 0] data_to_from_bus;

Input

send data, rcv data;

wire

[31: 0] ckt to bus;

wire

[31: 0] data to from bus, data from bus;

assign data_from_bus = (rcv_data)? data_to_from_bus: 32'bz;

assign data_to_from_bus = (send_data)? ckt_to_bus: data_to_from_bus;

// Behavior using data_from_bus and generating

// ckt_to_bus goes here

endmodule

```

30