### WHAT IS TIMS ?

TIMS is a Telecommunications Instructional Modelling System. It models telecommunication systems.

Text books on telecommunications abound with block diagrams. These diagrams illustrate the subject being discussed by the author. Generally they are small sub-systems of a larger system. Their behaviour is described by the author with the help of mathematical equations, and with drawings or photographs of the signal waveforms expected to be present.

TIMS brings alive the block diagram of the text book with a working model, recreating the waveforms on an oscilloscope.

How can TIMS be expected to accommodate such a large number of models ?

There may be hundreds of block diagrams in a text book, but only a relatively few individual block *types*. These block diagrams achieve their individuality because of the many ways a relatively few element *types* can be connected in different *combinations*.

TIMS contains a collection of these block types, or *modules*, and there are very few block diagrams which it cannot model.

### **PURPOSE OF TIMS**

TIMS can support courses in Telecommunications at all levels - from Technical Colleges through to graduate degree courses at Universities.

This text is directed towards using TIMS as support for a course given at any level of teaching.

Most early experiments are concerned with illustrating a small part of a larger system. Two or more of these sub-systems can be combined to build up a larger system.

The list of possible experiments is limitless. Each instructor will have his or her own favourite collection - some of them are sure to be found herein.

Naturally, for a full appreciation of the phenomena being investigated, there is no limit to the depth of mathematical analysis that can be undertaken. But most experiments can be performed successfully with little or no mathematical support. It is up to the instructor to decide the level of understanding that is required.

# **EXPERIMENT AIMS**

The digital experiments in this Volume build on those covered in Volume D1. It is advantageous to have completed as many of those as possible.

As before, the experiments have been written with the idea that each model examined could eventually become part of a larger telecommunications system, the aim of this large system being to transmit a *message* from input to output. The origin of this message, for the digital experiments in Volumes D1 and D2, is generally a pseudo random binary sequence. For the analog experiments, in Volumes A1 and A2, it would ultimately be speech. But for test and measurement purposes a sine wave, or perhaps two sinewaves (as in the two-tone test signal) are generally substituted.

The experiments are designed to be completed in about two hours, with say one hour of preparation prior to the laboratory session.

The four Volumes of *Communication Systems Modelling with TIMS* are:

- A1 Fundamental Analog Experiments

- A2 Further & Advanced Analog Experiments

- D1 Fundamental Digital Experiments

- D2 Further & Advanced Digital Experiments

# Contents

| BER measurement in the noisy channel1 |

|---------------------------------------|

| BER instrumentation macro model19     |

| Bit clock regeneration                |

| Carrier acquisition                   |

| DPSK - carrier acquisition and BER    |

| PCM TDM                               |

| Block coding & decoding               |

| Block coding and coding gain          |

| Convolutional coding                  |

| TCM - trellis coding                  |

| PPM and PWM                           |

| QAM and 4-PSK                         |

| Multi-level QAM & PSK                 |

| Spread spectrum - DSSS and CDMA 123   |

| Digital utility sub-systems           |

|                                       |

| Appendix - Advanced Modules           |

# BER MEASUREMENT IN THE NOISY CHANNEL

| PREPARATION                              | 2  |

|------------------------------------------|----|

| overview                                 | 2  |

| the basic system                         |    |

| a more detailed description              |    |

| theoretical predictions                  | 5  |

| EXPERIMENT                               | 6  |

| the ERROR COUNTING UTILITIES module      | 6  |

| modelling the transmission system        | 7  |

| 1.0: the transmitter                     | 7  |

| 2.0: the channel model                   | 8  |

| 3.0: the receiver                        | 8  |

| 4.0: the BER measurement instrumentation | 9  |

| 5.0 error counting with noise            | 11 |

| preparation                              | 11 |

| adding noise - principle                 |    |

| adding noise - practice                  |    |

| 6.0 DC threshold adjustment              |    |

| method #1                                | 14 |

| method #2                                | 14 |

| measuring the BER                        | 14 |

| role of the filter                       | 15 |

| conclusion                               | 15 |

| TUTORIAL QUESTIONS                       | 15 |

| APPENDIX                                 | 17 |

| the ERROR COUNTING UTILITIES module      | 17 |

| X-OR gate                                | 17 |

| gate timing pulse                        | 17 |

|                                          |    |

# BER MEASUREMENT IN THE NOISY CHANNEL

**ACHIEVEMENTS:** ability to set up a digital communications system over a noisy, bandlimited channel, with provision for line-coding, and instrumentation for BER measurements. This system will be used for many future experiments.

**PREREQUISITES:** completion of the first five experiments in Volume D1 would be an advantage, especially those entitled **The noisy channel model**, and **Detection with the DECISION MAKER**.

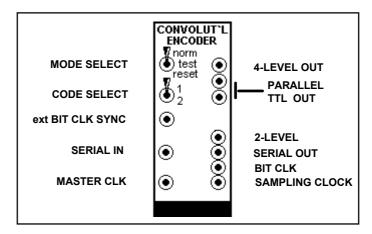

**EXTRA MODULES:** LINE-CODE ENCODER, LINE-CODE DECODER, DECISION MAKER, NOISE GENERATOR, ERROR COUNTING UTILITIES, WIDEBAND TRUE RMS METER, an extra SEQUENCE GENERATOR, BASEBAND CHANNEL FILTERS.

# PREPARATION

### overview

This experiment serves as an introduction to bit error rate (BER) measurement. It models a digital communication system transmitting binary data over a noisy, bandlimited channel. A complete instrumentation setup is included, that allows measurement of BER as a function of signal-to-noise ratio (SNR).

Many variations of this system are possible, and the measurement of the performance of each of these can form the subject of separate experiments.

In this first experiment the system is configured in its most elementary form.

Other experiments can add different forms of message coding, line coding, different channel characteristics, bit clock regeneration, and so forth.

# the basic system

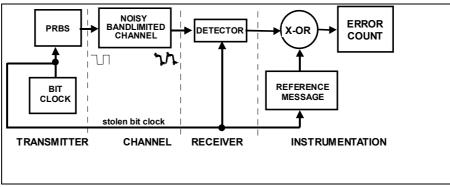

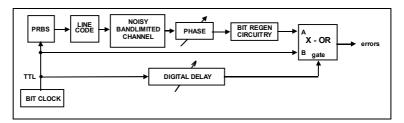

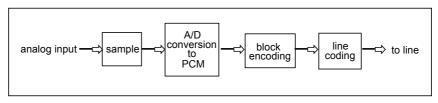

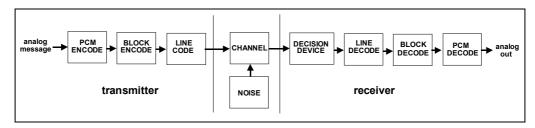

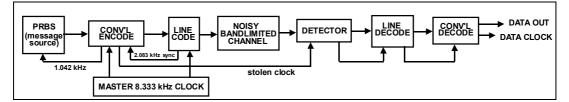

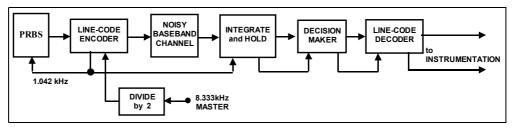

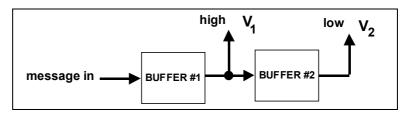

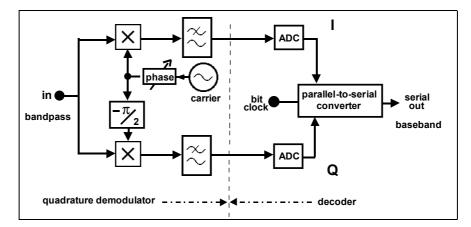

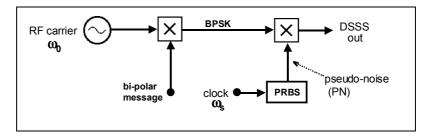

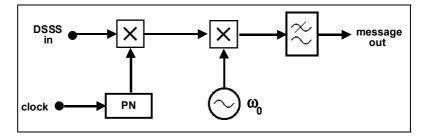

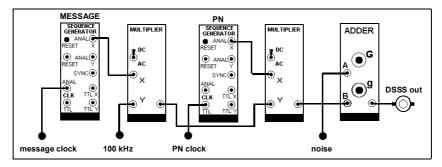

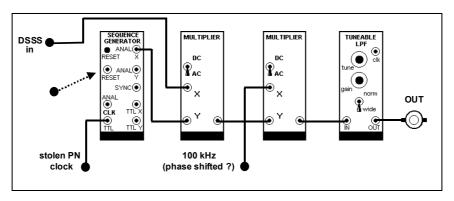

A simplified block diagram of the basic system is shown in Figure 1 below.

Figure 1: block diagram of system

The system can be divided into four sections:

#### the transmitter

At the *transmitter* is the originating message sequence, from a pseudo random binary sequence (PRBS) generator, driven by a system bit clock.

#### the channel

The *channel* has provision for changing its bandlimiting characteristic, and the addition of noise or other sources of interference.

#### the receiver

The *receiver* (detector) regenerates the transmitted (message) sequence. It uses a stolen bit clock.

#### the BER instrumentation

The instrumentation consists of the following elements:

- 1. a sequence generator identical to that used at the transmitter. It is clocked by the system bit clock (stolen, in this case). This sequence becomes the reference against which to compare the received sequence.

- 2. a means of aligning the instrumentation sequence generator with the received sequence. A *sliding window correlator* is used. This was introduced in the experiment entitled *Detection with the DECISION MAKER* in Volume D1.

- 3. a means of measuring the errors, after alignment. The error signal comes from an X-OR gate. There is one pulse per error. The counter counts these pulses, over a period set by a gate, which may be left open for a known number of bit clock periods.

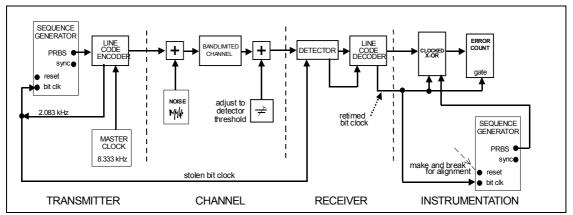

## a more detailed description

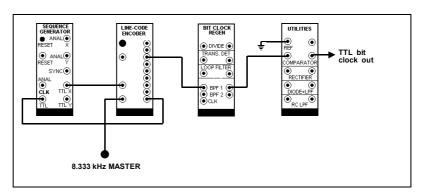

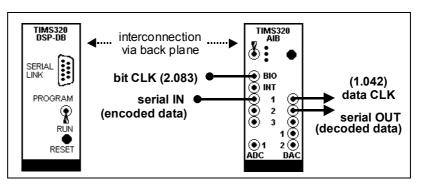

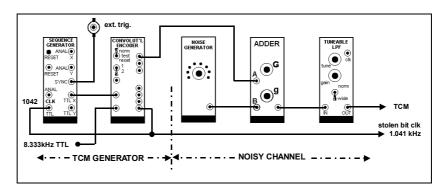

Having examined the overall operation of the basic system, and gained an idea of the purpose of each element, we proceed now to show more of the specifics you will need when modelling with TIMS.

So Figure 1 has been expanded into Figure 2 below.

The detector is the DECISION MAKER module, introduced in the experiment entitled *Detection with the DECISION MAKER*.

The LINE-CODE ENCODER and LINE-CODE DECODER modules were introduced in the experiment entitled *Line coding* in Volume D1.

Figure 2: block diagram of system in more detail

The extra detail in Figure 2 includes:

- 1. provision for transforming the data before transmission, using any one of a number of line codes. In this experiment we use the NRZ-L code which provides level shift and amplitude scaling, to suit the analog channel.

- 2. bit clock generation. Because the line coder requires quarter-bit-period timing information, it is driven by a *master clock* at four-times the bit-clock rate. The timing information is obtained by dividing the master clock by four (within the LINE-CODE ENCODER). This divided-by-four version of the *master clock* becomes the *system bit clock*.

- 3. provision for adding noise to the channel via the adder on the *input* side of the bandlimiting channel.

- 4. inclusion of an ADDER on the output side of the channel. This restores the polarity change introduced by the input ADDER (for line codes which are polarity sensitive). It also provides an opportunity to fine-trim the DC level to match the threshold of the DECISION MAKER.

- 5. a decoder for the line code.

- 6. instrumentation for SNR adjustment (not shown) and BER measurement.

# theoretical predictions

Bit error probability  $(P_B)$  is a function of  $E_n/N_o$ . For matched filter reception of bipolar baseband signalling it has been shown that:

$$P_B = \mathcal{Q}\left(\sqrt{\frac{2E_b}{N_o}}\right) \qquad \qquad \dots \dots 1$$

The symbols are defined in the Chapter entitled *BER instrumentation macro module* in this Volume

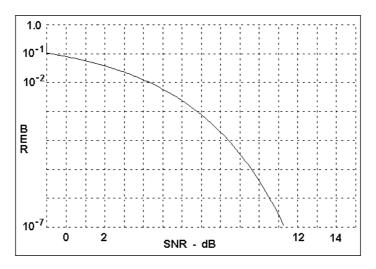

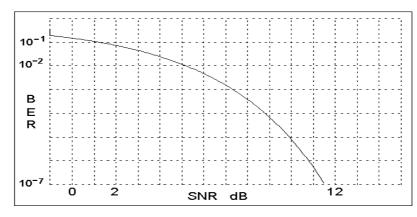

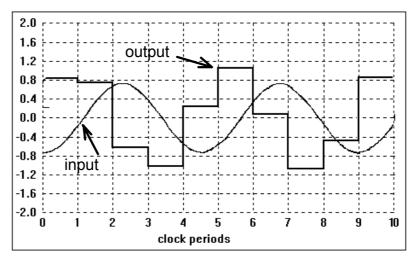

You will measure not  $P_B$ , but BER; and not  $E_n/N_o$ , but SNR. Figure 3 shows theoretical predictions, based on eqn(1) above.

Figure 3 theoretical expectations - BER versus SNR (for bi-polar signalling)

# EXPERIMENT

Familiarity with the setting up of a transmitter, receiver, and noisy channel, using a stolen clock for bit clock synchronization, and the sliding window correlator for sequence alignment, is assumed.

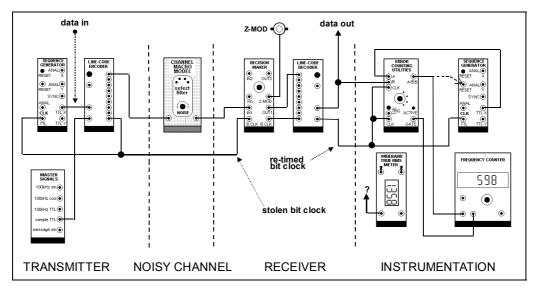

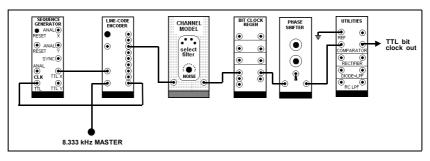

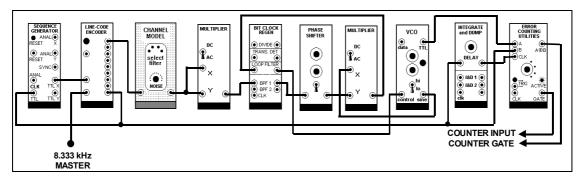

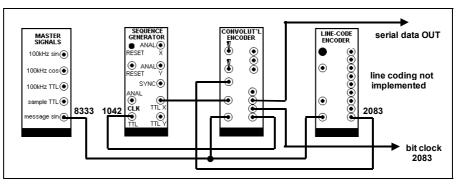

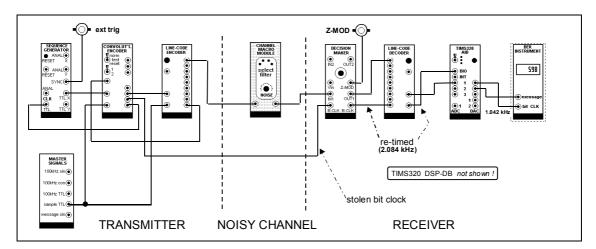

The system under examination, the principle of which is illustrated in block diagram form in Figure 1, is shown modelled by the patching diagram of Figure 4 on the next page. Within that diagram is included the macro CHANNEL MODEL module, and the BER INSTRUMENTATION macro module.

The macro CHANNEL MODEL module was introduced in the experiment entitled *The noisy channel model* in Volume D1, which you should already have completed.

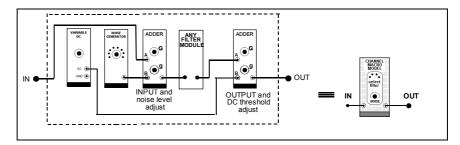

As a reminder, details of the macro CHANNEL MODEL module are reproduced in Figure 4 below.

Figure 4: details of the macro CHANNEL MODEL module

Remember that, during testing, and afterwards, the oscilloscope triggering comes from:

- the SYNC output from the transmitter SEQUENCE GENERATOR for snapshots

- the bit clock for eye patterns.

# the ERROR COUNTING UTILITIES module

This is the first time the pulse counting capabilities of the ERROR COUNTING UTILITIES module have been used. A complete description of the characteristics and behaviour of the module can be obtained from the *TIMS Advanced Modules User Manual*.

A condensed description of its function is given in the Chapter entitled *Digital utility sub-systems* in this Volume, under the two headings *Timed Pulse* (for the counting function) and *Exclusive-OR*.

# modelling the transmission system

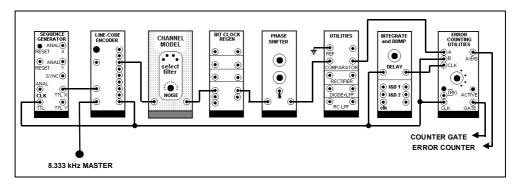

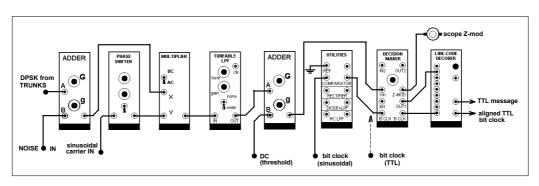

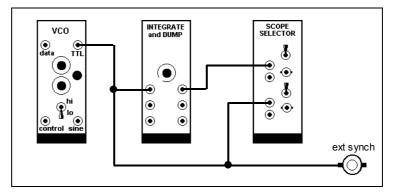

The system to be modelled is shown in Figure 5. It will be patched up systematically, section by section, according to the scheme detailed below. It has not been cluttered by showing oscilloscope connections. You should set up the SCOPE SELECTOR for maximum usage of the facility for toggling between the A and B options for each channel.

**Figure 5: the TIMS model of Figure 2**

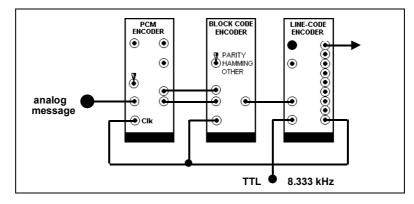

### 1.0: the transmitter

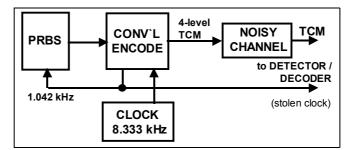

- **T1.1** patch the transmitter according to Figure 5, from a SEQUENCE GENERATOR (set to a short sequence - both toggles of SW2, on circuit board, UP), a LINE-CODE ENCODER (using NRZ-L), and the MASTER SIGNALS module. Note that the LINE-CODE ENCODER accepts the **master clock**, which is the 8.333 kHz TTL 'sample clock' from the MASTER SIGNALS module, and divides it by four to produce the 2.083 kHz **system bit clock** for the SEQUENCE GENERATOR.

- **T1.2** press the reset on the LINE-CODE ENCODER. Check on CH1-A that a short TTL sequence has been generated by the SEQUENCE GENERATOR.

- **T1.3** simultaneously with the previous observation on CH1-A, check the NRZ-L output of the LINE-CODE ENCODER on CH2-A. Relative to the TTL on CH1-A it will be delayed half a bit period. This is the signal being transmitted to the channel. Confirm the code format.

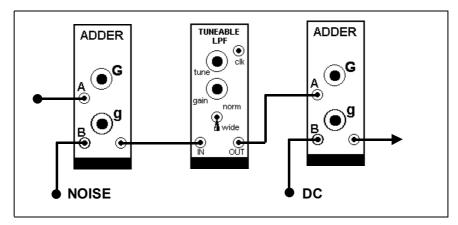

#### 2.0: the channel model

The macro CHANNEL MODEL module is shown modelled in Figure 4.

- **T2.1** patch up the channel according to Figure 4 and insert it into the position shown in Figure 5.

- **T2.2** set the front panel attenuator of the NOISE GENERATOR to maximum output; but reduce the channel noise to zero by rotating the INPUT ADDER gain control 'g' fully anti-clockwise.

- **T2.3** adjust the amplitude of the signal **into** the BASEBAND CHANNEL FILTERS module to near the TIMS ANALOG REFERENCE LEVEL (say, 2 volt peak-to-peak) with the INPUT ADDER gain control '**G**'. This level <u>will</u> <u>need resetting</u> when noise is added.

- *T2.4* select channel #3 of the BASEBAND CHANNEL FILTERS module.

- **T2.5** set the gain of the DC threshold adjustment path through the OUTPUT ADDER to zero.

- **T2.6** adjust the amplitude of the signal **out of** the CHANNEL MODEL to, say, 2 volt peak-to-peak with the OUTPUT ADDER gain control '**G**'. The gain through the channel is now unity.

- **T2.7** confirm that the signal at the OUTPUT ADDER, although of different shape, and further delayed, is clearly related to the input sequence.

When tracing the sequence through the system, notice that there is a polarity inversion introduced by the INPUT ADDER of the channel, and a second inversion introduced by the OUTPUT ADDER.

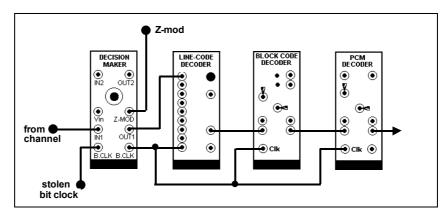

#### 3.0: the receiver

The receiver consists of the DECISION MAKER and LINE-CODE DECODER modules.

- **T3.1** before plugging in the DECISION MAKER:

- *a)* switch the on-board switch SW2 to 'IN' (DECISION POINT can now be adjusted with the front panel control).

- *b)* select the expected line code with the on-board rotary switch SW1 (upper rear of board). For this experiment it is NRZ-L.

- **T3.2** patch up the DECISION MAKER, including the Z-MOD output to the oscilloscope. It is assumed that the Z-MOD adjustments have been made on the circuit board to suit your oscilloscope <sup>1</sup>.

- **T3.3** trigger the oscilloscope from the bit clock, and obtain an eye pattern at the channel output. Adjust the sampling instant, with the DECISION MAKER front panel control, to the centre of the eye. Remember that some fine adjustment of the intensity control of the oscilloscope will probably be necessary to easily identify the bright spot at the sampling instant.

- **T3.4** trigger the oscilloscope from the SYNC output of the transmitter SEQUENCE GENERATOR. Check that the reconstructed 'analog' output from the DECISION MAKER is a delayed version of, but otherwise the same shape as, that at the channel input.

- **T3.5** refer to the DECISION MAKER in the **TIMS User Manual** for threshold level information. This varies according to the code in use. For the NRZ-L code the threshold is approximately 25 mV. Thus the input signal amplitude must either swamp any possible DC threshold, or, if small, must be adjusted to straddle it. There is provision in the model (the OUTPUT ADDER) for this; it will be checked in the next Section. For now confirm that the output waveform is centred approximately about zero volts.

- **T3.6** patch up the LINE-CODE DECODER, selecting the NRZ-L output.

- **T3.7** press the reset on the LINE-CODE DECODER. Check that the TTL output sequence is identical, except for a delay, with that at the transmitter SEQUENCE GENERATOR output.

Do not proceed unless these two TTL signals are identical !

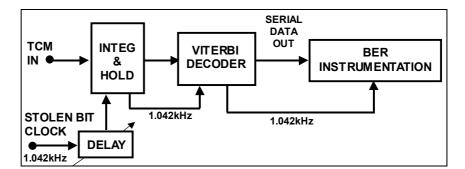

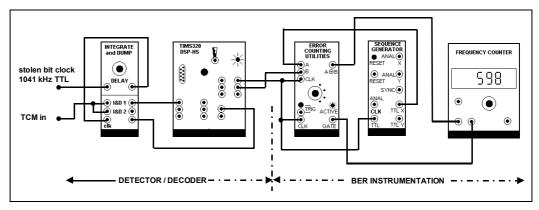

### 4.0: the BER measurement instrumentation

The transmission system is now fully set up. You will now proceed to verify its overall operation.

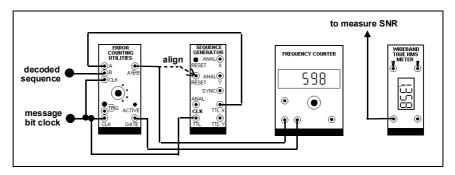

The BER measurement instrumentation system is used to generate an *identical* sequence to that transmitted, and *aligned* with that from the receiver detector. These two sequences will be compared, bit by bit, and any disagreements *counted*. The count is made over a pre-determined number of bit clock periods, and so the bit error *rate* (BER) may be calculated.

You will record the BER for various levels of noise, and compare with theoretical expectations.

<sup>&</sup>lt;sup>1</sup> refer to the experiment entitled *Detection with the DECISION MAKER*. in Volume D1

- **T4.1** patch up according to Figure 5. Note the instrumentation (receiver) SEQUENCE GENERATOR uses the LINE-CODE DECODER strobe as its bit clock. Trigger the oscilloscope for a snapshot. Check that there is a short sequence coming from the instrumentation SEQUENCE GENERATOR output.

- **T4.2** see the Appendix to this experiment for a short description of the ERROR COUNTING UTILITIES module, <u>including on-board jumper and</u> <u>switch settings</u>. Plug it in. Check that the line from the X-OR output to the instrumentation SEQUENCE GENERATOR RESET is **open**.

- *T4.3* observe the two inputs to the X-OR gate simultaneously. It is unlikely that they are aligned, but they should be synchronized.

Your good work is about to be rewarded with the sight of the two sequences snapping into alignment.

**T4.4** momentarily close the line from the X-OR output to the instrumentation SEQUENCE GENERATOR RESET. Confirm that the two sequences, already <u>synchronized</u>, are now <u>aligned</u>.

If you want to see the sliding window correlator at work again, press the reset on the instrumentation SEQUENCE GENERATOR, and alignment will be lost. Re-align by repeating the last Task.

- **T4.5** set the FREQUENCY COUNTER to its COUNT mode, and patch it into the system, complete with the gate signal from the ERROR COUNTING UTILITIES module.

- **T4.6** switch the gate of the ERROR COUNTING UTILITIES, with the PULSE COUNT switch, to be active for  $10^5$  bit clock periods. Make a mental calculation to estimate how long that will be !

*T4.7* to make an error count:

- *a)* reset the FREQUENCY COUNTER.

- *b)* start the error count by pressing the TRIG button of the ERROR COUNTING UTILITIES module.

The 'active' LED on the ERROR COUNTING UTILITIES module will light, and remain alight until 90% of the count is completed, when it will blink before finally extinguishing, indicating the count has concluded. *warning*: every time a count is initiated *one count* will be recorded immediately. This is a 'confidence count', to reassure you the system is active, especially for those cases when the actual errors are minimal. It does *not* represent an error, and *should always be subtracted from the final count*.

Despite the above single confidence-count you may wish to make a further check of the error counting facility, before using noise.

**T4.8** if the ERROR COUNTING UTILITIES GATE is still open press the instrumentation SEQUENCE GENERATOR reset button (else press the TRIG to open the GATE). The sequences should now be out of alignment.

The counter will start counting (and continue counting) errors until the GATE shuts. It will record a count of between 2 and  $10^n$  (with the PULSE COUNT switch set to make  $10^n$  counts). You will record a different count each time this is repeated. Why would this be ?

#### well done !

You have just completed a major setting-up procedure. If it was achieved without any problems you are to be congratulated ! Although TIMS itself will behave reliably, it is easy to make patching errors, and their discovery and rectification is all part of the learning process.

You are now almost ready to sit back and let TIMS do the measurements for you.

### 5.0 error counting with noise

#### preparation

- **T5.1** increase the message sequence length of <u>both</u> SEQUENCE GENERATOR modules (both toggles of SW2 DOWN). See Tutorial Question Q2.

- **T5.2** re-establish sequence alignment by pressing all the reset buttons, in order input to output, then momentarily connect the X-OR output to the instrumentation SEQUENCE GENERATOR RESET input.

#### adding noise - principle

It is now time to add the noise to the signal. Noise must be introduced *before* bandlimiting, since the channel bandlimiting filters are required to bandlimit the noise as well.

The noise from the NOISE GENERATOR is wideband. Its peak amplitude must not overload an analog module, so its output has been restricted to 4 volt peak-to-peak (the TIMS ANALOG REFERENCE LEVEL). As soon as it is bandlimited, this amplitude is reduced. Amplification cannot be used to bring it up to a convenient level until *after* bandlimiting. But by this time the signal has been added, so that is not possible.

So the only way to obtain a small signal-to-noise ratio (relatively high noise) is to *reduce* the signal level. This is done with the INPUT ADDER.

To set the noise level:

- a) remove the signal from the channel input

- b) add as much noise as is available, to implement the worst SNR possible, by maximising the gain through the INPUT ADDER, and setting the attenuator of the NOISE GENERATOR for maximum noise output. The SNR can later be increased less noise with this attenuator.

- c) measure the noise level into the DECISION MAKER with the WIDEBAND TRUE RMS METER. Then remove the noise, replace the signal, and adjust it to the same level.

- d) replace the noise. The SNR is 0 dB.

The system is now set up for the worst conditions under which measurements are to be made. From now on the SNR will be improved, in *calibrated* steps of the NOISE GENERATOR attenuator, and BER measurements recorded.

The above steps will now be implemented.

### adding noise - practice

- **T5.3** patch both the oscilloscope and the WIDEBAND TRUE RMS METER to observe the signal at the **output** of the channel.

- **T5.4** reduce the signal amplitude to zero with the 'G' gain control of the INPUT ADDER.

- **T5.5** set the attenuator of the NOISE GENERATOR for maximum output. Increase the noise level **into** the channel, with the INPUT ADDER, to maximum. **Record the reading of the rms meter (N volt rms amplitude)**.

- **T5.6** remove the noise by unplugging the patch cord from the INPUT ADDER.

- **T5.7** introduce some signal with the 'G' control of the channel INPUT ADDER, until the rms meter is reading the same as the previous noise reading. **Record this reading (S volt rms amplitude)**.

- **T5.8** replace the noise. Do <u>not</u> disturb the INPUT ADDER gain settings from now on !

- **T5.9** check the signal level at the channel output. Use the '**G**' gain control of the OUTPUT ADDER to raise the input level to the DECISION MAKER to the TIMS ANALOG REFERENCE LEVEL (4 V peak-to-peak is allowable, although there may be insufficient gain in the ADDER).

The SNR is now set up to a reference value

$$10\log_{10}\left|\frac{S^2}{N^2}\right| dB$$

and this will be 0 dB. However you may have your own reasons for selecting some other ratio, but it needs to result in many errors. From now on you can only *reduce* the noise, using the calibrated attenuator of the NOISE GENERATOR. This will *increase* the SNR, which will in turn *reduce* the error rate.

*warning*: *if alignment is ever lost the noise must be removed before attempting re-alignment !*

**T5.10** set the SNR to, say, 10 dB, and set the decision instant with the aid of an eye pattern.

### 6.0 DC threshold adjustment

The effect of any DC threshold of the DECISION MAKER must be offset with DC introduced by the OUTPUT ADDER.

Two methods are suggested.

- 1. after setting up as above, add a small DC to the signal from the channel. If the error count can be reduced then adjust for the smallest count.

- 2. set the DC output from the channel to +25 mV. This is the threshold level of the DECISION MAKER in NRZ-L mode. Recall the measurement made in this regard in the experiment entitled *Detection with the DECISION MAKER* in Volume D1.

See Tutorial Question Q3.

Now implement one or the other method of threshold adjustment.

#### method #1

- **T6.1** set the PULSE COUNT on the DECISION MAKER to  $10^5$  and press the TRIG button. Adjust the noise level with the attenuator so that errors are accumulating at about 10 per second (watch the second last digit).

- **T6.2** rotate the VARIABLE DC level about  $45^{\circ}$  anti-clockwise. Advance the 'g' control of the OUTPUT ADDER about  $20^{\circ}$ . The error rate should increase.

- **T6.3** slowly reduce the DC offset voltage magnitude (rotate the VARIABLE DC control clockwise towards zero). The error rate should slowly reduce, then increase. Return to the lowest rate and stay there. This is an important adjustment. It takes some practice. At all times set the error rate (with the noise source attenuator) so it is about 10 errors per second. Concentrate on the second last, and then the last digit, as the minimum is approached.

#### method #2

**T6.4** remove both inputs from the INPUT ADDER. Using both the VARIABLE DC control and the OUTPUT ADDER 'g' control, set the DC level at the input to the DECISION MAKER +25 mV (use the WIDEBAND TRUE RMS METER). Replace the inputs to the INPUT ADDER.

## measuring the BER

Everything is now set up for some serious measurements. It is assumed that:

- both SEQUENCE GENERATORS are set for long sequences (both toggles of the on-board switch SW2 are DOWN).

- line code NRZ-L has been patched (for *this* experiment) on the LINE-CODE ENCODER and LINE-CODE DECODER.

- line code NRZ-L has been selected with SW1 on the DECISION MAKER board.

- all reset button have been pushed (in turn from input to output).

- levels throughout the system have been set correctly (typically with SNR = 0 dB with max noise from the NOISE GENERATOR).

- DC threshold at the DECISION MAKER has been accounted for.

- signal into the DECISION MAKER is ideally at the TIMS ANALOG REFERENCE LEVEL (but probably considerably lower with the model of Figure 4).

- the DECISION POINT of the DECISION MAKER has been set up, using an eye pattern (with 'moderate' noise present say an SNR of 10 dB).

- the SEQUENCE GENERATOR at the receiver has been aligned with the incoming sequence (carried out with no noise present a high SNR).

- conditions for a known (reference) SNR are recorded.

- channel bandwidth is recorded (eg, which filter of the BASEBAND CHANNEL FILTERS module is in use ).

- **T6.5** measure BER according to the procedure in Task T4.7. Record the measurement, and the conditions under which it was made. Compare results with counts over short and long periods.

- **T6.6** decrease the noise level by one increment of the NOISE GENERATOR front panel attenuator. Go to the previous Task. Loop as many times as appropriate.

- T6.7 plot BER versus SNR. Relate your results to expectations.

### role of the filter

The characteristics of the filter will influence the result. The theoretical results assume an 'ideal' filter. We do not have that.

## conclusion

Future experiments will use this system configuration to measure BER under different conditions - for example, with the addition of error control coding, bit clock regeneration, and so on.

It is important, then, that you familiarize yourself with the setting up procedures of the basic system which was the subject of this experiment.

# **TUTORIAL QUESTIONS**

Q1 once sequence alignment is attained, the sliding window correlator is disabled. Explain why alignment is not lost even if the noise level is raised until the BER increases to unacceptably high levels.

Q2 why were you advised to use a long sequence when counting errors?

*Q3* explain the principle of what you were doing when adjusting the DC at the input to the DECISION MAKER.

# **APPENDIX**

# **ERROR COUNTING UTILITIES module**

A full description of this module is available in the *TIMS Advanced Module User Manual*. This should be <u>essential reading</u> before the module is used.

Before use it is necessary to check the settings of the on-board switches SW1 and SW2, and the jumper J1.

Briefly, the module consists of two sub-systems:

### X-OR gate

This has two modes:

- 1. *pulse mode:* with a clock signal connected. Acts as a gated sub-system. Somewhere near the middle of each clock pulse it makes an X-OR decision regarding the two TTL inputs. Its output is a TTL HI if they are different, otherwise a LO. In the present application it compares each bit of the regenerated received signal with a reference generator. Differences - which represent errors - are counted by the FREQUENCY COUNTER in COUNT mode.

- 2. *normal mode*: with no clock input

#### gate timing pulse

This clocked sub-system, on receipt of a trigger pulse - manual or electronic - outputs a pulse of length (number of clock periods) determined by the front panel switch PULSE COUNT, the toggles of the on-board switch SW2, and jumper J1.

In this experiment the trigger pulse is initiated by the front panel TRIG push button.

Th GATE output pulse (a LO, selected by toggle 2 of the on-board switch SW1) is used to activate the FREQUENCY COUNTER, in COUNT mode.

### on-board settings for this experiment

| switch/jumper | toggle   | position      | comments                |

|---------------|----------|---------------|-------------------------|

| J1            |          | NORM          |                         |

| SW1           | 1 - TRIG | HI - to left  | suits press button      |

| SW1           | 2 - GATE | LO - to right | counter activated on LO |

| SW2           | 1        | ON - to right | PULSE COUNT switch      |

| SW2           | 2        | ON - to right | settings times unity    |

# BER INSTRUMENTATION MACRO MODULE

#### **ADVANCED MODULES:** ERROR COUNTING UTILITIES, WIDEBAND TRUE RMS METER. Both the system being measured **and** this macro module require a SEQUENCE GENERATOR.

## introduction

Bit error rate (BER) measurement techniques were first introduced in the experiment entitled *BER in the noisy channel* in this Volume. That experiment used a macro CHANNEL MODEL module. This 'module' was defined earlier in the experiment entitled *The noisy channel model* in Volume D1.

In subsequent experiments this macro module is represented in patching diagrams as a single module, in order to save space.

Likewise, the BER instrumentation is required in many experiments, and it is convenient to represent it also as a single 'macro module' to save space, and repetition, in patching diagrams.

This Chapter is intended to serve as a convenient reference to the macro BER INSTRUMENTATION module.

This instrumentation has been devised for those experiments which use a pseudo random sequence from a SEQUENCE GENERATOR to provide the source message, and a second SEQUENCE GENERATOR in the instrumentation as a reference.

# the BER instrumentation

### principle

The instrumentation consists of the following elements:

- 1. a sequence generator identical to that used at the transmitter. It is clocked by the message bit clock. This locally supplied sequence becomes the reference against which to compare the received sequence.

- 2. a means of aligning the instrumentation sequence generator with the received sequence. A *sliding window correlator* is used. This was introduced in the experiment entitled *Detection with the DECISION MAKER* in this Volume.

- 3. a means of measuring differences between the received sequence and the reference sequence (after alignment); ie, the errors. The error signal comes from the output of an X-OR gate (the same one used for the sliding window correlator). There is one pulse per error. The counter counts these pulses, over a period set by a gate, which may be left open for  $10^n$  bit clock periods, where n = 3, 4, 5 or 6.

- 4. a method of measuring the signal-to-noise ratio (SNR) of the signal being examined. The WIDEBAND TRUE RMS METER is ideal for this purpose.

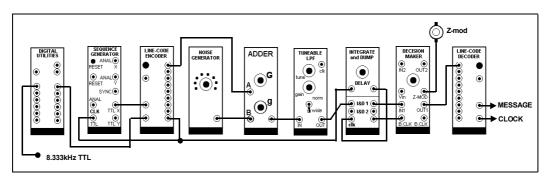

### practice

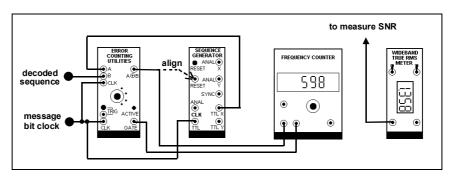

The above ideas are shown modelled in Figure 1 below. It is assumed that the reference sequence generator is identical to, and set up similarly to, that at the transmitter.

Figure 1: BER measurement instrumentation

In future experiments this model will be represented by the pseudo module shown in Figure 2 below.

Figure 2: the BER INSTRUMENTATION macro module.

## setting up

It is assumed that a transmission system is already in existence.

The procedure for setting up the BER INSTRUMENTATION is as follows:

- 1. patch up according to Figure 1

- 2. remove the NOISE from the channel

- 3. align the two sequences (momentarily connect the reset of the instrumentation SEQUENCE GENERATOR to the output of the X-OR gate of the ERROR COUNTING UTILITIES module).

- 4. press RESET of the COUNTER. No digits should be displaying.

- 5. press the TRIG button of the ERROR COUNTING UTILITIES module. The COUNTER should display '1'. This is the 'confidence count', *not* an error count. The COUNTER should remain at '1' for the duration of the PULSE COUNT, verified by the ACTIVE indicator being alight (it flickers during the last 10% of the count period).

- 6. replace the NOISE at a high level. The COUNTER should start counting bit errors (provided the ACTIVE indicator is alight). Reduce the NOISE and the BER should reduce.

#### **Remember:**

- always remove the noise before attempting to align the two sequences.

- the PULSE COUNT indicates the number of bit clock periods for which the GATE remains open (while the ACTIVE indicator is alight), and during which the COUNTER is activated for counting errors.

- the bit error count is the COUNTER display minus '1' (the 'confidence count').

- the ratio (COUNTER DISPLAY 1) / (PULSE COUNT) is the BER.

## theoretical predictions

See your Text book for theoretical predictions of bit error probability of various signals, typically expressed as a function of  $E_b/N_o$ , where:

- E<sub>b</sub> is the energy per bit

- the only corruption is assumed to be additive white Gaussian noise (AWGN), where  $N_o$  is the average noise power per Hz.

From a practical point of view  $E_b/N_o$  is interpreted as the signal-to-noise ratio (SNR). This is a power ratio, and is typically expressed in decibels (dB).

The SNR is measured at the decision maker input.

Plots of bit error probability versus  $E_b/N_o$  will typically involve the function Q(x), where Q(x) is the complementary error function, given by:

$$Q(x) = \frac{1}{\sqrt{2\pi}} \int_{x}^{\infty} \exp\left(-\frac{u^2}{2}\right) du \qquad \dots \dots 1$$

There are many papers in the literature concerning the evaluation of this integral, including that given by P.O. Börjesson, C-E. Sundberg, "Simple approximations of the error function Q(x) for communications applications", IEEE Trans. Com, Vol. COM-27, No.3, March 1979, p639-643.

The above paper was pointed out to me by my colleague Bob Radzyner, who extracted the following approximation from it.

and where

$$v = \chi^2$$

...... 4

# **BIT CLOCK REGENERATION**

| PREPARATION                    |    |

|--------------------------------|----|

| synchronization                | 24 |

| stolen bit clock               | 24 |

| regenerated bit clock          | 25 |

| jitter                         | 26 |

| BIT CLOCK REGEN module         |    |

| procedure                      | 27 |

| bit clock quality              |    |

| system performance             |    |

| EXPERIMENT                     | 29 |

| bit clock recovery - method #1 | 29 |

| adding noise                   |    |

| bit clock 'quality'            |    |

| bit clock recovery - method #2 |    |

| bit error rate                 |    |

| TUTORIAL QUESTIONS             |    |

| APPENDIX                       |    |

| digital delay                  |    |

| divide-by-2                    |    |

# **BIT CLOCK REGENERATION**

**ACHIEVEMENTS:** introduction to bit clock regeneration. Evaluation using bitby-bit comparison with system bit clock.

**PREREQUISITES:** completion of at least some of the early experiments of Volume D1.

ADVANCED MODULES: BIT CLOCK REGEN, LINE-CODE ENCODER, ERROR COUNTING UTILITIES, INTEGRATE & DUMP. A BASEBAND CHANNEL FILTERS module is optional.

TRUNKS: optional 208 kHz sine. Refer Laboratory Manager.

# PREPARATION

## synchronization

Receivers in a digital environment can require synchronization at at least three different levels:

- carrier synchronization (in the case of bandpass signals)

- bit synchronization (at baseband)

- frame synchronization (at baseband)

This experiment is concerned with the second of these. It assumes either that the signal has been transmitted at baseband, or successfully recovered from a higher frequency carrier from which it has been demodulated.

#### stolen bit clock

For most TIMS experiments, when a bit clock is required by a receiver, it has been convenient to use a 'stolen' clock. Bit clock regeneration from the received data stream itself is not a trivial exercise, and is best avoided in the laboratory if at all possible. This eliminates unnecessary complications, and sources of signal corruption, and allows one to concentrate on other aspects of one's investigations.

#### regenerated bit clock

Bit clock regeneration cannot be avoided in a real-life situation. Techniques can be divided into two fundamental types: open loop, and closed loop.

This experiment is concerned with very basic open loop techniques.

#### open loop

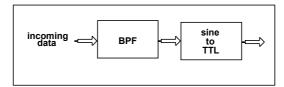

If there is already a component at the bit clock frequency in the spectrum of the data stream, it can be extracted with a bandpass filter (BPF). Alternatively, there may be a component at a higher harmonic; this, instead, could be extracted, and the fundamental obtained by division.

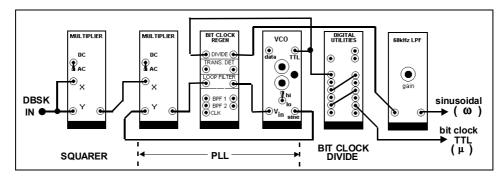

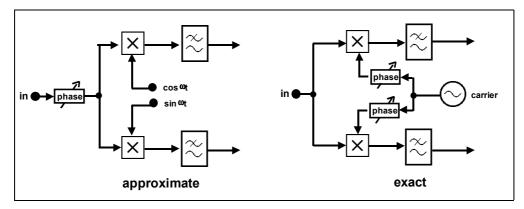

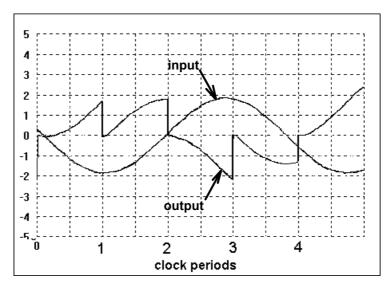

Figure 1 illustrates the basis of the most elementary example of an open loop system, where a component at bit clock frequency already exists in the data.

Figure 1: example of elementary open loop bit clock extraction

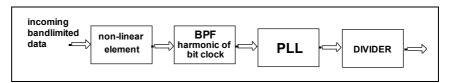

When there is no component at bit clock frequency or any of its harmonics it can probably be created by a non-linear element, as shown in Figure 2.

# Figure 2: creation, and extraction, of a spectral component at bit clock frequency

TIMS non-linear elements in this context are:

- a MULTIPLIER (used as a squarer)

- the CLIPPER, in the UTILITIES module

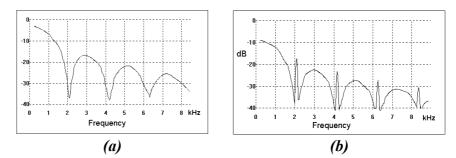

For example, the spectrum of a bipolar pseudo random binary sequence from the SEQUENCE GENERATOR is of the form shown in Figure 3(a) below.

Notice that there are nulls at all the harmonics of the bit clock frequency (2.0833 kHz). If this signal is first bandlimited, then squared, the spectrum, Figure 3(b), now contains lines at the bit clock frequency and its harmonics. A component at the bit rate can be extracted with, for example, a bandpass filter (BPF – see the BIT CLOCK REGEN module), or a phase locked loop (PLL) – or perhaps a combination of the two.

Figure 3: PRBS signal spectrum (a) before and (b) after bandlimiting and squaring

#### closed loop

Closed loop circuits use feedback. They make comparisons with received data and expected data. They can involve the transmitter sending known sequences - training sequences - which are used by the receiver to verify synchronization <sup>1</sup>. Closed loop systems are more accurate than open loop systems, but can be complex and costly. They are outside the scope of present TIMS modules.

### jitter

Bit clock recovery circuits can suffer from timing jitter.

Although the recovered clock is of the correct mean frequency, it can be undergoing either or both of linear and non-linear modulation.

The effects of linear modulation can be removed (or at least reduced) by amplitude limiting - by a comparator, for example.

The effects of non-linear modulation are not so easily overcome.

# **BIT CLOCK REGEN module**

This is the first time the BIT CLOCK REGEN module has been used. It is described in detail in the *Advanced Module User Manual*.

As can be seen, from the drawing of the front panel (opposite), the module contains four independent subsystems. These have been described separately in the Chapter entitled *Digital utility sub-systems* (in this Volume) to which you should refer.

As its name implies, these sub-systems are useful in bit clock regeneration schemes, examples of which are given in the experiment to follow.

You may also devise your own schemes.

<sup>&</sup>lt;sup>1</sup> recall the operation of the sliding window correlator for sequence alignment

### procedure

Some of the signal formats available from the LINE-CODE ENCODER module can be used to test bit clock recovery schemes.

There are only two examples of bit clock recovery scheme given in the experiment to follow - one in detail, and the other in outline.

When completed, you are invited to investigate other methods of recovery in which you are interested. In preparation, here are some reminders of signals and systems which may be useful.

#### signal source

As already mentioned, the LINE-CODE ENCODER, driven by a SEQUENCE GENERATOR at 2.084 kHz, is a good source of bit streams having different characteristics. These serve as inputs to your bit clock regenerator, after passing through a noisy, bandlimited channel.

#### modules

The following modules will be found useful in the work to follow:

- BIT CLOCK REGEN module: not surprisingly, this module will be useful !

- UTILITIES module: contains a CLIPPER/COMPARATOR a useful odd-order non-linear characteristic, and used for converting a sinewave to TTL format.

- a MULTIPLIER, as a SQUARER, provides an even-order non-linear characteristic.

- VCO: as part of a phase locked loop (PLL). There is a loop filter in the BIT CLOCK REGEN module, as well as a TTL divide-by-two sub-system.

- NOISE GENERATOR: a low SNR will put your regeneration system to the test.

- the INSTRUMENTATION MODEL macro module will check BER performance, although a simplified bit clock 'quality' arrangement is suggested.

#### bit clock component present ?

Before modelling a regeneration scheme, it might be a good idea to examine each of the line codes to check whether it already has a bit clock component present in its spectrum.

This can be done with the scheme of Figure 1.

#### bit clock component creation

For those spectra not already containing a spectral line at bit clock frequency try a scheme as illustrated in Figure 2.

#### **BIT CLOCK REGEN BPF**

Using an internal clock, the BPF in the BIT CLK REGEN module may be tuned to 2.048 kHz.

It may be tuned to other frequencies by the use of an external sinusoid (eg, a VCO).

For example, to tune the BPF to 4.167 kHz (twice 2.048 kHz) requires a clock at 50 times this frequency, namely 208.33 kHz. This frequency may be obtained from:

1) a VCO:

a) by setting the on-board switch SW2 to FSK

b) toggling the front panel switch to HI

- c) leaving nothing connected to DATA IN (acceptable as a TTL LO)

- d) adjusting RV7 (FSK1) for 208 kHz output (setting the frequency to 208 kHz by watching the frequency counter is acceptable. However it may be easier to connect a 4.167 kHz sine wave to the input of the BPF and then to tune the VCO for a maximum BPF output).

or

2) TRUNKS. This would be the preferred option.

### bit clock quality

Rather than measure bit error rate over a noisy channel - which tests the complete system - it is instructive to measure just the 'quality' of the recovered bit clock. The term 'quality' is used loosely here. It refers to frequency and phase stability, jitter, and so on. See Tutorial Question Q5.

A method of measuring the quality consists of comparing the regenerated clock with the system clock, using the X-OR in the ERROR COUNTING UTILITIES module, as a performance indicator. A suggested arrangement is shown in block diagram form in Figure 4 below. The phase of the sinusoidal output from the BPF is made adjustable so it may be aligned with the reference bit clock. A digital VARIABLE DELAY is inserted in the gate to the X-OR to control the instant of comparison.

Figure 4: measurement of bit clock quality

By appropriate adjustment of the analog phase and the TTL delay, and with no noise, the arrangement can be set so as to register no errors.

Noise could then be added to the channel in order to make a more demanding test.

Reliable bit clock recovery should be possible for signal-to-noise ratios approaching 0 dB.

This system will be modelled in the experiment.

### system performance

If the quality of the recovered bit clock is considered good, by the previous test, then the overall system performance can be measured by carrying out a bit error rate measurement over the noisy channel.

This is perhaps an unnecessary extension of the experiment, the aim of which was to introduce some basic methods of bit clock recovery, without going into great detail.

# EXPERIMENT

The complete system to be modelled involves many modules. It will be patched up systematically. It is suggested that the modules be inserted into the TIMS frame in the order shown, starting at the extreme left hand side.

In the first example a bit clock will be recovered from the UNI-RZ coded output from the LINE-CODE ENCODER.

This waveform may be shown to contain energy at the bit clock frequency. So it can be extracted with a BPF according to the scheme of Figure 1.

### bit clock recovery - method #1

- **T1** acquire a BIT CLOCK REGEN module. Read about it in the Advanced Modules User Manual. Before plugging it in locate the on-board switch SW1. Set the left hand toggle UP and the right hand toggle DOWN. This tunes BPF #1 to 2.083 kHz, and leaves BPF #2 to be tuned by an external TTL signal (at 50 times the desired passband frequency) later on in the experiment.

- **T2** patch up the diagram of Figure 5, which is a model of the open loop regeneration scheme of Figure 1.

Figure 5: model of Figure 1

- **T3** using the 2.083 kHz as a reference on CH1-A, look at the output of BPF #1 with CH2-A. This will be a sinewave, also on a mean frequency of 2.083 kHz. However, its amplitude will be varying with time. Is this due to amplitude modulation or phase modulation? See Tutorial Question Q1.

- **T4** observe the output of the COMPARATOR on CH2-B. This is a TTL signal, of fixed amplitude, and mean frequency 2.083 kHz. Is its phase varying ?

#### adding noise

The above procedures demonstrated carrier regeneration from a wideband, noise-free signal. Now pass the test signal through a noisy, bandlimited channel.

- **T5** add a noisy, bandlimited channel<sup>2</sup> to the model, as in Figure 6 below. Use a TUNEABLE LPF as the bandlimiting filter, or channel #3 of a BASEBAND CHANNEL FILTERS module. Without noise, adjust the gains of the TUNEABLE LPF (bandwidth set to maximum) and each ADDER to unity. Include the PHASE SHIFTER; it will be required later. Confirm the regenerated carrier is still present at the output of the COMPARATOR.

- **T6** add noise. Estimate at what level of SNR the recovered bit clock might become unusable ? Explain how you made this estimate.

Figure 6: adding a noisy channel

#### bit clock 'quality'

Now add some instrumentation to measure the 'quality' of the recovered clock.

**T7** add the error counting facility shown in Figure 7 below. This is based on the scheme illustrated in Figure 4. As shown, the regenerated bit clock is patched to the 'A' input f the X-OR gate, and the reference (the system bit clock) into the 'B' input.

<sup>&</sup>lt;sup>2</sup> described in the experiment entitled *The noisy channel model* in Volume D1.

Figure 7: the system with instrumentation added

- **T8** first check performance of the error counter with the system bit clock in both inputs 'A' and 'B'.

- **T9** when happy with the previous Task, remove the noise, and replace the stolen bit clock with the regenerated bit clock. Check the alignment of the X-OR inputs. Adjust the DIGITAL DELAY. Adjust the DIGITAL DELAY for no errors <sup>3</sup>. This **must** be possible ! For the record observe the timing of the gating pulse from the DIGITAL DELAY to the X-OR clk with respect to the X-OR inputs (and the range over which it may be moved for no errors to be recorded).

Describe in your notes what you understand by the statement 'adjust the digital delay'.

- **T10** now patch the regenerated bit clock into the 'A' input of the X-OR gate (not via the DIGITAL DELAY). Align the two inputs to the X-OR gate with the PHASE SHIFTER (on-board switch set LO). Adjust the DIGITAL DELAY for no errors.

- *T11* with no errors the recovered clock should be of acceptable quality. Now add noise, and report results.

Record in your notes your opinion regarding the validity of the 'quality' measurements.

### bit clock recovery - method #2

The previous bit clock recovery method extracted a component at bit clock frequency which was already present in the data stream.

This second method is truly a regenerative method, since the data stream will not have such a component present.

<sup>&</sup>lt;sup>3</sup> for details of range setting of the DIGITAL DELAY see the Appendix to this experiment.

It will model the block diagram of Figure 2, using a MULTIPLIER as a squarer.

The model is shown in Figure 8 below. It is complete with recovered bit clock 'quality' assessment instrumentation.

Detailed step-by-step Tasks are not provided.

Figure 8: the TIMS model

You will note that the model contains 13 plugin modules (there are five within the CHANNEL MODEL macro module - but one, the VARIABLE DC, is a fixed module so does not require a free slot). These 13 cannot be accommodated within a single TIMS 301 system.

However, if you use a QUADRATURE UTILITIES module which contains two MULTIPIERS, then there is sufficient space in a single TIMS 301.

The BPF in the BIT CLOCK REGEN module must be tuned to 2.083 kHz by setting the on-board switch SW1 to INT CLK.

The second MULTIPLIER, together with the VCO and LOOP FILTER in the BIT CLOCK REGEN module, implements a phase locked loop (PLL). You might query the need for this, since the output of the BPF is already a sinusoid at this frequency (the sinusoid could be converted to TTL, as required by the EXCLUSIVE-OR gate in the ERROR COUNTING UTILITIES, with the COMPARATOR in the UTILITIES module). Consider the merits of both systems, and try each as time permits.

### bit error rate

A final check of the quality of any bit clock recovery scheme would consist of measuring the bit error rate of the overall system under different conditions.

TIMS can do that, following the procedures set out in the experiment entitled *BER measurement in the noisy channel* (in this Volume). It would call for a second TIMS 301, or a TIMS Junior, to accommodate the extra modules.

It would also go beyond the intended aim of the experiment, which was to introduce some elementary schemes of bit clock recovery.

# **TUTORIAL QUESTIONS**

- **Q1** a bit clock, recovered as a sine wave with varying amplitude, may or may not have uniform zero crossings. Give examples of the two cases. Which one gives rise to timing jitter ?

- *Q2* how would the presence of timing jitter (in your extracted clock) show up on the oscilloscope ?

- *Q3* can you distinguish, using only the oscilloscope, the difference between amplitude jitter and phase jitter on a regenerated clock bit ?

- *Q4* what factors might influence the choice between an open loop and a closed loop bit clock regeneration scheme ?

- Q5 describe the various imperfections from which a recovered bit clock can suffer.

# **APPENDIX**

### digital delay

The DIGITAL DELAY sub-system is built into the INTEGRATE & DUMP module. It is described in the *Advanced Modules User Manual*, as well as in the Chapter entitled *Digital utility sub-systems* of this Volume.

The delay is adjustable by a front panel control DELAY, in conjunction with a toggle switch SW3 mounted on the circuit board. The delays to be expected are shown in the table below.

| SW3-upper toggle | SW3-lower toggle | delay range from front panel, using DELAY |

|------------------|------------------|-------------------------------------------|

| RIGHT            | RIGHT            | 10 µsec - 100 µsec                        |

| RIGHT            | LEFT             | 60 µsec - 500 µsec                        |

| LEFT             | RIGHT            | 100 µsec - 1 msec                         |

| LEFT             | LEFT             | 150 µsec - 1.500 msec                     |

#### on-board switch SW3 settings

The bit clock in the present experiment is 2 kHz, so the period is 500 µs.

### divide-by-2

There is a TTL divide-by 1, 2, 4, or 8 in the BIT CLOCK REGEN module. The onboard switch setting s are shown in the Table below.

| SW2-A (left) | SW2-B (right) | divide by |

|--------------|---------------|-----------|

| DOWN         | DOWN          | 8         |

| DOWN         | UP            | 4         |

| UP           | DOWN          | 2         |

| UP           | UP            | -1        |

on-board switch selectable division ratios

### **CARRIER ACQUISITION**

| PREPARATION        |  |

|--------------------|--|

| EXPERIMENT         |  |

| TUTORIAL QUESTIONS |  |

### **CARRIER ACQUISITION**

*ACHIEVEMENTS:* carrier recovery from a modulated signal, using a phase locked loop.

**PREREQUISITES:** none

ADVANCED MODULES: BIT CLOCK REGEN

# PREPARATION

In a commercial application carrier acquisition (recovery, regeneration) from a (digitally) modulated signal is always required.

In a laboratory situation it has been seen that the use of a stolen carrier is preferred, to sharpen focus on other aspects of the experiment.

In this experiment the main focus is on carrier acquisition.

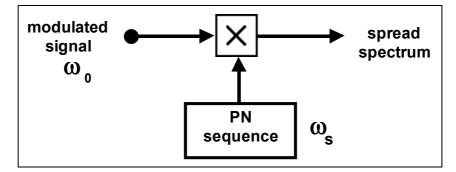

There are two cases to be examined - those modulated signals which already contain a component at carrier frequency, and those which don't !

The latter is far more likely to be the case in commercial practice. Both types of signals are present at TRUNKS.

The modulated signals could have been derived from any of the baseband signals already studied, and then have been translated (modulated) to a higher (carrier) frequency.

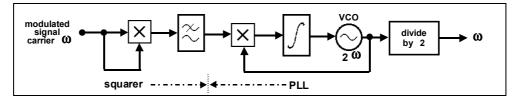

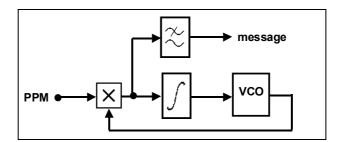

The scheme outlined in Figure 1 will be modelled.

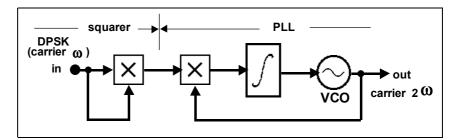

Figure 1: carrier regeneration from a modulated signal

Should there be a carrier component present in the received signal then the SQUARER, and DIVIDE-BY-2, can be omitted. The VCO would be then tuned to  $\omega$ .

# EXPERIMENT

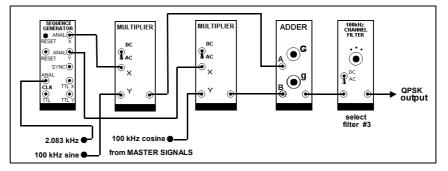

A model of the scheme of Figure 1 is shown in Figure 2.

Observe that the block labelled as DIVIDE-BY-2 in Figure 2 will be a digital (TTL) sub-system, whereas the MULTIPLIER of the VCO requires an analog (sinusoidal) signal. This is easily accommodated by the TIMS VCO since it has both a TTL and an analog output.

The filter in Figure 1 following the SQUARER is perhaps not essential in many cases. It is included for completeness in the block diagram. In this experiment it can safely be omitted. See Tutorial Question Q3.

Figure 2: TIMS model of Figure 1

- *T1* patch up the model of Figure 2 without the SQUARER. Select the modulated signals appearing at TRUNKS on the 100 kHz carrier.

- **T2** use the oscilloscope to view both the incoming signal and the sinusoidal output of the VCO. Trigger to the latter.

- **T3** with the gain of the VCO set fully anti-clockwise (zero loop gain no negative feedback) tune the VCO to near 100 kHz. Watch the two oscilloscope traces. See if you can judge when the VCO is near the carrier frequency.

- **T4** when you think you have tuned the VCO close to the incoming carrier then introduce some negative feedback. Watch for indications of phase lock. If and when it occurs report the frequency of the recovered carrier.

- **T5** in your notes describe the technique you have adopted for obtaining and confirming phase lock with the PLL.

- **T6** is your recovered carrier free of linear or non-linear modulation? What technique did you use to check this?

*T7* introduce the SQUARER to the model, and repeat the previous Tasks, this time working with the TRUNKS signal based on a 50 kHz carrier.

# **TUTORIAL QUESTIONS**

- *Q1* how would the scheme illustrated in Figure 1 be modified if the received signal already had a spectral component at carrier frequency ?

- *Q2* it is essential that the MULTIPLIER following the filter of the SQUARER be AC coupled. Why is this ?

- Q3 what is the purpose of the filter following the SQUARER in Figure 1?

# DPSK - CARRIER ACQUISITION AND BER

| PREPARATION                        |    |

|------------------------------------|----|

| BPSK                               |    |

| DPSK                               |    |

| experiment outline                 |    |

| the transmitter                    |    |

| carrier acquisition                |    |

| channel                            |    |

| theoretical predictions            |    |

| EXPERIMENT                         |    |

| receiver                           |    |

| BER instrumentation                |    |

| BER measurement - stolen carrier   |    |

| carrier acquisition                |    |

| bit clock recovery                 |    |

| BER measurement - acquired carrier |    |

| TUTORIAL QUESTIONS                 | 50 |

### DPSK - CARRIER ACQUISITION AND BER

**ACHIEVEMENTS:** reception and demodulation of a differential phase shift keyed (DPSK) signal, with carrier and bit clock recovery and bit error rate (BER) measurement.

**PREREQUISITES:** completion of the experiment entitled **BER measurement in** the noisy channel (this Volume) is essential; it would be an advantage to have completed the experiments entitled Carrier acquisition (this Volume) and **BPSK - binary phase shift keying** (Volume D1).

**ADVANCED MODULES:** NOISE GENERATOR, LINE-CODE DECODER, DECISION MAKER, ERROR COUNTING UTILITIES, BIT CLOCK REGEN, TRUE RMS WIDEBAND METER, DIGITAL UTILITIES.

**EXTRA MODULES:** a total of three MULTIPLIER modules.

# PREPARATION

### **BPSK**

It is essential that you are familiar with setting up a bandlimited noisy channel, and measuring bit error rates (BER) over it. Thus completion of the experiment entitled *BER measurement in the noisy channel* is a prerequisite to this experiment.

It would be helpful, but not essential, if you have completed the experiment entitled *BPSK* - *binary phase shift keying*, of which the present experiment is an extension.

### DPSK

A disadvantage of BPSK is that the receiver requires a knowledge of the frequency *and* phase of the carrier of the incoming signal.

As for BPSK, DPSK requires a local carrier for successful synchronous demodulation. But the phase of this carrier need not be known. It is the *differential coding* at the transmitter that makes this unnecessary.

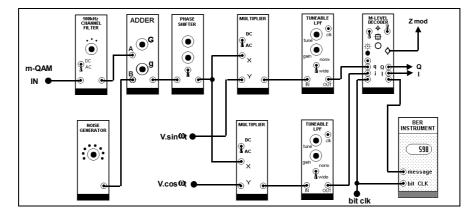

### experiment outline

The experiment is built around the principles investigated thoroughly in the experiment entitled *BER and the noisy channel*, so only an outline of procedures is given below.

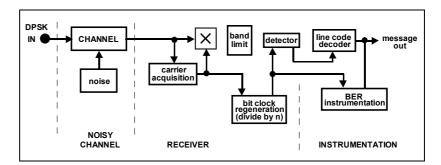

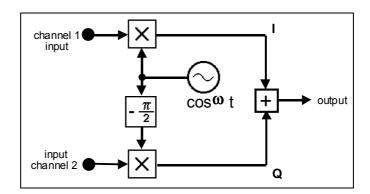

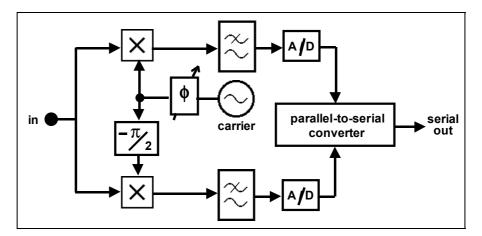

A block diagram of the system to be examined is shown in Figure 1.

Figure 1: the DPSK receiving system

#### the transmitter

You will not be concerned with modelling the transmitter. The DPSK signal will come to you via TRUNKS. It will already be bandlimited.

It will be based on a carrier of exactly 50 kHz.

The message will be supplied at the transmitter by a SEQUENCE GENERATOR of the type you will have, set to a long sequence. It will be clocked at *exactly* 1/24 of the carrier frequency.

You will be responsible for demodulation and message recovery, both by stolen carrier (from TRUNKS) and by carrier acquisition circuitry.

#### carrier acquisition

With the data rate a sub-multiple of the carrier frequency then carrier acquisition circuitry is sufficient to recover both the carrier *and* the bit clock.

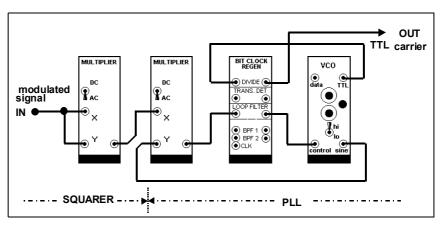

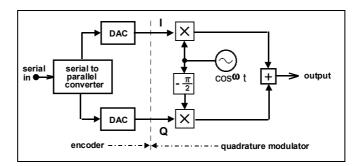

The method of carrier acquisition to be investigated in this experiment involves a squaring operation, followed by a phase locked loop. It is shown in block diagram form in Figure 2 below. Methods of carrier acquisition (including this one) were examined in the experiment entitled *Carrier acquisition* (in this Volume).

Figure 2: carrier and bit clock acquisition

In the scheme of Figure 2 the squaring operation generates a component at twice the carrier frequency. This is not of constant amplitude. It is smoothed by a phase locked loop, which acts as a narrow band filter.

Digital division-by-two will recover a TTL signal at carrier frequency, and a further division-by-twenty-four the 2.083 kHz clock for the DECISION MAKER.

#### channel

The channel is the (non-bandlimited) TRUNKS system, followed by an ADDER, which serves as an injection point for the system noise. Noise bandlimiting will occur at baseband. See Tutorial Question Q1.

### theoretical predictions

Bit error probability ( $P_B$ ) is a function of  $E_n/N_o$ . For synchronous demodulation of DPSK it has been shown that:

The symbols in eqn.(1) are defined in the Chapter entitled *BER instrumentation macro module* (in this Volume).

You will measure not  $P_B,$  but BER; and not  $E_n\!/N_o$  , but SNR. Figure 3 shows theoretical predictions, based on eqn(1) above.

Figure 3: performance prediction - BER v. SNR (DPSK, coherent detection)

# EXPERIMENT

It is expected that you will not be attempting this experiment unless you are an experienced TIMS user. You will have completed the introductory digital experiments, and be familiar with the BER INSTRUMENTATION macro module. It should not be necessary to receive detailed setting up instructions.

This is a big system, requiring more than 12 slots for its modelling. You should plan ahead and decide how to distribute the modules of the receiver, instrumentation, and carrier acquisition models.

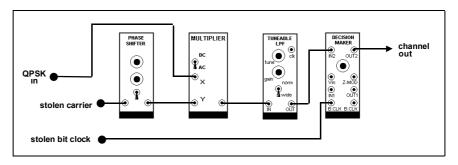

### receiver

You will be modelling the receiver shown in block diagram form in Figure 1 above, and modelled in Figure 4 below.

- **T1** before plugging in the DECISION MAKER set the on-board switch SW1 to accept differential encoding (NRZ-M), and SW2 to 'INT' (manual decision point adjustment).

- T2 before plugging in the PHASE SHIFTER set the on-board switch to HI.

- **T3** patch up the receiver. Initially steal the 50 kHz carrier from TRUNKS and the bit clock (2.083 kHz) from the MASTER SIGNALS module. Set the bandwidth the same as that at the transmitter (or wider ?).

Figure 4: the receiver

- *T4* set the receiver carrier phase for maximum input to the DECISION MAKER. Then use the channel gain to set this level to about the TIMS ANALOG REFERENCE LEVEL.

- **T5** set up the oscilloscope for an eye pattern. Set the decision instant to the appropriate part of the eye.

**T6** confirm the received sequence is a (delayed) copy of the sent message. Confirm the behaviour of differential encoding.

### **BER** instrumentation

Bit error rate measurements will be made with the model described in the Chapter entitled *BER instrumentation macro module* (in this volume). This is reproduced in Figure 5 below.

Figure 5: BER measurement instrumentation

- *T*7 set up the instrumentation. Align the received and reference sequences. With no added noise confirm that there are no errors.

- **T8** add noise. Confirm the error rate worsens as the SNR is reduced.

- **T9** prepare for some serious quantitative BER measurements.

- *a)* match the signal to the input threshold of the DECISION MAKER (about 25 mV).

- *b) add noise into the channel. Set up for a DECISION MAKER input SNR of 0 dB, and an absolute level of the TIMS ANALOG REFERENCE LEVEL.*

### **BER measurement - stolen carrier**

*T10* using a stolen carrier and bit clock, make some quantitative measurements over a range of SNR, and confirm that BER matches expectations.

When satisfied that the system is behaving satisfactorily it is time to replace the stolen carrier with one acquired from the received signal.

### carrier acquisition

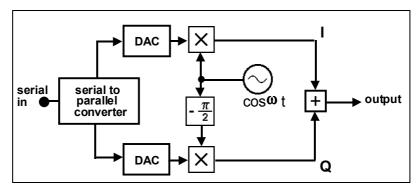

A model of the carrier acquisition scheme shown in block diagram form in Figure 2 is modelled in Figure 6 below.

Figure 6: carrier acquisition model of Figure 2

Note that both the MULTIPLIER modules are AC coupled. There should be no component at DC at the input to the first, so AC coupling is merely a precaution against DC offsets. But the output of the squaring process will produce a large DC component, sufficient to overload the second MULTIPLIER, if nothing else. So it should be blocked.

The 100 kHz TTL output from the VCO is divided-by-two with the sub-system in the BIT CLOCK REGEN module (set the on-board switch SW2 with the left toggle UP and the right toggle DOWN). It is then filtered to a sine wave.

There is a TTL signal into an analog module (60 kHz LPF). Whilst this is usually not allowed (in the interests of linearity) here is one of those cases where it is acceptable ! Even if the input stage (of the filter) is overloaded the next filter stage may not be. Provided the output is a sinusoid (have a look) this is acceptable. After all, this is a filter, so it probably will not pass the distortion components anyway. But see Tutorial Question Q2.

### bit clock recovery

Division-by-24 is required to derive the 2.083 kHz bit clock from the acquired 50 kHz carrier. This is available in a DIGITAL UTILITIES module.

*T11* patch up the carrier acquisition model. Set it up under no-noise conditions. Confirm it is operating as expected.

### **BER measurement - acquired carrier**

- **T12** have the system measuring BER with high SNR. Check the carrier amplitude and phase into the receiver MULTIPLIER. Retain the stolen bit clock. Prepare the acquired carrier to have the same amplitude and phase, then use it instead of the stolen carrier. With high SNR there should be no change to measured BER.

- **T13** decrease the SNR and observe the deterioration of the BER. Not only is poor SNR to the DECISION MAKER causing errors, but the quality of the recovered carrier will have deteriorated - look for jitter.

- **T14** return to conditions of the penultimate Task (high SNR). Change over to the acquired bit clock. It will be necessary to check the alignment of the decision instant using an eye pattern as before.

- **T15** measure BER with a high SNR and compare with previous results. Reduce SNR observe further deterioration of the system BER compared with the stolen carrier condition.

# **TUTORIAL QUESTIONS**

- Q1 noise usually enters the system in the channel. This is at carrier frequency. In the experiment the noise was indeed added into the channel, but it was not bandlimited until it reached baseband. Is this a 'legitimate' experimental technique? What about the 'image response' of the product demodulator - would this cause a problem ?

- *Q2* suppose the recovered carrier was not a pure sinewave, because of overload of the filter. What would be some of the consequences ?

### **PCM-TDM**

| PREPARATION          |  |

|----------------------|--|

| TIMS PCM TDM format  |  |

| TIMS PCM TDM         |  |

| EXPERIMENT           |  |

| independent channels |  |

| multiplexing         |  |

| demultiplexing       |  |

| TUTORIAL QUESTIONS   |  |

|                      |  |

### PCM-TDM

*ACHIEVEMENTS:* creation of a time division multiplexed pulse code modulated -PCM-TDM - signal by interlacing two PCM signals. Demultiplexing of same.

**PREREQUISITES:** completion of the experiments entitled **PCM encoding** and **PCM decoding** of Volume D1.

**ADVANCED MODULES:** two PCM ENCODER and one PCM DECODER (version 2 preferable). A second PCM DECODER is optional.

# PREPARATION

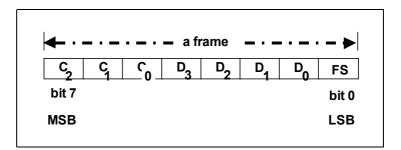

In the experiment entitled *PCM encoding* the PCM signal was generated as a binary data stream.

The sampling rate was one eighth of the bit clock rate.

Samples were coded into binary digital words, and placed into frames of eight slots, each slot being of length equal to a bit clock period.

Each frame contained a coded version of a 'flat top' sample of an analog signal (obtained with a sample-and-hold operation), together with a frame synchronization bit.

If the contents of every alternate frame were removed from the serial data (leaving eight 'empty' slots), then it would appear that the sampling rate had been halved. A consequence of this would be that the allowable bandwidth of the signal to be sampled would have been halved.

The message could still be decoded if each alternate frame could be identified.

Thus the empty spaces in the data stream could be filled with frames derived by sampling another message. These would not interfere with the frames of the first message. Thus two messages could be contained in the one data stream.

This is a time division multiplexed pulse coded modulated (PCM TDM) signal.

### TIMS PCM TDM format

In a PCM TDM system there are several parameters to consider, including:

- a) number of message channels 'n'

- b) bandwidth of each message channel  $B_m$

- c) message sampling rate

- d) bit rate of the PCM TDM signal

In what might be called a 'conventional' system  $B_m$  (and thus the message sampling rate) would be fixed, and independent of 'n'. So as the number of channels increased so would the bit rate of the PCM TDM signal itself. And so the bandwidth of the transmission channel would need to increase with 'n'. Consider these interrelationships carefully.

In the TIMS PCM TDM format the opposite approach has been taken. The bit rate of the PCM TDM signal has been kept fixed, independent of 'n' (although 'n' is fixed at n = 2). So the transmission channel bandwidth can remain fixed, and independent of 'n'. Thus it was necessary to *halve* the message sampling rate when 'n' increased from 1 to 2.

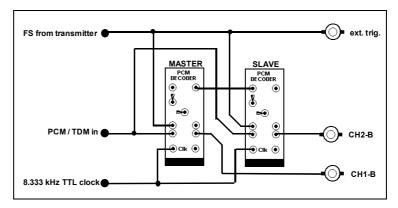

### TIMS PCM TDM

A PCM TDM signal can be created with two PCM ENCODER modules.

Each is driven by a common clock. One is nominated as the MASTER. By connecting its MASTER output to the SLAVE of the second, the second module becomes a SLAVE.

Their outputs can be patched together.

This is *not* a common practice with TIMS modules, but it is allowable in this case (the outputs employ *open collector* circuitry).

Interconnection in this manner automatically (by internal logic) removes every alternate frame from each PCM signal in such a manner that the two outputs can be added to make a TDM signal as described above.

# EXPERIMENT

The experiment will begin by patching up two *independent* PCM signals. When these have been examined they will *then* be combined to make a TDM signal. However, they will share a common clock

### independent channels

РСМ РСМ 1 2 PCI ENCO VARIABLE DC BUFFER )) СН2-В P FNC NFR • ۲ ۲ ۲ #1 🗨 ۲ ۲ ext. trig ۲ CH2-A DC #2 GND ( ))е сн1-а 8.333 kHz TTL clock 🕤 сн1-в

The model will be that of Figure 1 below.

Figure 1: two independent PCM generators

- **T1** patch up the model of Figure 1. Initially set both encoders to 4-bit linear (although you may prefer to change this later on).

- **T2** set the VARIABLE DC output to one end of its range. Reduce the gains of both BUFFER AMPLIFIERS to zero.

- **T3** with the oscilloscope triggered to the FS signal, and displaying it on CH2-B, set the sweep speed to display (say) two or three frames across the screen. Line up the FS signal with the graticule so that the positions of the 8 slots of each frame can be identified. Remember the FS signal marks the <u>end</u> of a frame.

- *T4* view CH1-A and CH2-A (the two channels are identified in Figure 1 as 'PCM 1' and 'PCM 2'). Set each channel to a different pattern, using the two BUFFER amplifiers.

- **T5** identify the alternate '0' and '1' pattern in each output in the LSB position.

they have independently adjustable messages. These are shown here as DC, to ensure stable oscilloscope displays. Later periodic messages will be used.

### multiplexing

Imagine what will happen to the displays on CH1-A and CH2-A when:

- a) the MASTER/SLAVE relationship is invoked

- b) the two PCM DATA outputs are joined to make a common output (as already mentioned, this is *not* normal TIMS practice).

Ostensibly this will make a two-channel TDM signal, with alternate frames being those of channel '1' and channel '2'.

Examine this now. First invoke the MASTER/SLAVE relationship:

- **T6** observe the PCM output from PCM 1 as MASTER, and PCM 2 as SLAVE, while making and breaking a patch between the MASTER and SLAVE sockets. Note how alternate frames of each channel go HI.

- *T7* make a permanent connection between MASTER and SLAVE.

Imagine what will now happen when the two 'common collector' outputs of PCM 1 and PCM 2 are patched together.

- **T8** patch together the two PCM DATA outputs and check your expectations.

- **T9** check what has happened to the alternating '0' and '1' embedded frame synchronization bits which were, before combination of the two channels, at the end of each frame.

- *T10* show that the frame synchronization bit is a '1' for the MASTER channel, and a '0' for the SLAVE.

Currently both messages are DC. Change one to AC. Use an AUDIO OSCILLATOR, or one of the built-in periodic messages. Remember there is no inbuilt message bandlimiting. The sampling rate is now half what it was before the encoders were slaved to each other, so choose your frequency wisely.

*T11* change one of the messages to a periodic waveform. Adjust its amplitude to about 2 volt peak. Explain what you see.

### demultiplexing

When you have convinced yourself that you have indeed made a two-channel TDM signal it is time to patch up a de-multiplexer and endeavour to separate the two messages. If you wish to be very cautious you could first use only one PCM ENCODER, and one PCM DECODER, and revise your understanding of the operation of the two modules.

The Tasks below take up the procedure assuming you are ready for TDM.

Figure 2: PCM TDM demodulator patching

T12 patch up the demodulator as shown in Figure 2. Note that:

- a) each module receives the same clock, 'stolen' from the transmitter

- *b)* each module receives an external FS signal (the embedded frame synchronization circuitry is disabled).

- *c)* the coding schemes selected for each channel match those at the transmitter (where they can be different).

- **T13** two outputs are available from each PCM DECODER the quantized samples, and the reconstructed message from the built-in LPF (version 2 modules). Choose the reconstructed outputs. Confirm the two messages have been recovered one is DC, and the other AC and appear at the correct outputs.

- **T14** as patched in Figure 2 the frame synchronization signal 'FS' has been 'stolen' from the transmitter. Switch the FS SELECT toggle on either or both PCM DECODER modules to EMBED, and show synchronization is maintained.

- *T15* confirm that the coding schemes of the two channels are independent (eg, use 4-bit in one and 7-bit in the other).

**T16** suppose only one PCM DECODER module was available, yet a 2-channel TDM signal is being received. From your knowledge of the operation of these modules, what would you expect to see at its output. Consider carefully before answering this question experimentally.

# **TUTORIAL QUESTIONS**

**Q1** when displaying the PCM TDM signal, it can happen, as the oscilloscope sweep speed is changed (either in fixed steps, or continuously), that sometimes the MASTER channel displays first, and sometimes second. How can it be made to appear first on all occasions ?

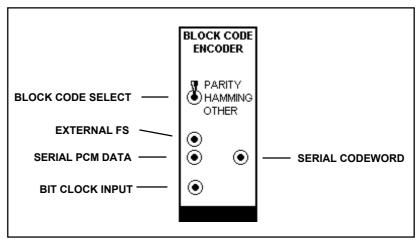

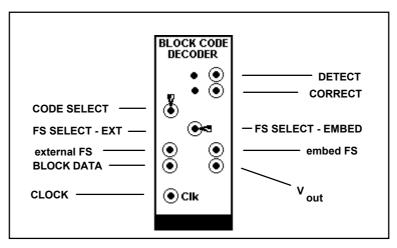

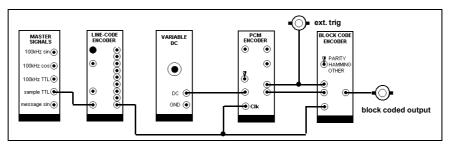

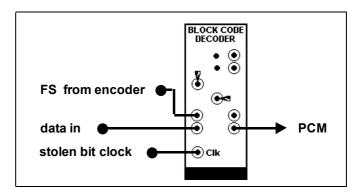

# BLOCK CODING & DECODING

| PREPARATION                     |    |

|---------------------------------|----|

| block coding                    | 60 |

| PCM encoded data format         | 60 |

| block code format               | 61 |

| block code select               | 62 |

| typical usage                   |    |

| block decoding                  |    |

| EXPERIMENT                      | 64 |

| encoding                        | 64 |

| decoding                        |    |