## AI-aided System and Design Technology Co-optimization Methodology Towards Designing Energy-efficient and High performance AI Accelerator

by

#### Kaniz Fatema Mishty

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama December 14, 2024

Keywords: AI accelerator, MRAM, Chiplets, Reinforcement Learning, STCO, DTCO

Copyright 2024 by Kaniz Fatema Mishty

#### Approved by

Mehdi Sadi, Chair, Assistant Professor of Electrical and Computer Engineering

Ujjwal Guin, Associate Professor of Electrical and Computer Engineering

Vishwani Agrawal, Professor of Electrical and Computer Engineering

Yin Sun, Associate Professor of Electrical and Computer Engineering

Akond Rahman, Assistant Professor of Computer Science and Software Engineering

#### Abstract

The rapid growth of artificial intelligence (AI) and deep learning (DL) workloads has created an urgent need for more efficient and high-performance AI accelerators, both at the edge and in cloud data centers. The computational and memory demands of large models, such as ChatGPT and Sora, have far outpaced advancements in semiconductor technology, leading to the emergence of the memory wall and area wall. These challenges necessitate the exploration of new technologies and methodologies. This dissertation presents a comprehensive investigation into emerging memory technologies, innovative architectural designs, and optimization methodologies aimed at improving energy efficiency, performance, and area utilization in AI accelerators.

First, we introduce a high-performance AI accelerator that incorporates spin transfer torque magnetic RAM (STT-MRAM) as the on-chip memory system. Through model-driven design space exploration, we develop a novel scratchpad-assisted buffer architecture that optimizes memory retention time, read/write latency, and energy efficiency by dynamically adjusting for process and temperature variations. Our STT-MRAM-based design (STT-AI) achieves a 75% reduction in area and 3% power savings compared to SRAM-based systems, with minimal trade-offs in accuracy, demonstrating its suitability for modern AI workloads.

Next, we address the limitations of existing accelerators in handling large-batch AI training and inference due to memory bandwidth and capacity constraints. We propose a design technology co-optimization (DTCO)-enabled memory system utilizing spin-orbit torque magnetic RAM (SOT-MRAM) to significantly increase on-chip memory capacity. The limitations posed by STT-MRAM are also addressed by introducing SOT-MRAM. This workload-aware memory system shifts AI accelerators from being memory-bound to achieving system-level peak performance. Our results show an 8× improvement in energy efficiency and 9× reduction in latency for computer vision benchmarks, along with substantial gains

in natural language processing tasks, while consuming just 50% of the area compared to SRAM at the same capacity.

Finally, to address the limitations of large monolithic designs, we explore the potential of chiplet-based architectures for AI accelerators. The vast design space and complex trade-offs between power, performance, area, and cost (PPAC) require a systematic optimization approach. We introduce an optimization framework, Chiplet-Gym, which integrates heuristic-based methods, such as simulated annealing (SA), with learning-based algorithms, such as reinforcement learning (RL), to evaluate and optimize chiplet-based AI accelerator designs by accounting for resource allocation, placement, and packaging architecture. Our results indicate that reinforcement learning demonstrates greater stability and achieves a 16% higher cost model value than simulated annealing. The framework-suggested design choice delivers a 1.52× improvement in throughput, a 0.27× reduction in energy, and a 0.89× lower cost compared to monolithic designs at iso-area, underscoring the potential of chiplet architectures for the next-generation AI hardware.

#### Acknowledgments

I would like to express my gratitude to my advisor, Dr. Mehdi Sadi, for his support and guidance throughout my PhD journey. I am profoundly grateful to the members of my dissertation committee — Dr. Ujjwal Guin, Dr. Vishwani Agrawal, Dr. Yin Sun, and Dr. Akond Rahman — for their valuable feedback, time, and support in helping me refine my research. Their input has been pivotal in improving the quality of this work.

I would also like to extend my heartfelt thanks to my colleagues and friends, whose collaboration and brainstorming sessions helped refine my ideas and made this challenging journey both manageable and enjoyable.

My deepest gratitude goes to my mother, sisters, and father, whose love and unwavering belief in me provided the strength I needed to persevere through the ups and downs of this journey. To my elder sister, Jawata Afnan Saba, thank you for your endless support, encouragement, and sacrifices. Special thanks to my younger sister, Sumaiya Tohorat, for always keeping me cheerful. This achievement would not have been possible without you.

Finally, I believe that everything has been possible because Almighty Allah (SWT) has paved the way for me. His guidance and blessings have given me the strength, wisdom, and perseverance to accomplish this work.

# Table of Contents

| A۱ | ostrac  | et       |                                                                         | 2  |

|----|---------|----------|-------------------------------------------------------------------------|----|

| A  | cknow   | rledgme  | nts                                                                     | 4  |

| Li | st of 1 | Figures  |                                                                         | 9  |

| Li | st of   | Tables   |                                                                         | 17 |

| 1  | Int     | troducti | ion                                                                     | 18 |

|    | 1.1     | Thesis   | Outline and Contributions                                               | 23 |

|    | 1.2     | Backg    | round and Literature Review                                             | 25 |

|    |         | 1.2.1    | Overview of DNN and Generative AI                                       | 25 |

|    |         | 1.2.2    | Overview of AI accelerators                                             | 28 |

|    |         | 1.2.3    | Optimization & Evaluation of Accelerators                               | 32 |

|    |         | 1.2.4    | Impact of memory in AI accelerators & potential of Emerging memory      |    |

|    |         |          | technologies in AI accelerators                                         | 35 |

|    | 1.3     | Thesis   | Organization                                                            | 37 |

| 2  | En      | nergy-ef | ficient and High-performacne AI accelerator with customized STT-MRAM $$ | 38 |

|    | 2.1     | Introd   | uction                                                                  | 38 |

|    | 2.2     | Backg    | round                                                                   | 41 |

|    |         | 2.2.1    | Deep Neural Networks                                                    | 41 |

|    |         | 2.2.2    | Deep Learning/AI Hardware Accelerators                                  | 43 |

|    |         | 2.2.3    | Memory System in AI/Deep Learning Hardware                              | 43 |

|    | 2.3     | Efficie  | nt AI/Deep Learning Hardware                                            | 44 |

|    |         | 2.3.1    | Reconfigurable Core                                                     | 44 |

|    |         | 2.3.2    | STT-MRAM Based On-Chip Memory System                                    | 46 |

|    |         | 2.3.3    | Retention time of Convolution layer followed by FC layer                | 53 |

|    | 2.4     | Optim    | izing STT-MRAM for AI Accelerators                                      | 53 |

|   |     | 2.4.1   | Critical Design and Performance Parameters of MTJ                   | 54  |

|---|-----|---------|---------------------------------------------------------------------|-----|

|   |     | 2.4.2   | Customizing STT-MRAM For AI Accelerators                            | 56  |

|   |     | 2.4.3   | Addressing Process and Temperature Variation                        | 57  |

|   |     | 2.4.4   | MRAM Write Energy Optimization in Accelerator with ScratchPad $$ .  | 60  |

|   | 2.5 | Result  | s and Analysis                                                      | 61  |

|   |     | 2.5.1   | Design Space Exploration for Selecting Memory Capacity              | 61  |

|   |     | 2.5.2   | Memory Retention Time Estimation for AI Models and Accelerator      |     |

|   |     |         | Architecture                                                        | 64  |

|   |     | 2.5.3   | Customizing STT-MRAM for AI Accelerator                             | 64  |

|   |     | 2.5.4   | Energy Optimization with Variable Retention MRAM Banks              | 67  |

|   |     | 2.5.5   | Optimizing Energy with Scratchpad for Partial Ofmaps                | 68  |

|   |     | 2.5.6   | Accelerator Implementation                                          | 68  |

|   |     | 2.5.7   | Accelerator Performance with ImageNet Dataset                       | 71  |

|   | 2.6 | Relate  | d Work                                                              | 71  |

|   | 2.7 | Conclu  | isions                                                              | 74  |

| 3 | Sy  | stem an | nd Design Technology Co-optimization of SOT-MRAM for High-Performan | ice |

|   | AI  | Accele  | rator Memory System                                                 | 75  |

|   | 3.1 | Introd  | uction                                                              | 75  |

|   | 3.2 | Backg   | round                                                               | 78  |

|   |     | 3.2.1   | AI/DL Applications                                                  | 78  |

|   |     | 3.2.2   | AI/DL Accelerators                                                  | 80  |

|   |     | 3.2.3   | SOT-MRAM                                                            | 81  |

|   | 3.3 | DNN '   | WORKLOAD PROFILING                                                  | 82  |

|   |     | 3.3.1   | Memory Bandwidth Expression                                         | 83  |

|   |     | 3.3.2   | Memory Access Patterns                                              | 87  |

|   | 3.4 | DTCC    | O of SOT-MRAM                                                       | 92  |

|   |     | 3.4.1    | Optimizing critical switching current $I_c$                        | 92  |

|---|-----|----------|--------------------------------------------------------------------|-----|

|   |     | 3.4.2    | Optimizing read-write pulse width                                  | 93  |

|   | 3.5 | Result   | s and Analysis                                                     | 94  |

|   |     | 3.5.1    | Bandwidth Demand                                                   | 95  |

|   |     | 3.5.2    | Impact of on-chip memory                                           | 98  |

|   |     | 3.5.3    | DTCO of SOT for PPA Optimization                                   | 100 |

|   |     | 3.5.4    | Process & Temperature Variation and Bitcell Simulation             | 104 |

|   |     | 3.5.5    | System level performance evaluation of SOT-MRAM based Memory .     | 107 |

|   | 3.6 | Relate   | d Work                                                             | 108 |

|   | 3.7 | Conclu   | asion                                                              | 109 |

| 1 | Ch  | niplet-G | ym: Optimizing Chiplet-based AI Accelerator Design with Reinforce- |     |

|   | me  | ent Lea  | rning                                                              | 111 |

|   | 4.1 | Introd   | uction                                                             | 111 |

|   | 4.2 | Backg    | round                                                              | 114 |

|   |     | 4.2.1    | AI workloads and Accelerators                                      | 114 |

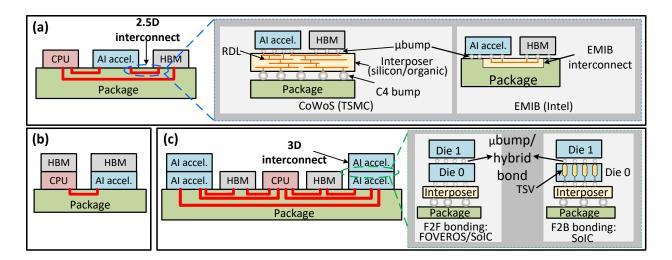

|   |     | 4.2.2    | Chiplets and Heterogeneous Integration                             | 116 |

|   | 4.3 | Throu    | ghput formulation and Design space exploration                     | 117 |

|   |     | 4.3.1    | Top level Architectural exploration                                | 118 |

|   |     | 4.3.2    | Throughput and Energy efficiency formulation                       | 119 |

|   |     | 4.3.3    | Chiplet allocation and Placement                                   | 121 |

|   |     | 4.3.4    | Package architectures and configurations                           | 126 |

|   | 4.4 | Optim    | izing Chiplet-based Architecture                                   | 130 |

|   |     | 4.4.1    | RL problem formulation                                             | 131 |

|   |     | 4.4.2    | Simulated Annealing                                                | 134 |

|   | 4.5 | Exper    | iments and Results                                                 | 135 |

|   |     | 4.5.1    | Experimental method                                                | 135 |

|    |         | 4.5.2    | Implementation details                                           | 136 |

|----|---------|----------|------------------------------------------------------------------|-----|

|    |         | 4.5.3    | Results                                                          | 140 |

|    | 4.6     | Relate   | ed works                                                         | 146 |

|    |         | 4.6.1    | Chiplet-based architecture exploration                           | 146 |

|    |         | 4.6.2    | RL in Design-space exploration                                   | 147 |

|    | 4.7     | Limita   | ations and Future Works                                          | 147 |

|    | 4.8     | Conclu   | usion                                                            | 148 |

| 5  | Co      | onclusio | ns and future works                                              | 149 |

|    | 5.1     | Conclu   | usions                                                           | 149 |

|    | 5.2     | Future   | e works                                                          | 150 |

|    |         | 5.2.1    | Dynamic Re-configuration of Hardware Resources at Runtime to Op- |     |

|    |         |          | timize Energy and Throughput                                     | 150 |

|    | 5.3     | Photo    | nic interconnects in chiplet-based AI accelerators               | 151 |

|    | 5.4     | Recon    | figurable memory system                                          | 151 |

| В  | ibliogı | raphy    |                                                                  | 153 |

| D. | uhlica  | tions    |                                                                  | 160 |

# List of Figures

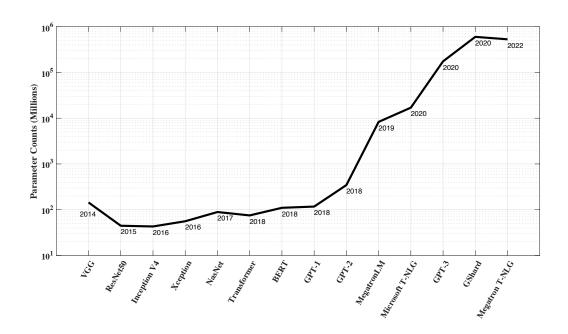

| 1.1 | Growth trend of Deep Learning models with year                                                                                                                                                                                                                                                                   | 20 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

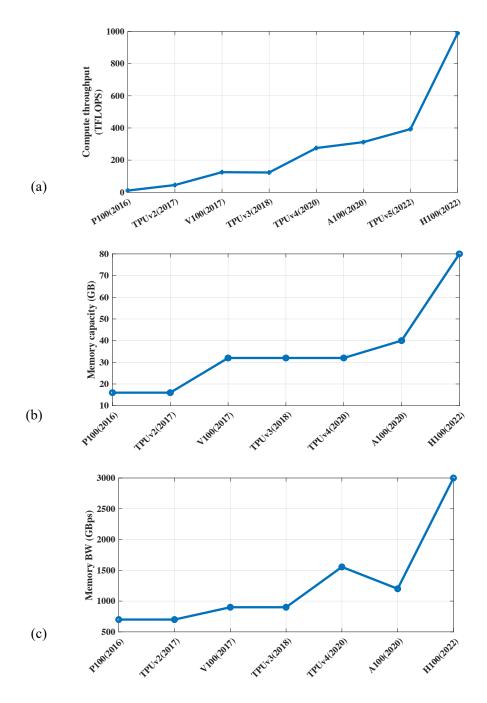

| 1.2 | Trend of AI hardware accelerators specs over the years: (a) Compute throughput (TFLOPS), (b) Memory capacity (GB), and (c) Memory BW (GBps)                                                                                                                                                                      | 21 |

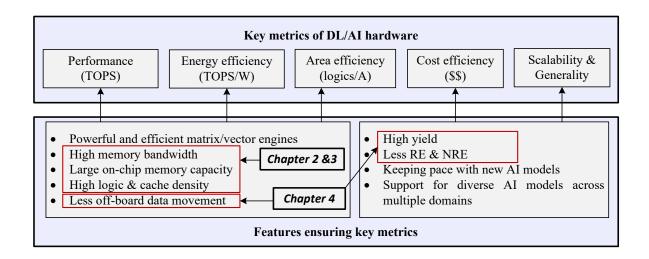

| 1.3 | Thesis outline and contributions: key metrics of DL/AI accelerators and the chapter-wise distribution of the contribution                                                                                                                                                                                        | 24 |

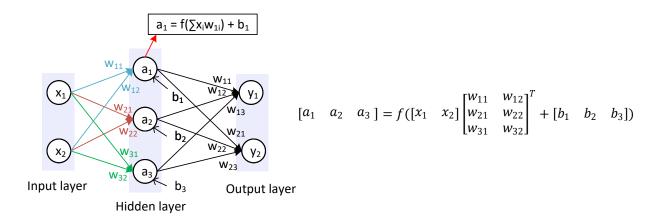

| 1.4 | Vanilla Neural Network (Multilayer perceptron) and its underlying matrix-vector multiplication representation of the hidden layer                                                                                                                                                                                | 26 |

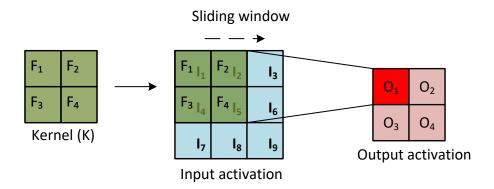

| 1.5 | Illustration of 1D convolution operation. A 2x2 Output activation is generated by convolving a 2x2 Kernel with a 3x3 Input activation with a stride size of 1. Each element of output activation is generated by taking the element-wise dot product of the Kernel and Kernel-overlapped input activation region | 27 |

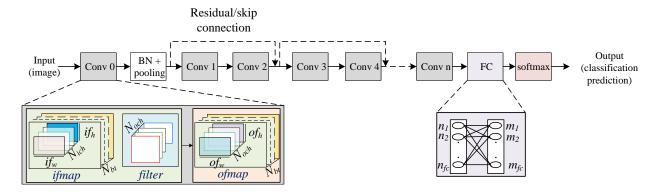

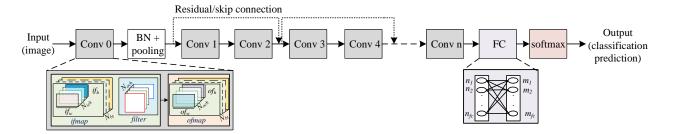

| 1.6 | CV model (CNN/DNN) abstract architecture. Deep convolution (Conv) layers with residual/skip connection followed by fully connected (FC) layer/s. For symbol meaning please see Table 3.1                                                                                                                         | 27 |

| 1.7 | Transformer model workflow breakdown                                                                                                                                                                                                                                                                             | 28 |

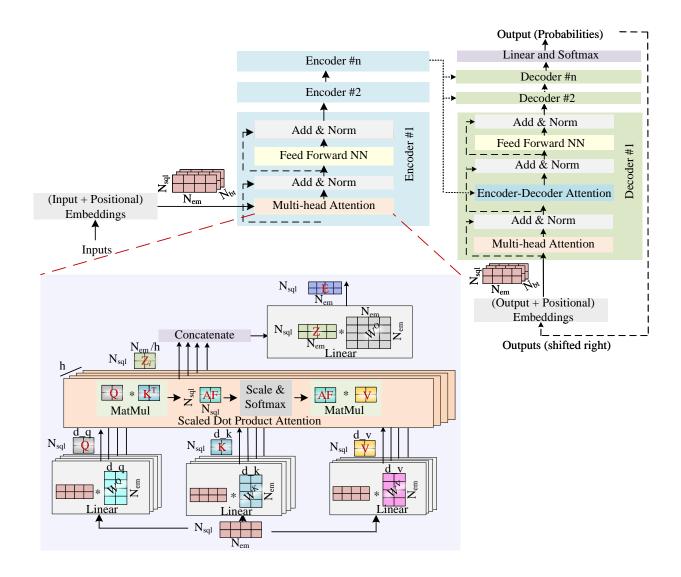

| 1.8 | (a) SIMD type architecture. (b) Systolic array-based Deep Learning accelerator architecture                                                                                                                                                                                                                      | 29 |

| 1.9 | Power and performance comparsion of A100 GPU vs TPUv4, showing the impact of on-chip memory                                                                                                                                                                                                                      | 36 |

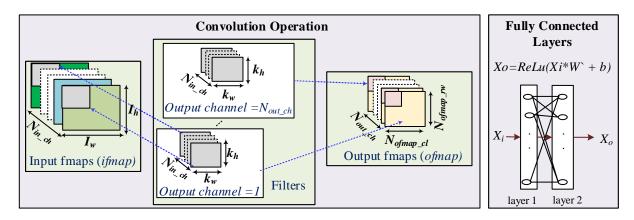

| 2.1  | Convolution and fully connected layer operations                                                                                                                                                                                                | 42 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

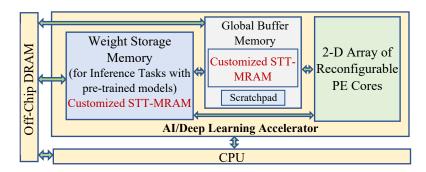

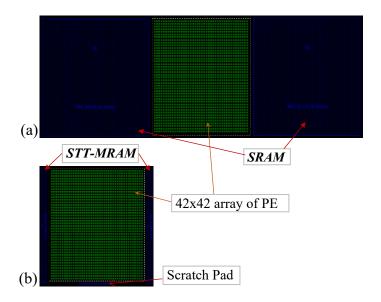

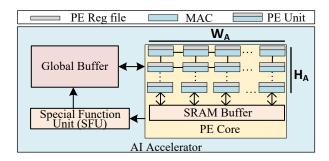

| 2.2  | AI Accelerator with reconfigurable cores optimized for both Conv. and FC layers, and STT-MRAM based on-chip memory                                                                                                                              | 44 |

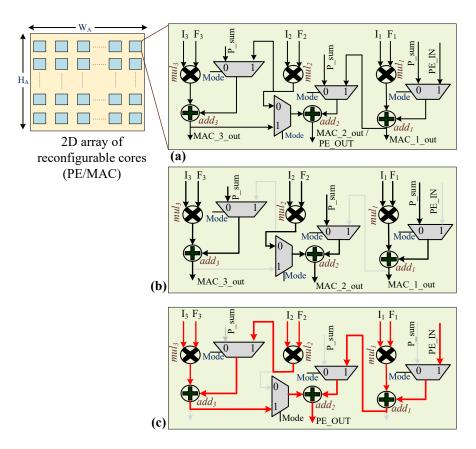

| 2.3  | (a) Reconfigurable core, (b) Reconfigurable core acting as building block of systolic array when mode is low, and (c) Reconfigrable core acting as convolution PE, when mode is high                                                            | 45 |

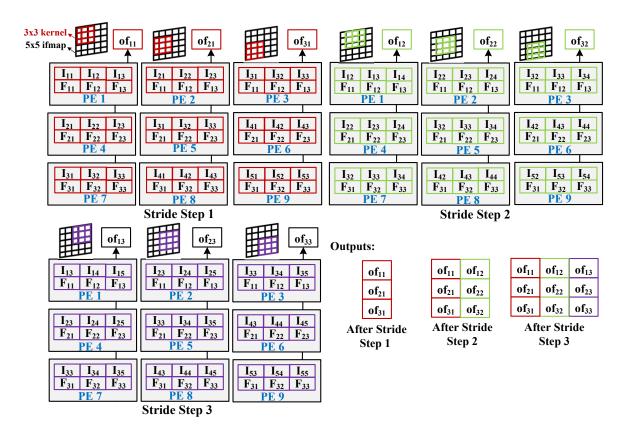

| 2.4  | A $3\times3$ kernel $(k_h=k_w=3)$ is convolved (with stride=1) over a $5\times5$ ifmap to produce $3\times3$ ofmap $(N_{ofmp\_rw}=N_{ofmp\_cl}=3)$ . The size of unit PE block, $P_s=3$ . Total 9 PE blocks are required for this convolution   | 49 |

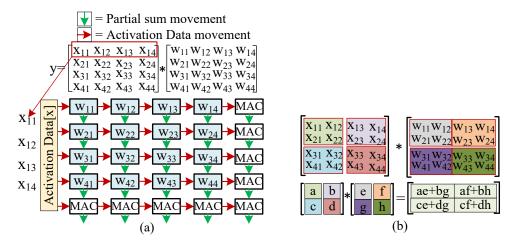

| 2.5  | (a) Dataflow inside systolic array, (b) Larger matrices can be divided into smaller sub-matrices to fit in the systolic array. An example of dividing two $4\times4$ matrix into four $2\times2$ matrices to fit into $2\times2$ systolic array | 51 |

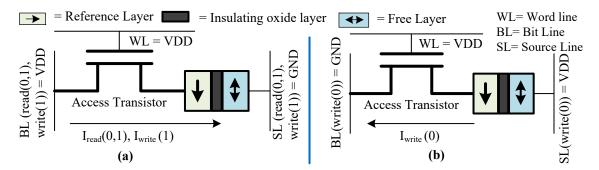

| 2.6  | Bit cell of STT-MRAM. (a) shows reading from it and writing 1, (b) shows writing 0                                                                                                                                                              | 54 |

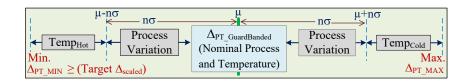

| 2.7  | Impact of process and temperature variation on thermal stability factor ( $\Delta$ )                                                                                                                                                            | 58 |

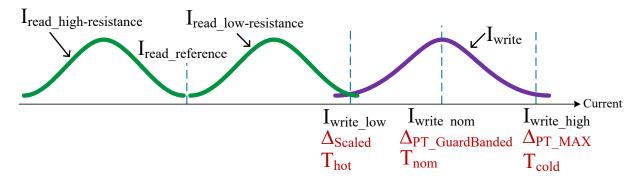

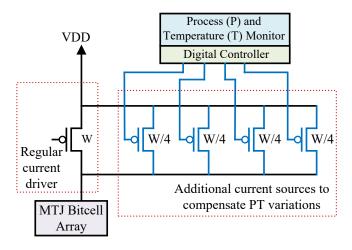

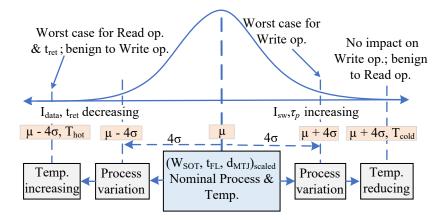

| 2.8  | Distribution of read/write currents with PT variation. Worst-case occurs when worst process corners experience $T_{hot}$ or $T_{cold}$                                                                                                          | 58 |

| 2.9  | Modified Write Driver                                                                                                                                                                                                                           | 60 |

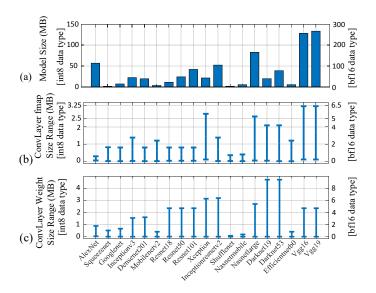

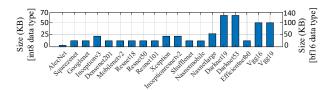

| 2.10 | (a) Complete sizes of widely used AI models. (b) Activation map (ofmap/ifmap) sizes, (c) Weight sizes for Conv layers                                                                                                                           | 62 |

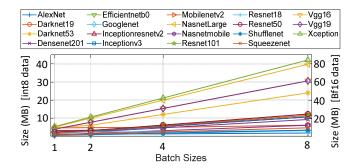

| 2.11 | Required capacity of global buffer with varying batch sizes to avoid DRAM access              |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | during inference                                                                              | 62 |

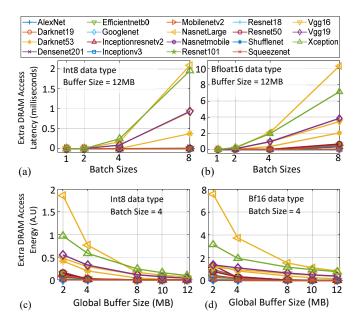

| 2.12 | For Conv. layers, total extra DRAM access latency for varying batch sizes: (a)                |    |

|      | int<br>8, (b) BF16 data types; total extra DRAM access energy for varying GLB size:<br>$$     |    |

|      | (a) int8, (b) BF16 data types                                                                 | 63 |

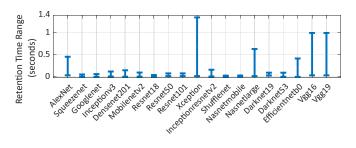

| 2.13 | Global buffer retention time range for 42x42 MAC array (Bfloat16 hardware,                    |    |

|      | CLK details in Table 2.2) and batch size 16                                                   | 64 |

| 2.14 | The required retention time of MRAM global buffer for Bfloat<br>16 hardware (CLK $$           |    |

|      | cycles and frequency given in Table II), (a) varying MAC array capacity. (b)                  |    |

|      | varying batch sizes                                                                           | 65 |

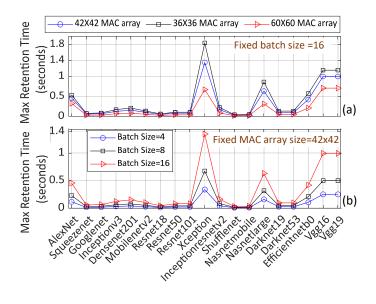

| 2.15 | (a) Thermal stability ( $\Delta$ ) scaling for 3 years retention time (for pre-trained weight |    |

|      | storage NVM application). (b) $\Delta$ and retention time scaling for accelerator's           |    |

|      | global buffer memory design. (c), (d) With scaled $\Delta$ , read pulse width scaling         |    |

|      | while ensuring RD BER is within limit. (e), (f) Write latency scaling with $\Delta$ ,         |    |

|      | within target write error rate. Note: (c), (e) uses base-case (10yrs ret. time)               |    |

|      | from [69], and (d), (f) from [62]. Target BER is chosen to ensure no accuracy                 |    |

|      | impact on AI tasks [76]                                                                       | 65 |

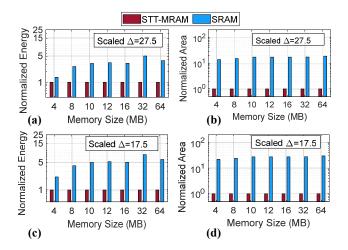

| 2.16 | Energy and area comparison of SRAM and STT-MRAM for various sizes. $\Delta$                   |    |

|      | scaled: (a),(b) for global buffer; (c), (d) for eMRAM banks to store lower half               |    |

|      | (i.e., LSB groups) of weight/fmap bits                                                        | 66 |

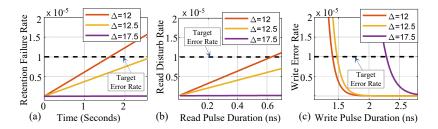

| 2.17 | $\Delta$ scaling with relaxed BER for LSB bit groups. (a) Retention, (b) Read, and            |    |

|      | (b) Write latency within target BER. (Base case, $\Delta = 60$ , data modeled after [62]).    | 68 |

| 2.18 | Maximum size of partial ofmaps                                                           | 68 |

|------|------------------------------------------------------------------------------------------|----|

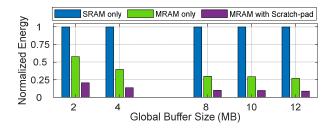

| 2.19 | Comparison of buffer memory energy dissipation for SRAM, MRAM, and MRAM                  |    |

|      | with scratch pad architectures                                                           | 69 |

| 2.20 | Top level floorplan view from ICC2. Accelerator designed with, (a) 12MB SRAM.            |    |

|      | (b) 12MB STT-MRAM with scratchpad                                                        | 71 |

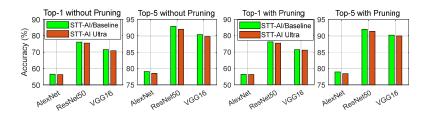

| 2.21 | Top-1 and Top-5 accuracy comparisons for $STT$ - $AI/Baseline$ and $STT$ - $AI$ $Ul$ -   |    |

|      | $tra$ cases. No accuracy change for $STT	ext{-}AI/Baseline$ cases, and negligible (less  |    |

|      | than $1\%$ normalized) accuracy change occurs on $STT\text{-}AI\ Ultra$ acclerator. Both |    |

|      | original and pruned (at 50% pruing rate) [9] model results are shown                     | 72 |

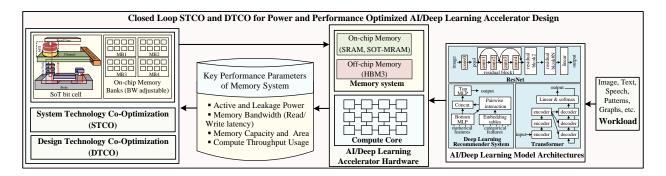

| 3.1  | Workflow of closed-loop analysis for system and device level optimization for            |    |

|      | AI/Deep Learning Accelerator Design                                                      | 76 |

| 3.2  | CV model (CNN/DNN) abstract architecture. Deep convolution (Conv) layers                 |    |

|      | with residual/skip connection followed by fully connected (FC) layer/s. For sym-         |    |

|      | bol meaning please see Table 3.1                                                         | 78 |

| 3.3  | Transformer model workflow breakdown                                                     | 79 |

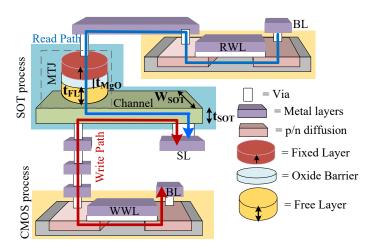

| 3.4  | Physical structure of a SOT-MRAM bit cell highlighting separate read (along              |    |

|      | blue line) and write (along red line) path                                               | 80 |

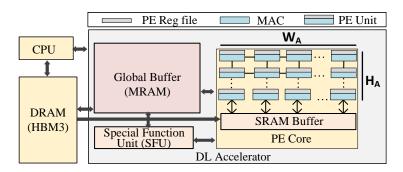

| 3.5  | Block diagram of Accelerator architecture                                                | 82 |

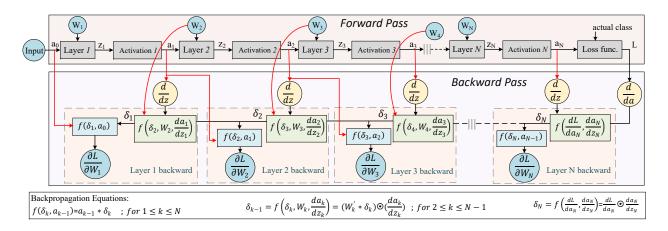

| 3.6  | Computational graph of DNN training                                                      | 82 |

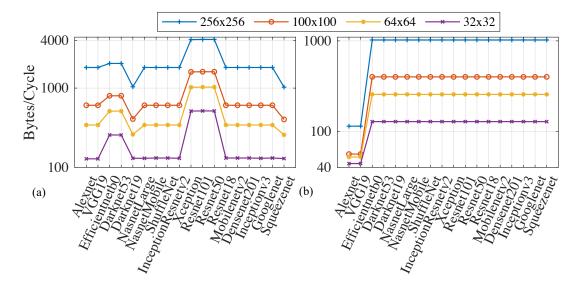

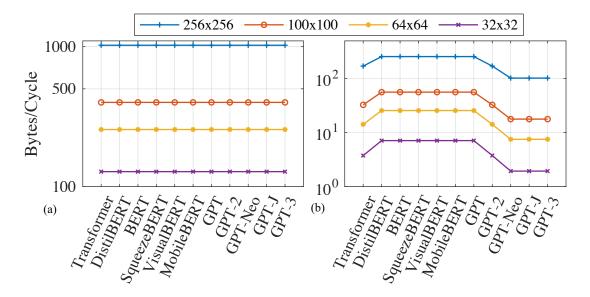

| 3.7  | Bandwidth requirement of CV models for different PE array sizes. (a) Read                |    |

|      | Bandwidth, (b) Write Bandwidth. Bandwidth varies from model to model be-                 |    |

|      | cause of their variation in layer size and type                                          | 96 |

| 3.8  | Bandwidth requirement of NLP models for different PE array size. (a) Read            |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | Bandwidth (for GEMM and softmax operation), (b) Write Bandwidth. Read                |     |

|      | bandwidth is the same across all the models because it is limited by the PE array    |     |

|      | dimension, whereas the write bandwidth varies across models because of their         |     |

|      | different sequence lengths                                                           | 97  |

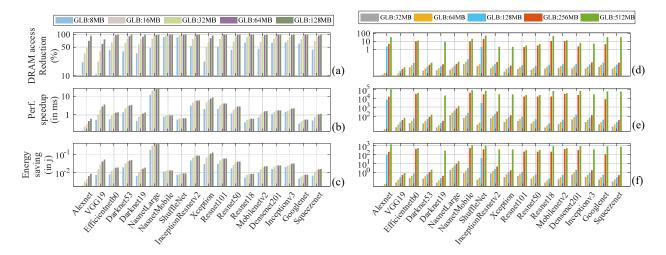

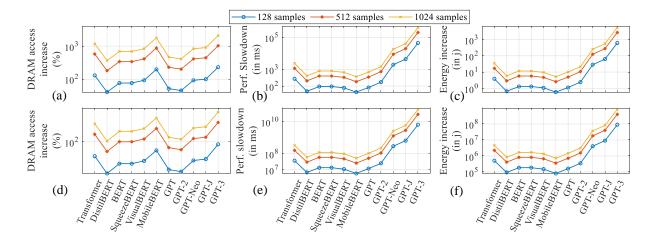

| 3.9  | Impact of larger GLB memories on performance and energy efficiency for CV            |     |

|      | models at inference and training. Percentage reduction in DRAM accesses at in-       |     |

|      | ference (a) and training (d). Performance Speedup from DRAM access reductions        |     |

|      | at inference (b) and training (e). Energy savings from reduced DRAM accesses         |     |

|      | at inference (c) and training (f). Both cases compare results to a baseline of 2MB   |     |

|      | GLB running 16 samples                                                               | 98  |

| 3.10 | Impact of batch size on performance and energy efficiency for CV models at           |     |

|      | inference and training. Percentage increase in DRAM accesses at inference (a),       |     |

|      | at training (d). Performance slowdown (latency increase) from extra DRAM             |     |

|      | accesses at inference (b), at training (e). Energy increase from extra DRAM          |     |

|      | accesses at inference (c), at training (f). In both cases, results are compared to   |     |

|      | a baseline of 16 samples running with 4MB GLB                                        | 99  |

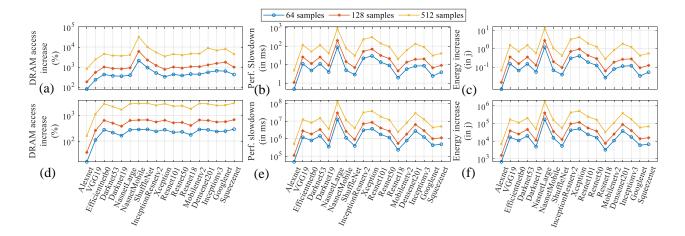

| 3.11 | Impact of larger GLB memories on performance and energy efficiency for NLP           |     |

|      | models at inference and training. Percentage reduction in DRAM accesses at in-       |     |

|      | ference(a), at training (d). Performance Speedup from DRAM access reductions         |     |

|      | at inference (b), at training (e). Energy savings from reduced DRAM accesses at      |     |

|      | inference (c), at training (e). In both cases, results are compared to a baseline of |     |

|      | 2MB GLB running 16 samples                                                           | 100 |

| 3.12 | Impact of batch size on performance and energy efficiency for NLP models at                |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | inference and training. Percentage increase in DRAM accesses, inference (a),               |     |

|      | and training (d). Performance slowdown (latency increase) from extra DRAM                  |     |

|      | accesses at inference (b), at training (e). Energy increase from extra DRAM                |     |

|      | accesses at inference (c), at training (f). Results are compared to a baseline of          |     |

|      | 16 samples running with 4MB GLB                                                            | 101 |

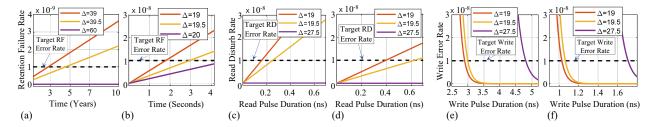

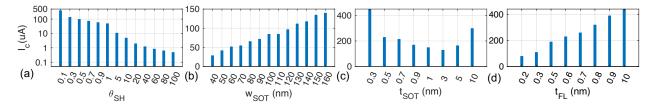

| 3.13 | Critical current vs $\theta_{SH}(a)$ , $w_{SOT}(b)$ , $t_{SOT}(c)$ , and $t_{FL}(d)$       | 101 |

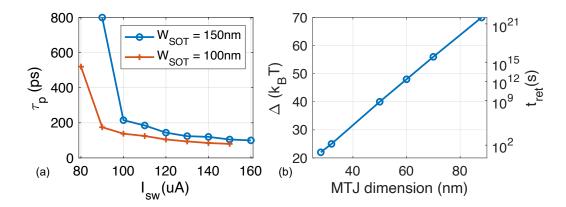

| 3.14 | (a) Switching pulse width $\tau_p$ vs applied switching current $I_{sw}$ . (b) Thermal     |     |

|      | stability factor $\Delta$ (left Y-axis) and retention time $t_{ret}$ (right Y-axis) vs MTJ |     |

|      | dimension for a fixed retention failure rate, $P_{RF}=10^{-9}$ . At $\Delta=70$ , MTJ      |     |

|      | dimension = 88nm, retention time is $> 10$ years [124]                                     | 102 |

| 3.15 | Impact of (a) oxide thickness on TMR, (b) TMR on read latency                              | 102 |

| 3.16 | Impact and distribution of Process and Temperature variation on scaled parameters.         | 105 |

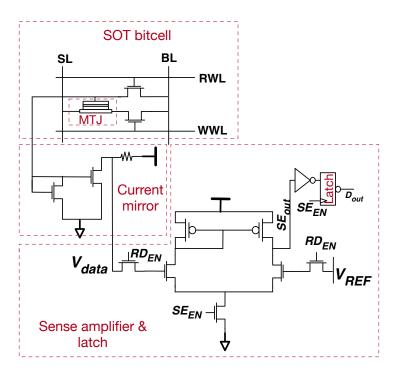

| 3.17 | SOT-MTJ bitcell with read sensing circuitry                                                | 106 |

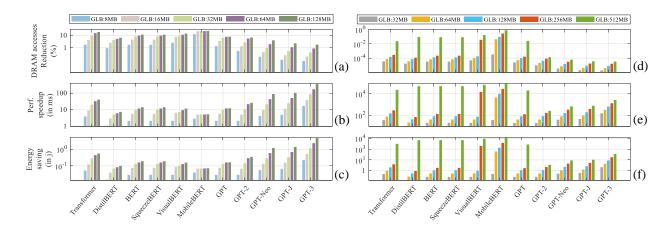

| 3.18 | System level energy improvement with SOT-MRAM and DTCO-optimized-SOT-                      |     |

|      | MRAM over SRAM at the same size for CV (a-d) and NLP (e-h) models. The                     |     |

|      | top plots show energy (a, e) and latency (b, f) for inference, and the bottom plots        |     |

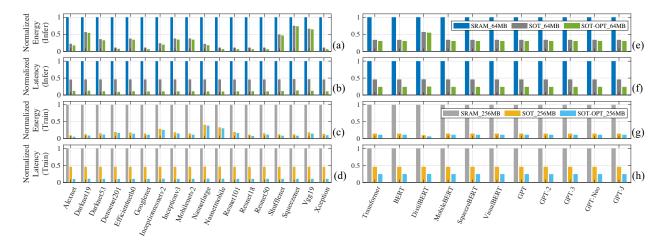

|      | show energy $(c,g)$ and latency $(d,\!h)$ for training                                     | 107 |

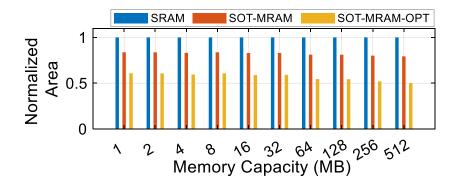

| 3.19 | Area improvement of SOT-MRAM and SOT-MRAM-OPT                                              | 109 |

| 4.1  | AI accelerator chiplet architecture                                                        | 115 |

| 4.2 | Top-level system architecture for different scenarios. (a) CPU, AI accelerator and  |     |

|-----|-------------------------------------------------------------------------------------|-----|

|     | HBM chiplets are connected in package level through 2.5D interconnects. CoWoS       |     |

|     | and EMIB are two options of 2.5D interconnects. (b) CPU and AI accelerator          |     |

|     | chiplets are connected through 2.5D interconnects and HBM is stacked on top         |     |

|     | of CPU and AI accelerator through 3D interconnects. (c) Two AI accelerator          |     |

|     | chiplets are stacked on top of each other through 3D interconnects and they are     |     |

|     | interconnected to CPU, HBM and other AI chiplets pair through 2.5D                  | 116 |

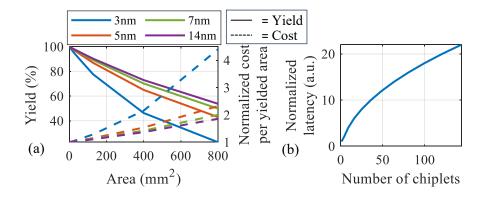

| 4.3 | (a) Yield (left y-axis) and normalized cost per yielded area (right y-axis) vs area |     |

|     | at different tech nodes. (b) Normalized latency vs number of chiplets               | 122 |

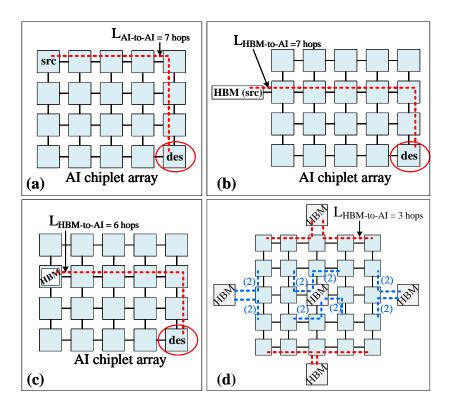

| 4.4 | Illustration of latency (in terms of hop) calculation. (a) AI2AI chiplet commu-     |     |

|     | nication, considering the farthest chiplets as source-destination pair. (b) One     |     |

|     | HBM chiplet, located at the left connected in 2.5D, and the farthest AI chiplet     |     |

|     | as source-destination pair. (c) One HBM chiplet, 3D-stacked on top of a left-       |     |

|     | most AI chiplet, and the farthest AI chiplet as source-destination pair. (d) 5      |     |

|     | HBM chiplets are placed in 5 different positions. The highest latency decreases     |     |

|     | from 6 hops (case (c)) to 3 hops with most of the AI chiplets can be provided       |     |

|     | with data in 2 hops by nearest HBMs                                                 | 125 |

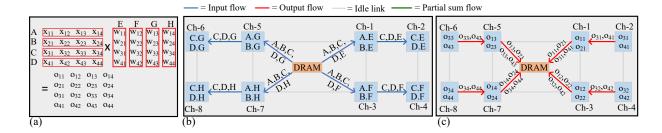

| 4.5 | Illustration of mapping and dataflow. (a) Splitting the matrices into smaller parts |     |

|     | for different chiplets. (b) Initial data supply from DRAM. Once the chiplets are    |     |

|     | loaded with required data, computation begins. (c) Final output collection to       |     |

|     | the DRAM. In this dataflow, there is no inter-chiplet communication during          |     |

|     | computation for partial sum                                                         | 126 |

| 16  | Optimization framework everyion                                                     | 129 |

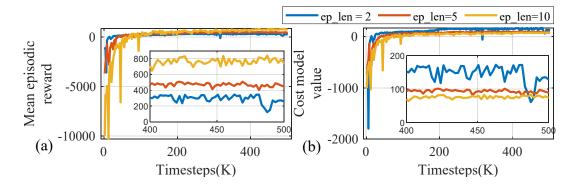

| 4.7  | Impact of episode length in convergence (PPO algorithm). Inset shows the                |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | zoomed-in version of each plot                                                          | 138 |

| 4.8  | (a) Impact of entropy coefficient in RL convergence and (b) impact of temperatue        |     |

|      | on SA convergence . Inset shows the zoomed-in version of each plot. $\ \ldots \ \ldots$ | 139 |

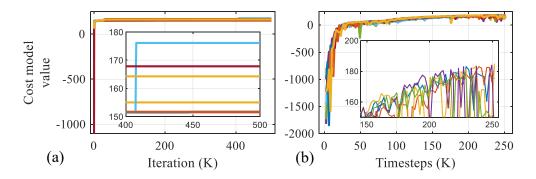

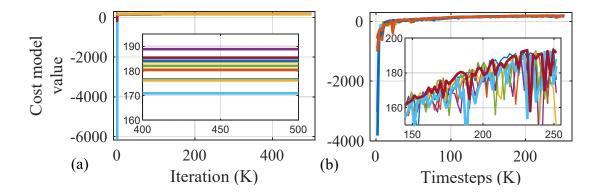

| 4.9  | Convergence behavior of (a) SA and (b) RL for multiple runs with 10 different           |     |

|      | seed values for case (i) (i.e., 64 chiplets). Inset shows the zoomed-in version of      |     |

|      | each plot                                                                               | 141 |

| 4.10 | Convergence behavior of (a) SA and (b) RL for multiple runs with 10 different           |     |

|      | seed values for case (ii) (i.e., 128 chiplets). Inset shows the zoomed-in version of    |     |

|      | each plot                                                                               | 141 |

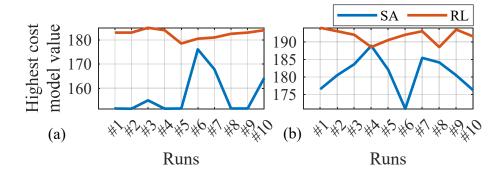

| 4.11 | Highest cost model value achieved by the SA and RL algorithms for multiple              |     |

|      | runs: (a) for 64 chiplets and (b) for 128 chiplets                                      | 141 |

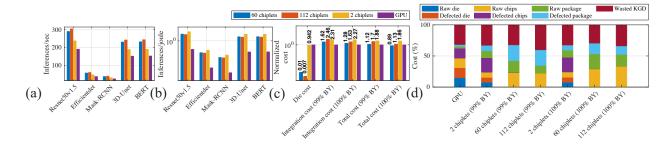

| 4.12 | Comparison of 60-chiplet, 112-chiplet, 2-chiplet and monolithic system: (a) In-         |     |

|      | ferences/sec, (b) Inferences/joule for MLPerf benchmark, and (c) cost. (d) Cost         |     |

|      | breakdown of monolithic, 2-chiplet, 60-chiplet, and 112-chiplet system at $99\%$        |     |

|      | and 100% package bonding yield (BY = bonding yield)                                     | 143 |

# List of Tables

| 1.1 | Commonly known datasets and their sizes                                                                             | 20  |

|-----|---------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Comparative summary of AI accelerator simulator frameworks for design space analysis                                | 33  |

| 1.3 | High-level comparison between SRAM and emerging memory technologies                                                 | 37  |

| 2.1 | Parameters & description                                                                                            | 48  |

| 2.2 | Reconfigurable PE core details (Bfloat16 hardware, and synthesized with 14nm standard cell library [85])            | 69  |

| 2.3 | Accelerator Design Details at 14nm                                                                                  | 70  |

| 3.1 | CNN and systolic array parameters nomenclature                                                                      | 85  |

| 3.2 | RD/WR bandwidth expression of FC layer for different cases                                                          | 86  |

| 3.3 | Parameter nomenclature for Algorithm 1 and 2                                                                        | 87  |

| 3.4 | DTCO control parameters & their impact on Power, Performance and Area (PPA)                                         | 93  |

| 3.5 | Parameters of NLP models                                                                                            | 95  |

| 3.6 | SOT-MRAM DTCO optimized parameters. 30% guard-band are added with thickness and width for process variations        | 103 |

| 3.7 | Dynamic Power consumption (in uW) of SRAM and SOT-MRAM. $(1/0)$ means the corresponding power to access bit 1 and 0 | 106 |

| 4.1 | Parameters and values of Design Space                                                                               | 130 |

| 4.2 | Per hop wire length and delay for 2.5D and 3D architecture [157][130]                                               | 135 |

| 4.3 | Interconnects' properties[129]                                                                                      | 135 |

| 4.4 | PPO hyper-parameters & their values                                                                                 | 139 |

| 4.5 | Optimized parameters for $\alpha, \beta, \gamma = [1, 1, 0.1]$ found by PPO algorithm                               | 140 |

| 4.6 | DNN benchmark features                                                                                              | 142 |

#### Chapter 1

#### Introduction

We are in the era of the Fourth Industrial Revolution, characterized by the unprecedented success of Artificial Intelligence (AI), including advancements in Generative AI. These technologies have transformed our lives in every aspect, from performing monotonous tasks such as data entry and spam email filtering to creative endeavors such as creating artwork, producing images and videos, and understanding complex behaviors of time-series data, protein folding, and DNA structure. AI is revolutionizing various sectors, including healthcare, transport, agriculture, finance, business, education, entertainment, security, etc., to name a few. In many instances, AI-provided solutions have proven to be even more effective than those provided by humans, enhancing efficiency, accuracy, and innovation.

As a result, the demand for Deep Learning and Artificial Intelligence (AI) is growing at a rapid pace across a wide range of applications such, as self-driving vehicles, image and voice recognition, medical imaging and diagnosis, finance and banking, defense operations, etc. Because of these data-driven analytics and AI boom, demands in deep learning and AI will emerge at both data centers and the edge [9, 56, 155]. In a recent market research [56], it has been reported that AI-related semiconductors will see a growth of about 18 percent annually over the next few years - five times greater than the rate for non-AI applications. By 2025, AI-related semiconductors could account for almost 20 percent of all semiconductor demand, which would translate into about \$67 billion in revenue [56]. As a result, significant R&D efforts in developing AI accelerators - optimized to achieve much higher throughput in deep learning compared to GPUs - are underway from academia, big techs, as well as startups [9]. In AI technology innovation and leadership, high-throughput AI accelerator hardware chips will serve as the differentiator [155, 56].

The great success of AI is fueled by the advancement in the semiconductor industry, the computing and storage capacity of computers, the Internet of Things (IoT), and the evolution of Big Data. We are seeing that more computation power is being made available with newer generations of GPUs and AI accelerators, interconnected at lightning speeds. However, the AI advancements are far outpacing the Moore's law. We continue to see hyperscaling of AI models leading to better performance, with seemingly no end in sight. A few of the prime reasons AI models achieve human-level performance are model size and training data set size. These models with hundreds of billions of parameters are trained on thousands of gigabytes of data. The power-law relationship between accuracy and data set growth and the sublinear relationship between model size and dataset size [1] imply that to keep pace with the accuracy improvement, dataset sizes will need to grow by 33-971×, while model sizes will need to grow by  $6.6-456 \times [3]$ . Figure 1.1 shows the trend of growing model size, and Table 1 shows the dataset size of the commonly used datasets used to train the AI models in different domains. The large model and dataset sizes eventually translate into hundreds of exaflops of compute and terabytes of data movement while training/running these models. That being said, it is impossible to use (both in inference and training mode) the Stateof-the-Art AI models with general purpose CPU. Though general-purpose GPUs are able to handle parallel processing, the huge amount of data movement makes them inefficient as well. As a result, Application Specific Integrated Circuits (ASIC)s have evolved, known as AI accelerators, in the last decade. These AI accelerators are specifically designed to take advantage of the inherent parallel computation and data reuse properties of the Deep Learning (DL) models to ensure performance and energy efficiency.

The existing DL/AI accelerators can sustain the computation demand of the current AI models, thanks to the inherent parallel property of the DL workloads. However, with the rapid growth of model and dataset size, even with the advancement in architectural innovation, it is hard to support the DNN/AI models training and inference. As shown

Figure 1.1: Growth trend of Deep Learning models with year

Table 1.1: Commonly known datasets and their sizes

| Dataset Name | Size (Instance or Bytes) |

|--------------|--------------------------|

| ImageNet     | 14M (Image)              |

| Kinetics-700 | 7M (Video clip)          |

| YFCC100M     | 100M (Media Objects)     |

| Wikipedia    | 45TB                     |

| MovieLens    | 25M movie ratings        |

| Jester       | 4.1M continuous ratings  |

| Alibaba      | 2.15B product reviews    |

in Figure 1.2, while the compute throughput has increased by  $900\times$ , the memory capacity and the memory bandwidth have increased only by  $5\times$ , creating the Memory Wall, which means that the hardware is memory bound. Despite having a higher theoretical throughput, the achievable throughput is less because of less memory bandwidth. This translates into huge data movement between processors, from host to processor, and processor to processor, incurring significant performance loss and energy consumption.

Figure 1.2: Trend of AI hardware accelerators specs over the years: (a) Compute throughput (TFLOPS), (b) Memory capacity (GB), and (c) Memory BW (GBps)

Nowadays, with the growing size of parameters and dataset, the models can no longer be trained with a single GPU as the model parameters cannot fit in the main memory of the GPU; even the largest GPU cannot hold the parameters. Hence, the models are trained in the data center with racks of powerful GPUs/TPUs interconnected with PCIe or NVLink with a distributed training technique. When it comes to running AI workloads, energy efficiency is of paramount importance, be it inference or training. While the inference devices have limited battery life, data centers are constrained by electricity costs, environmental impact, and carbon footprint. Producing an image using Generative AI, such as OpenAI's DALL-E 3, consumes an equivalent amount of energy as fully charging a smartphone. The carbon footprint of training a single large language model is around 600,000 pounds of CO<sub>2</sub> emissions, which is the equivalent of 125 round-trip flights between New York and Beijing[50] [51]. The energy usage of data centers is growing exponentially, with projections indicating a surge to 1,000TWh by 2026, further escalating to 2500TWh by 2030 [50] [51]. It is also very expensive to train the LLM models. OpenAI's GPT-3 language model, each training run required at least \$5 million worth of GPUs [52].

As a result, the key metrics of an AL/AI accelerator are: (i) high performance or high throughput (TOPS), (ii) energy efficiency (TOPS/W), (iii) area efficiency (logics/A), (iv) cost efficiency, (v) scalability, and (vi) generality. To ensure performance, the AI/DL hardware should support for parallel workloads, by having powerful matrix and vector engines. To ensure energy-efficiency, they should have high memory capacity, both on-chip and off-chip DRAM, and high memory bandwidth, less data movement. The cost efficiency is ensured by the high yield, less NRE and RE cost. To ensure generality, they should have the ability to keep pace with the rapid ever-evolving DNN/AI model architectures, support for multi-domain and diverse AI/DL models all in one efficiently. With powerful matrix and vector engines, the existing accelerators/GPU offer high performance. However, because of the smaller memory bandwidth and less memory capacity, they suffer from poor energy efficiency and cost efficiency. The challenge is to balance the need for more computational throughput at lower energy and cost.

The goal of this research is to optimize compute and memory resources to meet work-load demands, achieving energy and cost efficiency while maintaining high performance. We hypothesize that memory capacity and bandwidth, both on-chip (cache) and main memory (DRAM), play a significant role in the performance, energy, and cost efficiency of AI accelerators. This thesis presents a System and Design Technology Co-optimization (STCO & DTCO) methodology aimed at achieving energy, area, and cost efficiencies while preserving high performance.

#### 1.1 Thesis Outline and Contributions

Towards achieving energy efficiency, I evaluate the significance of on-chip memory on the energy efficiency and performance of AI accelerators and explore the potential and feasibility of NVM technologies as embedded on-chip memory/cache to increase the on-chip memory capacity. In chapter 2, I design an energy-efficient and high-performance AI accelerator with customized STT-MRAM (Spin Transfer Troque Magnetic Random Access Memory). Based on model-driven detailed design space exploration, a design methodology of an innovative scratchpad-assisted on-chip STT-MRAM based buffer system for high-performance accelerators is presented. Using analytically derived expression of memory occupancy time of AI model weights and activation maps, the volatility of STT-MRAM is adjusted with process and temperature variation aware scaling of thermal stability factor to optimize the retention time, energy, read/write latency, and area of STT-MRAM. In chapeter 3, we address the limitations that we faced with STT-MRAM by introducing SOT-MRAM as the on-chip memory. We develop the memory system with Design Technology Co-optimization (DTCO)- enabled customized Spin Orbit Torque (SOT)-MRAM as large on-chip memory through System Technology Co-optimization (STCO) and detailed characterization of the DL workloads. Together, these chapters provide an important contribution by introducing

Figure 1.3: Thesis outline and contributions: key metrics of DL/AI accelerators and the chapter-wise distribution of the contribution.

a larger on-chip memory and high on-chip bandwidth towards achieving high performance, energy, and area efficiency.

In Chapter 4, we explore the chipset-based AI accelerator to improve performance, energy, and cost efficiency. We analytically model the PPAC (Power, Performance, Area, and Cost) of the chiplet-based AI accelerator and integrate it into an OpenAI gym environment to systematically navigate the vast design space of chiplet-based AI accelerator. This system and package-level co-design methodology aid the designer in finding the optimum design point regarding Power, Performance, Area, and manufacturing Cost (PPAC) in a time and resource constrained environment.

Finally, as shown in Figure 1.3, this dissertation addresses several essential aspects of achieving the primary metrics/qualities of DL/AI accelerators through two straightforward methods: (i) Implementing NVM as on-chip memory to minimize off-chip data movements in chapters 2 and 3, and (ii) Utilizing chiplets to decrease off-package data movement in chapter 4.

#### 1.2 Background and Literature Review

#### 1.2.1 Overview of DNN and Generative AI

The AI that captivates our imaginations today owes its success to the profound capabilities of Deep Neural Networks and Self Attention mechanism. An artificial neuron, mimicking a biological neuron, is a mathematical operation that accepts an input vector, where each element is weighted by a corresponding element of a weight vector. The weighted sum, accumulated with a bias term, is passed through an activation function to generate the final output element. Mathematically, this is expressed as:  $y = act.(\sum_{i=1}^{n} (w_i x_i) + b)$ . There are various activation functions, such as sigmoid, ReLU, leaky ReLU, etc. Multiple neurons are grouped together to form a layer. A network is formed with an input layer and an output layer, with or without hidden layers. The layers between the input and output layers are known as hidden layers. Networks with many hidden layers are known as Deep Neural Networks (DNNs), and the depth of the network is determined by the number of hidden layers. The simplest network is a Multi layer perceptron (MLP) or fully connected layer. Where, each neuron of the previous layer is connected to each neuron of the next layer. Mathematically, the operations performed in each layer are equivalent to a matrix-vector multiplication. The output vector is generated by multiplying the weight matrix with the activation vector, which is either the input or the output of the previous layer. Figure 1.4 shows a vanilla neural network and the mapping of its operations to matrix-vector multiplication.

Another type of layer, best known for extracting spatial information from an image, is the convolution layer, where multiple kernels/filters are convolved over the inputs to generate the output. Figure 1.5 shows the operations performed in convolution operation. The convolution operation can be converted to matrix-matrix multiplication by performing a Im2Col transformation on the input matrix and unrolling the filter matrices and concatenating them

Figure 1.4: Vanilla Neural Network (Multilayer perceptron) and its underlying matrix-vector multiplication representation of the hidden layer.

along the rows [9]. The Deep Neural Networks (DNN) comprising of stacks of multiple convolutional layers connected straight and/or through residual connection [55] to extract the embedded features and one or more Fully connected layers to classify them dominate the Computer Vision (CV) domain of AI. Figure 1.6 shows the typical structure of the CV models. Image classification, captioning, reconstruction and object/instance segmentation are the scopes of CV models. Deep Residual Networks, having convolutional layers at their core, dominate the CV domain.

Language modeling deals with processing sequential data. Recurrent Neural Networks (RNN), Long Short Term Memory (LSTM), and Gated Recurrent Unit (GRU) have been used in language modeling until the state-of-the-art Transformer [111] model is introduced. NLP models are used in machine translation, text summarization, speech recognition, syntactic and semantic parsing, question answering, dialog system etc. Fig 1.7) illustrates the architecture of the Transformer model.

In Generative AI (GenAI) the new realistic data such as text, image, video, etc. are generated by the generative models. These models acquire an understanding of the underlying patterns and structures within their training data, subsequently producing fresh data

Figure 1.5: Illustration of 1D convolution operation. A 2x2 Output activation is generated by convolving a 2x2 Kernel with a 3x3 Input activation with a stride size of 1. Each element of output activation is generated by taking the element-wise dot product of the Kernel and Kernel-overlapped input activation region.

Figure 1.6: CV model (CNN/DNN) abstract architecture. Deep convolution (Conv) layers with residual/skip connection followed by fully connected (FC) layer/s. For symbol meaning please see Table 3.1.

that share similar traits and characteristics of their training data. While there are different approaches to training the generative models, such as Generative Adversarial Networks (GAN), Variational Auto-Encoders (VAE), Transformer based models, and Diffusion models, their building blocks are Deep Neural Networks or the transformer-based self-attention mechanism [2]. As a result, the most compute and memory intensive part of these workloads are also DNN and transformer-based attention mechanism.

Figure 1.7: Transformer model workflow breakdown

#### 1.2.2 Overview of AI accelerators

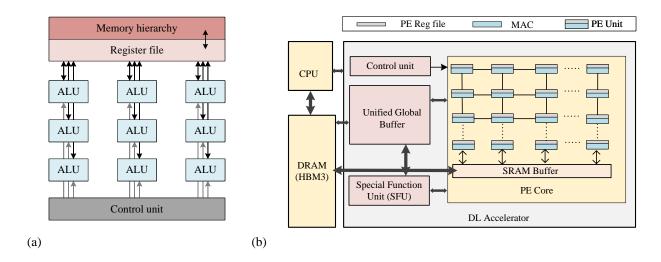

The fundamental component of DNN workloads (such as Conv. layer, FC layer, self-attention mechanism) are MAC (Multiply-Accumulate) operations, which are essentially the matrix-vector/matrix multiplication, or can be converted to matrix-vector/matrix multiplication with massive parallelism. CPUs are inefficient in parallel processing. GPU with temporal features such as vector processing (SIMD), parallel threading (SIMT) can accelerate the parallel computations[9]. However, they are inefficient in data movement. In addition to

Figure 1.8: (a) SIMD type architecture. (b) Systolic array-based Deep Learning accelerator architecture

the parallel computation, systolic array type architecture [4] with spatial features can also leverage the dataflow architecture to reduce the data movement to a significant amount. As a result, Systolic array-based architecture has been widely used in accelerating DNN workloads[155] efficiently. The typical architecture of AI accelerators is composed of array of Processing Elements (PE) containing MAC (multiplier and adder) modules, with/without register file and control unit local to each PE unit along with the Global bufffer (GLB) to hold to weights and activations. The number of PE units and the size of GLB may differ. Figure 1.8 (a) shows the block diagram of a SIMD-type temporal architecture, and Figure 1.8 shows the typical architecture of a Systolic Array-based Deep Learning accelerator.

Diannao[5] and ShiDianNao[6] are two of the earliest accelerator architectures that focused on reducing memory access to improve energy efficiency and performance by playing with memory hierarchy to extract the reuse of operands for CNNs and MLP networks. Eyeriss[7] is an energy-efficient DNN accelerator that introduces Row Stationary (RS) dataflow to maximize data reuse and minimize data movement, utilizing a hierarchical memory structure to significantly reduce energy consumption and improve performance. To

keep up with the diverse structure of DNN layers and to support multiple mapping strategies, flexible architectures such as MAERI [10], Flexflow [11] have recently been proposed. In addition to the massive parallalism and reuse propetry, the DNN workloads come with another special feature, sparsity, that can be leveraged to accelerate the performance and improve energy-efficiency. Sparsity means that a significant amount of activations and weights are either zero or close to zero (because of activation function, regularization, pruning technique). SCNN[8] proposed by NVIDIA is one of the first ASIC architectures supporting sparsity. It leverages sparse operands by first constructing tiles from sparse matrices and then using a dense accelerator substrate for non-zero operands. CambriconX[12] uses hardware indexing to eliminate redundant computations in sparse matrix multiplications, while Cambricon-S[13] enhances software to reduce sparse activation irregularities, simplifying the hardware indexing unit. SIGMA[14] employs specialized interconnects to efficiently handle large-scale sparse computations with irregular operand matrices.

Advances in machine learning, including GenAI, have led to increasingly large and complex models, outpacing the capabilities of conventional accelerators and necessitating new designs for efficient large-scale computation. DaDiannao [15] is one of the earliest accelerator that introduced interconnected accelerators for large network training and inference. Nvidia's Simba[16] features a scaled-out, still targetting inference, on-chip DNN accelerators linked via a silicon interposer. Stanford's Tangram[17] uses Eyeriss-like PEs with a new interconnect structure.

Apart from academia, Google's TPU [155][164], NVIDIA's NVDLA [18], Microsoft's Brainwave [28], Apple's Neural Engine [22], Intel's Nervana Neural Network Processor (NNP) [25], Tesla's FSD [26], Cerebra's Wafer Scale Engine (WSE) [19], SambaNova's Reconfigurable Dataflow Unit (DFU) [23], Groq's tensor streaming processor [24], Huawei's Ascend [29] are the notable and successful accelerators proposed from the industry.

Another domain of AI accelerator research is "In-memory computing" or "Processing-in-memory", where the computation is performed in the memory to reduce the data movement. In this thesis, we only focus on the regular temporal or spatial AI accelerator architecture, not in-memory or processing-in-memory architectures.

#### Chiplet-based AI accelerator

Recent advances in AI, including GenAI, have led to a substantial increase in computational and memory demands on AI hardware across various domains, from edge to cloud. To address the high demand for computing and memory resource capability, chipletbased AI accelerators have recently evolved as a viable solution. Unlike monolithic designs, which are often constrained by the fabrication yields, area, power consumption, heat dissipation, etc., chiplet-based AI accelerators provide scalability, area, yield, and cost efficiency. Simba [16] is one of the first chiplet-based AI accelerators for inference, which integrates 36 chiplets on organic package substrate with ground-referencing signaling (GRS) technology for intra-package communication. Centaur [35] integrates CPU and FPGA chiplets on package targeting recommendation system workloads. SPRINT [36] is a 64-chiplet system with photonic interconnect for DNN inference. [33] proposes a chiplet-based AI accelerator with IMC (In-Memory Computing) technology. [40] proposes a chiplet-based ASIC supercomputer for LLM that optimizes the total cost of ownership (TCO) per generated token. [38] proposes Tascade, a task-oriented scalable chiplet architecture for distributed workload execution, evaluated across 256 distributed chips. NN-Baton [34] is a tool for analyzing and optimizing the granularity of chips that proposes a 4-chiplet AI accelerator for DNN workloads. Monad [41] and SCAR [39] perform design space exploration for chiplet-based AI accelerator, focusing different aspects of the design space, such as monad considers architecture and integration, while SCAR considers multi-model dataflow scheduling on heterogeneous multi-chiplet modules.

#### 1.2.3 Optimization & Evaluation of Accelerators

Impact of Design Space Exploration (DSE) and System & Design technology co-optimization (STCO & DTCO)

With the AI models becoming increasingly complex and large, the design space of the AI accelerators are also booming. As a result, the importance of Design Space Exploration (DSE) and system and design technology co-optimizations across the entire stack, starting from the AI application to all the way down to the circuit and device level of the hardware running the AI models, has become pivotal to ensure the high performance, energy, area, and cost efficiency. The standalone optimization of any component of the stack, may lead to sub-optimal accelerator design. Edge devices are constrained by area and energy, while cloud or data centers are constrained by latency and environmental impact. The prediction accuracy of AI models should be given a high priority for Safety-critical applications such as wearable medical devices, autonomous vehicles and (Depart of Defense) DoD applications.

The key attributes contributing to the quality of AI accelerator are dataflow and mapping styles, and hardware resources. Dataflow styles incorporate computation order, loop tiling and parallelization strategies. While HW resources incorporate on-chip compute resources, memory hierarchy, on-chip memory capacity, and bandwidth, main memory capacity and bandwidth. Going from monolithic to multi-chiplet based AI accelerator, the design space further explodes, with different types of packaging and interconnect architectures, to name a few. From architectural perspective, resource allocation, monolithic or multi-chiplet based architecture, memory hierarchy, memory capacity, mapping and dataflow of the DNN workloads across the compute and memory resources should be considered. From communication and integration perspective, chiplet and memory placement, routing protocols, stacking/packaging technologies, interconnect types, bandwidth, and finally from application perspective, system requirement, such as reliability, scalibility etc., should be considered all

at the same time capturing their inter-dependency while optimizing for PPAC (Power, Performance, Area, and Cost).

Table 1.2: Comparative summary of AI accelerator simulator frameworks for design space analysis

|                                              | Simulator/Optimizer/<br>  Architecture                        | Design space/Architectural details                                                                                                                                                                                                   | Monolithic/<br>Chiplet-based        |

|----------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Scale-sim [27]                               | Performance Simulator                                         | (i) Dataflow: WS, IS, OS<br>(ii) HW resource: No. of PE, on-chip memory size<br>(iii) Architecture type: Eyeriss, TPU                                                                                                                | Monolithic                          |

| Timeloop+<br>accelergy [53]                  | Mapping optimizer + Performance, energy, and area simulator   | (i) Dataflow: WS, IS, OS (ii) HW resource: No. of PE, on-chip memory size (iii) Different memory hierarchies (iv) Architecture type: Eyeriss, Simba                                                                                  | Monolithic                          |

| Maestro [186]                                | Performance and energy<br>Simulator +Optimizer                | (i) Dataflow: flexible (ii) HW resources: Number of PEs, NoC BW/Latency, on-chip memory size (iii) Architecture type: NVDLA-like                                                                                                     | Monolithic                          |

| Astra-sim [31]                               | Performance Simulator                                         | (i) Distributed training: data, model, hybrid parallelism<br>(ii) Hierarchical collective algorithms: on-load, off-load<br>(iii) Fabric design: number of links & latency/BW per link<br>(iv) Fabric topology: pt-to-pt, 2D/3D Torus | Multi-chip<br>(package/board level) |

| STONNE [30]                                  | Performance, energy and area<br>Simulator                     | Architecture type: flexible & reconfigurable architecture                                                                                                                                                                            | Monolithic                          |

| Confucuix[49]                                | Performance and energy optimizer                              | (i) HW resource: Number of PE, on-chip buffer size                                                                                                                                                                                   | Monolithic                          |

| SIMBA [16]                                   | Performance & power<br>Optimizer + 36-chiplet<br>Architecture | (i) Mapping and tiling strategies<br>(ii) 36 NVDLA chiplets connected in 2D mesh                                                                                                                                                     | Multi-chip<br>(package level)       |

| SPRINT [36]                                  | 64-chiplet Architecure                                        | 64-chiplet architecture with photonic interconnect<br>for interchiplet communication                                                                                                                                                 | Multi-chip<br>(package level)       |

| NN-Baton [34]                                | Simulator + Optimizer                                         | (i) No. of accelerator chiplets: 1, 2, 4, 8 (ii) On-chip memory: 36 to 642KB (iii) Different mapping strategies (iv) Routing topology: Ring                                                                                          | Multi-chip<br>(package level)       |

| Moand[41]                                    | Optimizer                                                     | (i) No. of accelerator chiplets (ii) mapping & tiling (iii) packaging (iv) network topology (v) placement                                                                                                                            | Multi-chip<br>(package level)       |

| TVLSI'20[183]                                | Simulator                                                     | (i) 64-core ROCKET-64 architecture<br>(ii) 2.5D interposer-based centralized NoC                                                                                                                                                     | Multi-chip<br>(package level)       |

| Magnet [32]                                  | Area, Power, Performance<br>optimizer and RTL generator       | (i) Dataflow: WS, OS, WS-LOS, OS-LWS (ii) HW resources: No. of PE, on-chip memory size (iii) Precision: 4/8 bits (weight/activation), 16/20/24 bits (accumulation) (iv) Operating frequency: 0.5 GHz, 1 GHz                          | Monolithic                          |

| Chiplet-gym<br>(This work<br>Chapter 4 [37]) | Performance, power, area and cost Optimizer                   | (i) No. of AI accelerator chiplets, no. & location of HBM chiplets (ii) package architecture: 2.5D, 3D (iii) Interconnect types & configuration (details in Table 4.1)                                                               | Multi-chip<br>(package level)       |

## Use of AI/ML in design space exploration and optimization

With the exponential increase in valid design points within the design space, learning-based approaches, especially Reinforcement Learning (RL), have become more popular than traditional heuristic and metaheuristic-based search algorithms due to their efficiency and performance. Apollo [47] uses black-box optimization methods and transfer learning for

sample-efficient accelerator design. Confuciux [49] uses RL and genetic algorithm to explore the on-chip HW resource allocation on AI accelerator for a given dataflow and reuse. Zeus [45] co-optimizes performance and energy by finding optimal job and GPU-level configurations for recurring DNN training jobs using RL. [46] proposes a Deep Reinforcement Learning (DRL) based frmework for exploring the router-less Network-on-chip (NoC) design space. [48] uses multi-agent reinforcement learning to optimize DRAM-memory controller. Apart from architectural design space exploration, RL has also used in back-end of ASIC design, such as physical design [42], circuit design [43][44].

#### Existing simulators, optimizer and and DSE frameworks

To evaluate the performance and efficacy of the accelerators, and to accelerate the research, simulators and optimization frameworks have been proposed, specifically tailored for DNN accelerators. Scalesim [27] is one of the earlier simulator for systolic array type architecture. Given the architectural and workload parameters, it outputs the computation cycles, mapping utilization, SRAM and DRAM bandwidth. Timeloop+Accelergy[53][54] projects the performance and energy-efficiency of DNN accelerator for inference exploring different mapping and tiling strategies. While these two simulators work in layer-wise, STONNE[30] is an end-end, meaning that it can simulate the entire model, cycle-level simulator for both flexible architectures such as MAERI[10], SIGMA[14] and conventional architectures, such as Eyeriss[7]. MAESTRO[186] is another simulator which takes DNN models, mapping or dataflow and hardware resources as input, and outputs the performance report such as latency, NoC bandwidth requirement, and cost report such as activity count (energy), buffer size requirement, data reuse amount, etc. ASTRASIM [31] is the only system-level simulator available today, supporting distributed machine learning as well. Table 1.2 shows the framework for design space exploration in the literature.

# 1.2.4 Impact of memory in AI accelerators & potential of Emerging memory technologies in AI accelerators

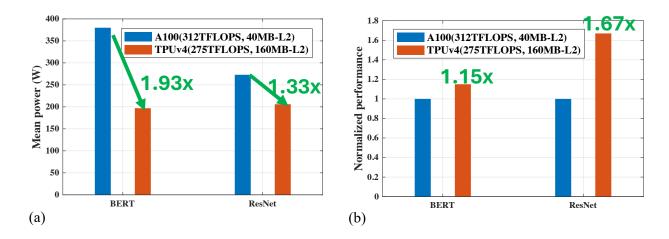

When it comes to DNN workload processing, on-chip memory plays a crucial role in performance and energy efficiency. Because data movement from processor to memory is two orders of magnitude more expensive than MAC (Multiply-Accumulate) operation, the dominant arithmetic operation in DNN workloads. Each MAC operation requires three memory reads (filter weights, fmap (feature map) activation, and partial sum) and one memory write operation [9]. Each memory access is at least 200× more energy and latency expensive than the MAC operations. The idea is that the more weights and intermediate activations can be accommodated in the on-chip memory, the off-chip main/DRAM access can be reduced, hence improving the performance and energy efficiency. A comparative analysis between A100 and TPUv4 processors, as shown in Fig. 1.9, effectively illustrates the impact of onchip memory on performance and energy efficiency. The A100, with specifications of 312 TFLOPS and a 40MB L2 cache, is compared to the TPUv4, which boasts 275 TFLOPS and a 160MB L2 cache. The performance metrics reveal that for the BERT model, the TPUv4 demonstrates a 1.93× reduction in mean power (measured in watts) compared to the A100. Similarly, for the ResNet model, the TPUv4 shows a 1.33× reduction in mean power over the A100. Furthermore, the normalized performance for BERT is 1.15× higher with the TPUv4, while for ResNet, the TPUv4 offers a 1.67× increase over the A100. These data points clearly indicate that TFLOPS is not the sole determinant of performance, highlighting the critical role of memory capacity.

Recent advancements in on-chip memory capacity across industry further underscore this point. NVIDIA's transition from the A100 to the H100 demonstrates an increase in L2 cache capacity from 40MB to 50MB, integrated with a transformer engine, signifying significant improvements in processing efficiency and capability. AMD's MI300 processor

Figure 1.9: Power and performance comparsion of A100 GPU vs TPUv4, showing the impact of on-chip memory.

incorporates 190GB of HBM3 and 3D-vCache technology with 144MB SRAM, representing a leap in memory architecture that enhances computational throughput and efficiency. Cerebras' WSE-2 [19] features 40GB of on-wafer memory, underscoring the shift towards integrating substantial memory directly on the chip to optimize performance. Similarly, Groq's TSP [24] boasts 220MB of SRAM, illustrating the industry's focus on increasing memory capacity to reduce the energy and latency hungry data movement.

SRAM has been predominantly used as the on-chip memory for CPUs and GPUs due to its ultra-fast access times (in pico-second range), unlimited endurance (exceeding 10<sup>16</sup> cycles), and scalability with technology scaling. However, for such large memory capacity as demanded by AI accelerators, SRAM is an expensive technology in terms of silicon footprint, with a relatively low integration density of only dozens of megabits per millimeter squared. It also suffers from high standby leakage power, ranging from tens to hundreds of picowatts per bit. As a result, to meet the demand of AI accelerators' Global Buffer (GLB), exploration of alternate memory technologies has gained interest. Emerging memory technologies, such as MRAM, RRAM, PCM etc. have shown potentials. Table 1.2.4 shows a comparsion between the properties of emerging memories and SRAM.

Table 1.3: High-level comparison between SRAM and emerging memory technologies

| Droporty          | Resistive RAM    | Phase Change | Magnetic RAM | Static RAM |  |

|-------------------|------------------|--------------|--------------|------------|--|

| Property          | (RAM)            | Memory (PCM) | (MRAM)       | (SRAM)     |  |

| Cell area         | $4 - 12F^2$      | $4 - 30F^2$  | $6 - 50F^2$  | $160F^{2}$ |  |

| (Storage density) | (High)           | (High)       | (High)       | (Low)      |  |

| On/OFF            | High             | High         | Low          | High       |  |

| resistance ratio  | Ingn             | Ingn         | LOW          | Ingn       |  |

| Retention time    | > 10y            | > 10y        | > 10y        | NI / A     |  |

| (Non-volatility)  | (High)           | (High)       | (High)       | N/A        |  |

| Leakage power     | Low              | Low          | Low          | High       |  |

| Write latency     | 100ns            | 150ns        | 10ns         | < 1ns      |  |

| Write energy      | 2nj              | 6nj          | 1nj          | 0.2nj      |  |

| Read latency      | 10ns             | 10ns         | 10ns         | < 1ns      |  |

| Endurance         | $10^6 - 10^{12}$ | $10^{9}$     | $10^{15}$    | $10^{16}$  |  |

For example, as shown in Table 1.2.4, while the emerging memories have the advantages of high integration density they also face high write energy and latency. A co-optimization methodology, guided by the demands of AI workloads and applications, is required to extract the benefits while discarding its drawbacks.

#### 1.3 Thesis Organization

The thesis is organized as follows. In Chapter 2, we design an energy-efficient and high-performance deep learning accelerator with customized STT-MRAM. In Chapter 3, the drawbacks of STT-MRAM is mitigated by introducing SOT-MRAM in the memory system and performing a system and design technology co-optimization of the system requirement, workloads, and SOT-MRAM. In Chapter 4, we present Chiplet-gym, a Reinforcement Learning based system and package level co-design methodology for chiplet-based AI accelerator. Finally, the thesis is concluded in Chapter 5 with potential future research direction.

### Chapter 2

Energy-efficient and High-performacne AI accelerator with customized STT-MRAM

# 2.1 Introduction

On-chip memory capacity plays a significant role in the performance and energy efficiency of AI tasks [9, 7, 58, 155]. In AI accelerator, off-chip Dynamic Random-Access Memory (DRAM) accesses can take 200 times and 10 times more energy compared to the local register file and global buffer memory, respectively [7]. Larger on-chip buffer memory is needed to minimize DRAM accesses, and it can improve the energy efficiency and speed of the accelerator. However, conventional Static Random-Access Memory (SRAM) based solutions suffer from area constraints and leakage power at advanced technology nodes [69, 74], which is a major concern for the energy-constraint IoT domain. STT-MRAM has the potential to replace SRAM as the global buffer in high-performance AI accelerators that require large on-chip memory [57, 155]. For AI accelerators used in inference-only applications, the pre-trained weights need to be stored on-chip. As conventional embedded Flash storage suffers from scalability and reliability issues at advanced nodes [74], emerging memory-based solutions are required for AI accelerators. As analyzed in detail in [75], because of weight reuse in Deep Learning, radiation-induced soft errors in the memory block of the accelerator can impact the accuracy of AI models. This is especially a concern for safety-critical applications such as autonomous vehicles with rigid FIT requirements [75], and STT-MRAM can be a better option for these types of applications.