### **RESEARCH**

# Modeling and Parasitic Extraction of the MM9 Transistor for GHz/THz CMOS RF Circuit Design

Aswini Kumar Gadige<sup>1</sup> • Paramesha<sup>1</sup>

Received: 22 August 2024 / Accepted: 17 November 2024 / Published online: 21 December 2024 © The Author(s), under exclusive licence to Springer Science+Business Media, LLC, part of Springer Nature 2024

#### Abstract

The goal of this paper is to decrease the number of complicated mathematical calculations for extracting the values of parasitic components and to examine the RF behavior of CMOS circuits rapidly by proposing a simple, bias-independent, three-capacitor  $\pi$  network small signal equivalent circuit of the sub-micrometer Philips MOS Model 9 (MM9) for high-frequency operations in the range of millimeter and terahertz. The performance of the suggested equivalent model and MM9 is compared by analyzing the simulated S-parameters in three distinct conditions: zero bias, active region, and saturation region. The frequency range considered for the analysis is from 1 GHz to 1 THz. Furthermore, the suggested model's suitability is shown by its implementation in a bilateral buffer amplifier operating at frequencies 1 GHz, 10 GHz, 50 GHz, and 100 GHz. The simulation results of the suggested equivalent model have shown excellent agreement with MM9, ranging from 10 GHz to frequencies exceeding 1 THz.

Keywords Philips MM9 · Millimeter wave · Terahertz · Small-signal model

## 1 Introduction

The most recent advancements in CMOS technology have made it feasible to utilize CMOS RFICs for millimeter wave and terahertz operations [1–5]. While CMOS is well known for its subpar performance as an RFIC technology, it does include intriguing characteristics that make it suitable for developing competitive radio transceiver systems. One of the key benefits is the ability to combine RF analog circuits with large-scale digital circuits, as well as the significant potential for affordable. One significant challenge in designing CMOS RFICs is the inadequate availability of accurate models that can accurately anticipate the behavior of devices operating at millimeter wave frequencies and the terahertz range. To forecast circuit performance and improve the first-time successful tape out, MOSFET model accuracy is essential [6].

Responsible Editor: T. Xia

✓ Aswini Kumar Gadige aswiniselectronics@gmail.com

Paramesha parameshap@cuk.ac.in

Department of Electronics and Communication Engineering, Central University of Karnataka, Gulbarga, India Compact MOS models like MM9 (MOS model 9), BSIM3v3 [7], and EKV [8] are often used for analog and digital circuit design. However, when these models are used at very high frequencies (VHF) without considering parasitic effects, the results are erroneous.

The Philips compact MOS Model 9 (MM9) is a physicsbased analytical model used for electrical circuit modeling. It is highly suitable for both analog and digital applications. It provides an excellent description of the electrical characteristics in all relevant regions of transistor operation such as the sub-threshold current, the substrate current and the output conductance. The MM9 model is the first compact MOS model to successfully meet the benchmark tests for analog models. Since the 1970s, simulation and testing of numerous small signal equivalent circuits has been developed [9–12] to predict the correctness of the MOSFET behavior. MM9's two port common source-bulk equivalent circuit [13] consists of 7 capacitors, 3 resistors and 8 dependent sources. To reach a GHz frequency range of up to 12 GHz for 0.25 µm CMOS RF circuit design, three more capacitors are included into the MOS model 9 [14, 15]. This is necessary owing to the presence of connection metal in a multi-finger arrangement, which ensures accurate alignment between measured and simulated data. Here the values of the parasitic components have been calculated by using the measured

S-parameters at 18 different bias points. S-parameters fitting and capacitance measurements have been performed adding an extra gate-bulk zero bias capacitance to the MOSFET equivalent circuit to increase the accuracy of MOS Model 9 up to 10GHz [16]. In the sub-circuit of 0.25 μm CMOS, a substrate network [17] is included to mitigate signal coupling at high frequencies (up to 10GHz) between the drain, source, and bulk. This network allows for the extraction of the equivalent model's components using Y parameters and transit frequency. A parallel gate-drain branch is included to account for the effects of parasitic gate-drain coupling at high frequencies up to 40 GHz, as well as the influence of substrate loss, terminal resistances, and inductances. A novel extraction process called cold extraction has been devised to extract all extrinsic parasitic components from zero bias Z-parameters and intrinsic components from ON state Y-parameters [18]. The MOSFET equivalent model includes the additional gate-bulk capacitance to accurately represent the gate-bulk coupling effect. To determine the parasitic components up to 60 GHz, the S-parameters undergo standard open short de-embedding [19]. Transfer length method and dual-sweep combinational transconductance technique are combined with channel resistance method to extract the Gate Bias-Dependent Parasitic Resistances of MOSFET [20]. Focusing on precise substrate parasitic modeling up to 40 GHz utilizing a curve-fitting technique to improve model accuracy while accounting for the parasitic effects introduced at high frequencies in order to extract the MOS-FET extrinsic parameters for small-signal modeling [21]. A high-frequency small-signal MOSFET model till 10 GHz is presented by utilizing the linear regression technique carried out by Y parameter analysis, substrate-related parameters, and nonreciprocal capacitors [22]. A RF MOSFET model is suggested to extract the drain-to-source conductance, the subthreshold swing, the source/drain resistance, the effective gate length, and the threshold voltage up to 60 GHz using the experimental S-parameters in linear region [23]. The aforementioned methods use multiple voltage bias testing

conditions, rough assumption of frequency to calculate S parameters, diverse passive elements, bias-dependent components, and dependent current sources to accurately examine the characteristics of MOSFETs, with a maximum frequency limit of Giga Hertz range. To extract the values of parasitic components, it is essential to use Kirchhoff's Current Law (KCL) and Kirchhoff's Voltage Law (KVL), which include complicated real/imaginary equations for two-port network S parameters. These equations need intricate calculations based on the assumption of frequency.

This research presents a simple small signal equivalent model to MM9 for precise estimation of NMOS (n channel MOS transistor) S-parameters over a broad range of frequencies from GHz to terahertz and effectively addresses the aforementioned issues. Here, a small signal equivalent model with just three bias-independent capacitors is proposed for all three conditions, such as zero bias, active, and saturation operating regions, which facilitate the quick extraction of parasitic components and the easy analysis of RF CMOS behavior at millimeter and terahertz frequencies with minimal, simple and quick calculations. In order to simplify the mathematical equations, the magnitudes of S and Y parameters are used instead of the real and imaginary portions for calculating the values of parasitic components.

# 2 Proposed Small Signal Equivalent Model

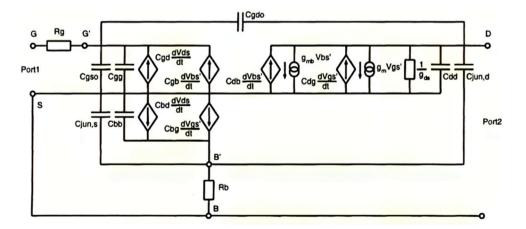

The small signal equivalent circuit of Philips Mos Model 9 model is shown in the Fig. 1 [11]. Here the MOSFET is represented in two port common source-bulk configuration, includes the overlap capacitances (Cgso and Cdgo), terminal resistances (Rg, Rb), junction capacitances (Cjun,s and Cjun,d), and intrinsic capacitances (Cgg, Cbb, Cgd, Cgb, Cbd, Cbg, and Cdd). Considering the cold extraction method (Vgs = Vds = 0) and neglecting the influence of terminal resistors (Rb = Rg = 0) at higher frequencies, the impact of dependent current

Fig. 1 Equivalent circuit of MOS MODEL 9 in two-port common source-bulk configuration

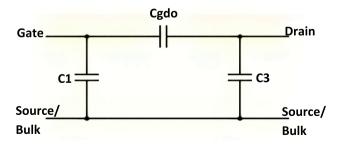

sources, Cjun,s and Cbb on the circuit will be negligible. Finally the small signal equivalent circuit is remained with Cgso, Cgg, Cdd, Cjun,d and Cgdo passive elements and these capacitors equivalent circuit is shown in Fig. 2 as a proposed 3 capacitors  $\pi$  network small signal equivalent model. The readily defined Y (admittance) matrix of the  $\pi$  network makes analysis and simulations easier, particularly in RF and microwave design. Since it can be used directly to calculate voltage and current relationships across the network and is compatible with network cascading, which is typical in RF amplifier designs, a Y-matrix in many SPICE-based tools makes the simulation process easier. This is a significant benefit for designers who analyze and optimize RF circuits using SPICE or other simulation software.

where, C1 is the parallel combination of Cgso and Cgg. i.e. C1=Cgso+Cgg, C3 is the parallel combination of Cdd and Cjun,d. i.e. C3=Cdd+Cjun,d.

The admittance matrix (Y) of the proposed  $\pi$  equivalent capacitive network is

$$Y = \begin{bmatrix} jwC1 + jwCgdo & -jwCdgo \\ -jwCdgo & jwC3 + jwCdgo \end{bmatrix} = 1/Z$$

where, w is the angular frequency and Z is the impedance matrix.

The two-port vector network analyzer is used to measure the S-parameters of the Philips MM9 MOSFET, rather than impedance/admittance parameters. Therefore, it is necessary to transform the S parameters into Z parameters initially. In the case of a typical two-port network, the conversion process can be accomplished using eqs. (1)–(4), with Zo representing the characteristic impedance of 50  $\Omega$  [24].

$$Z_{11} = \left[ \frac{(1+S11)(1-S22) + S12S21}{(1-S11)(1-S22) - S12S21} \right] Zo$$

(1)

$$Z_{12} = \left[ \frac{2S12}{(1 - S11)(1 - S22) - S12S21} \right] Zo$$

(2)

Fig. 2 Proposed capacitive equivalent circuit of MOS MODEL 9 at high frequencies

$$Z_{21} = \left[ \frac{2S21}{(1 - S11)(1 - S22) - S12S21} \right] Z0$$

(3)

$$Z22 = \left[ \frac{(1 - S11)(1 + S22) + S12S21}{(1 - S11)(1 - S22) - S12S21} \right] Z0$$

(4)

Our innovative technique involves characterizing the parasitic/intrinsic capacitances of a four-terminal Philips MM9 NMOSFET via two-port S-parameters measurement is as the following:

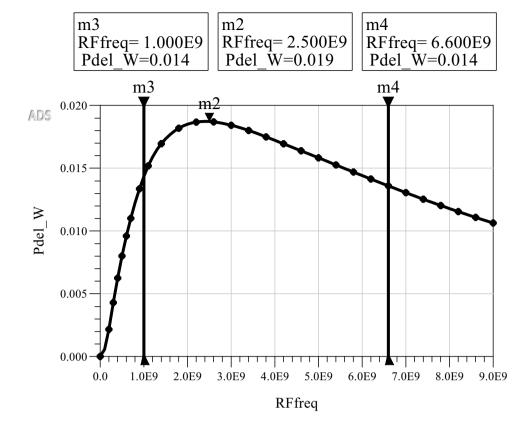

Step 1: Perform S-parameter measurements on the common source-bulk configuration of  $0.25 \times 400 \mu m$  MM9 at a lower cutoff frequency of 1 GHz, as depicted in Fig. 3;

Step 2: Transform the recorded magnitudes of S-parameters into Z-parameters using eqs. (1)–(4), and subsequently convert them into Y-parameters;

Step 3: The intrinsic/parasitic capacitances C1, Cdgo, and C3 depicted in Fig. 2 are extracted by utilizing the calculated Y-parameters and the admittance matrix Y at frequency 1 GHz.

The parameters obtained from the three steps mentioned above are presented in Table 1. The entire MM9 small signal model, which consists of three resistors, eight dependent current sources, and seven capacitors, is perfectly replaced by the suggested three capacitors  $\pi$  network small signal equivalent model with extracted parasitic capacitances at high frequency.

## 3 Results

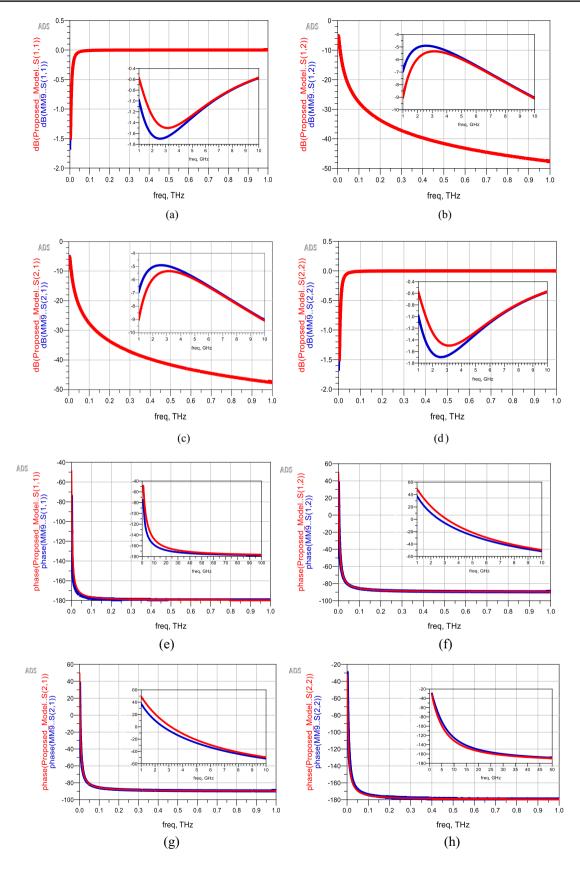

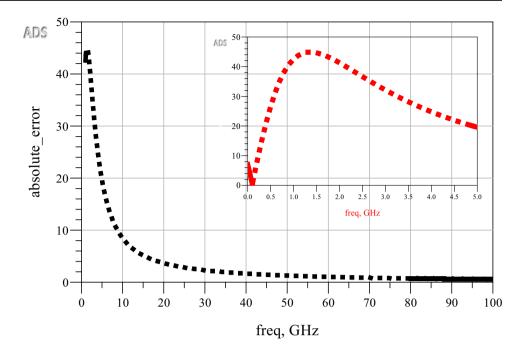

Figure 4 displays the simulated S-parameters of the MM9 model and the suggested capacitive  $\pi$  network equivalent model at zero bias, allowing for a direct comparison. Here the Philips MOS Model 9 NMOS transistor and suggested equivalent model are used in common source configuration with a source and load impedance of 50  $\Omega$ . Figure 4(a)-(d), shows the main (0.001-1 THz) and sub graphs (1-10 GHz)of input reflection (S11), reverse transmission (S12), forward transmission (S21) and output reflection (S22) coefficients respectively in decibels. Similarly, Fig. 4(e)-(h), shows the phase angle of these S parameter coefficients in degree. To draw the quick conclusion from these eight graphs, an absolute error is calculated as per eq. (1) and represented in Fig. 5. The following observations have been made based on this figure. 1. From 0.52 at 0.1 GHz to 44.88 at 1.4 GHz, the error is increasing. The poor electrical performance has been noted at low frequencies because capacitors tend to restrict low-frequency signals due to their frequency-dependent impedance, even though there is less inaccuracy at 0.1 GHz with regard to S parameters. 2. After 1.4 GHz; error begins to decrease till 0.54 at

Fig. 3 Philips MM9 NMOS output power (Pdel\_W) in watts with lower and upper cutoff frequencies

Table 1 Simulated S-parameters, calculated Y-parameters and extracted parasitic capacitances

| Magnitudes of MM9<br>S-parameters at 1 GHz |       |       | Conver<br>Y-parar | ted<br>neters (mS | 5)   | Extracted Parasitic capacitances (pF) |     |      |      |      |

|--------------------------------------------|-------|-------|-------------------|-------------------|------|---------------------------------------|-----|------|------|------|

| IS11I                                      | IS12I | IS21I | IS22I             | Y11               | Y12  | Y21                                   | Y22 | C1   | Cdgo | C2   |

| 0.893                                      | 0.451 | 0.451 | 0.893             | 9.9               | 4.23 | 4.23                                  | 9.9 | 0.82 | 0.67 | 0.32 |

100 GHz. These findings suggest that the proposed model can be used in the place of MM9 at higher frequencies, especially starting at 10 GHz.

Absolute error = |True Value - Measure Value|

$$= \left| \sum MM9 \text{ S parameters} - \sum \text{proposed model S parameters} \right|$$

(1)

Table 2 sows the comparison of S-parameters between MM9 NMOS and the proposed equivalent model in terms of the linear and saturation operating regions at a frequency of 100GHz. To maintain the linear operating region, the gate-source terminals connect to a 5 V DC and 20 dBm AC power source, while the drain-source terminals are kept at a 0.5 V DC level. Similarly, to maintain the saturation operating region, the gate-source terminals connect to a 0.1 V DC and 1 dBm AC power source, while the drain-source terminals are kept at a 5 V DC level.

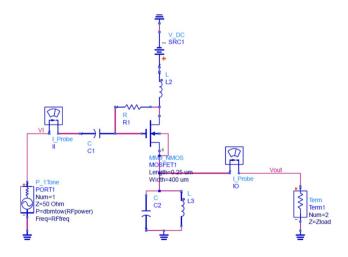

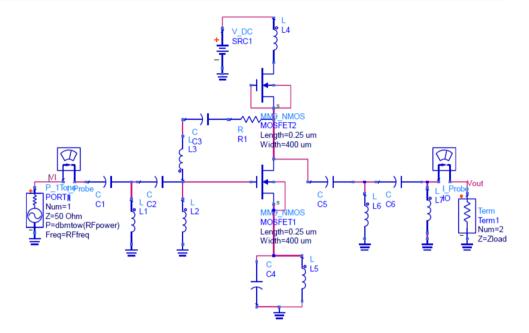

## 4 Circuit Example

In 5G, IOT, Satellite and Radar applications, transceivers plays the crucial role by buffering signals in bidirectional for facilitating the full duplex communication. As a part of transceiver, Bilateral Buffer Amplifier (BBA) remains an essential component. A single transistor BBA, as depicted in Fig. 6, and a two transistors wideband cascode bilateral buffer amplifier [25], as depicted in Fig. 7, are taken into consideration in order to evaluate the performance of the suggested equivalent model at the circuit level and application point of view. As indicated in Tables 3 and 4, respectively, these two circuits are designed and simulated using the MM9 NMOS (0.25  $\times$  400  $\mu$ m) and the proposed  $\pi$  network capacitors equivalent model for comparison in terms of S-parameters in decibels and phase angle of S-parameters in degrees. Table 5 compares electrical performance metrics of amplifier such as peak source current (Is), peak load

Fig. 4 Simulated S-parameters of the MM9 NMOS and Proposed capacitive  $\pi$  network equivalent model at zero bias

**Fig. 5** S parameters Absolute error of proposed model

Table 2 S-parameters comparison between the proposed equivalent model and the MM9 NMOS in terms of linear and saturation region at 100 GHz

|            | Linear op               | erating regi | on    |        |        |       |       |        |  |  |

|------------|-------------------------|--------------|-------|--------|--------|-------|-------|--------|--|--|

| MM9        | S11                     | S12          | S21   | S22    | ∠S11   | ∠S12  | ∠S21  | ∠S22   |  |  |

| NMOS       | -0.009                  | -26.9        | -26.9 | -0.009 | -177.4 | -86.1 | -86.1 | -174.8 |  |  |

|            | Saturation region       |              |       |        |        |       |       |        |  |  |

|            | S11                     | S12          | S21   | S22    | ∠S11   | ∠S12  | ∠S21  | ∠S22   |  |  |

|            | -0.002                  | -33.3        | -33.3 | -0.002 | -178.7 | -87.5 | -87.5 | -176.9 |  |  |

| Proposed   | Linear operating region |              |       |        |        |       |       |        |  |  |

| Equivalent | S11                     | S12          | S21   | S22    | ∠S11   | ∠S12  | ∠S21  | ∠S22   |  |  |

| model      | -0.007                  | -27.6        | -27.6 | -0.007 | -176.4 | -85.5 | -85.5 | -174.7 |  |  |

|            | Saturation region       |              |       |        |        |       |       |        |  |  |

|            | S11                     | S12          | S21   | S22    | ∠S11   | ∠S12  | ∠S21  | ∠S22   |  |  |

|            | -0.005                  | -32.6        | -32.6 | -0.005 | -178.4 | -86.5 | -86.5 | -176.7 |  |  |

Fig. 6 Single stage Buffer Amplifier

voltage (Vo), and peak load current (Io) at various frequencies with source power of 10 dBm. Four distinct frequencies i.e. 1 GHz, 10 GHz, 50 GHz, and 100 GHz that roughly span L-band to W-band have been used in this comparative analysis. Error % is computed for MM9 and the proposed model at the circuit level for improved comparison and better conclusion. The error percentage is often determined using eq. (2), and similarly, the percentage error tabulated in 3, 4, and 5 is computed using eq. (3).

$$Error\% = \frac{|True\ Value - Measured\ Value|}{True\ Value} \times 100$$

(2)

$$= \frac{\left| \sum \text{MM9 Parameters} - \sum \text{Proposed Model Parameters} \right|}{\sum \text{MM9 Parameters}} \times 100$$

(3)

**Fig. 7** Cascode Buffer Amplifier

Table 3 Comparison of S-parameters between the bilateral buffer amplifier (BBA) with MM9 NMOS and the proposed equivalent model at various frequencies

| Signle stage | Bilateral B                          | uffer Amp | lifier  |         |          |             |         |         |       |

|--------------|--------------------------------------|-----------|---------|---------|----------|-------------|---------|---------|-------|

| Frequency    | BBA with                             | n MM9 NM  | IOS     |         | BBA with | n Equivalen | t Model |         | Error |

| (GHz)        | S11(dB)                              | S12(dB)   | S21(dB) | S22(dB) | S11(dB)  | S12(dB)     | S21(dB) | S22(dB) | (%)   |

| 1            | -9.16                                | -0.77     | -0.77   | -8.70   | -4.85    | -1.76       | -1.76   | -4.78   | 32.2  |

| 10           | -20.60                               | -0.04     | -0.04   | -20.60  | -18.00   | -0.07       | -0.07   | -18.00  | 12.4  |

| 50           | -31.57                               | -0.00     | -0.00   | -31.57  | -29.61   | -0.00       | -0.00   | -29.61  | 6.2   |

| 100          | -32.05                               | -0.00     | -0.00   | -32.04  | -30.95   | -0.00       | -0.00   | -30.95  | 3.4   |

| Cascode Wi   | Wide band Bilateral Buffer Amplifier |           |         |         |          |             |         |         |       |

| Frequency    | BBA with                             | n MM9 NM  | IOS     |         | BBA with | n Equivaler | t Model |         | Error |

| (GHz)        | S11(dB)                              | S12(dB)   | S21(dB) | S22(dB) | S11(dB)  | S12(dB)     | S21(dB) | S22(dB) | (%)   |

| 1            | -6.66                                | -4.67     | -4.67   | -4.74   | -1.74    | -8.16       | -8.16   | -6.24   | 17.1  |

| 10           | -19.42                               | -0.05     | -0.05   | -19.41  | -20.25   | -0.04       | -0.04   | -20.24  | 4.2   |

| 50           | -16.49                               | -0.09     | -0.09   | -16.49  | -16.71   | -0.09       | -0.09   | -16.71  | 1.5   |

| 100          | -23.46                               | -0.02     | -0.02   | -23.46  | -23.70   | -0.01       | -0.01   | -23.70  | 1.6   |

**Table 4** Comparison of phase angle of S-parameters between the BBA with MM9 NMOS and the proposed equivalent model at various frequencies

| Signle stage B | Bilateral Bu | ffer Ampl | ifier |        |          |            |           |        |       |

|----------------|--------------|-----------|-------|--------|----------|------------|-----------|--------|-------|

| Frequency      | BBA with     | h MM9 N   | MOS   |        | BBA with | h Equivale | nt Model  |        | Error |

| (GHz)          | ∠S11         | ∠S12      | ∠S21  | ∠S22   | ∠S11     | ∠S12       | ∠S21      | ∠S22   | (%)   |

| 1              | 81.94        | 129.8     | 129.8 | 2.27   | 106.6    | 145.0      | 145.0     | 3.36   | 16.3  |

| 10             | -77.85       | 12.83     | 12.83 | -76.27 | -77.05   | 14.17      | 14.17     | -75.47 | 3.3   |

| 50             | -86.91       | 2.14      | 2.14  | -88.74 | -86.30   | 2.52       | 2.52      | -88.37 | 1.0   |

| 100            | -88.49       | 0.39      | 0.39  | -90.70 | -88.03   | 0.58       | 0.58      | -90.47 | 0.3   |

| Cascode Bilat  | eral Buffer  | Amplifie  | :     |        |          |            |           |        |       |

| Frequency      | BBA with     | h MM9 N   | MOS   |        | BBA with | h Equivale | ent Model |        | Error |

| (GHz)          | ∠S11         | ∠S12      | ∠S21  | ∠S22   | ∠S11     | ∠S12       | ∠S21      | ∠S22   | (%)   |

| 1              | -68.7        | 103.1     | 103.1 | 19.0   | -51.0    | 134.4      | 134.4     | 63.8   | 80.0  |

| 10             | 168.7        | 38.2      | 38.2  | 87.8   | 179.0    | 39.3       | 39.3      | 79.5   | 1.2   |

| 50             | 119.9        | 27.4      | 27.4  | 114.9  | 120.2    | 27.6       | 27.6      | 114.9  | 0.2   |

| 100            | 105.0        | 13.1      | 13.1  | 101.8  | 105.1    | 13.2       | 13.2      | 101.3  | 0.08  |

|                |              |           |       |        |          |            |           |        |       |

Table 5 Comparison of performance parameters between the BBA with MM9 NMOS and the proposed equivalent model at various frequencies

| Signle stage Bilat | teral Buffer Amplif | ìer      |        |              |                           |        |      |  |

|--------------------|---------------------|----------|--------|--------------|---------------------------|--------|------|--|

| Frequency          | BBA with M          | IM9 NMOS |        | BBA with Equ | BBA with Equivalent Model |        |      |  |

| (GHz)              | Vo(mV)              | Io (mA)  | Is(mA) | Vo(mV)       | Io (mA)                   | Is(mA) | (%)  |  |

| 1                  | 917                 | 18       | 20     | 812          | 16                        | 25     | 15.4 |  |

| 10                 | 971                 | 19       | 20     | 960          | 19                        | 19     | 1.1  |  |

| 50                 | 999                 | 20       | 20     | 998          | 20                        | 20     | 0.09 |  |

| 100                | 1000                | 20       | 20     | 999          | 20                        | 20     | 0.09 |  |

| Cascode Bilateral  | l Buffer Amplifier  |          |        |              |                           |        |      |  |

| Frequency          | BBA with M          | IM9 NMOS |        | BBA with Equ | Error                     |        |      |  |

| (GHz)              | Vo(mV)              | Io (mA)  | Is(mA) | Vo(mV)       | Io (mA)                   | Is(mA) | (%)  |  |

| 1                  | 337                 | 7        | 9      | 332          | 7                         | 15     | 0.3  |  |

| 10                 | 996                 | 20       | 20     | 993          | 20                        | 20     | 0.2  |  |

| 50                 | 984                 | 20       | 21     | 985          | 20                        | 21     | 0    |  |

| 100                | 997                 | 20       | 20     | 997          | 20                        | 20     | 0    |  |

The following inferences can be made by comparing the S parameters in degrees, decibels, and electrical performance metrics from the tables above with respect to error percentage. (1) At higher frequencies, such as centimeter wave (>10GHz), millimeter wave (30–300 GHz), and terahertz frequency (0.1-10 THz) range, the suggested equivalent model is effectively replicating the MM9, as evidenced by the error percentage decreasing as the operating frequency increases and maintaining a considerable error % from 10 GHz onward. (2) This operating frequency is not recommended for the suggested model since the largest error % is shown at the lower cutoff frequency of MM9, which is 1 GHz. (3) Although multi-transistor or cascode buffer amplifiers are advantageous at high frequencies, they will pose issues at low frequencies due to the addition of poles to the frequency response. This can cause unfavorable phase shifts and instability in systems, which is why the lowest frequency of 1 GHz exhibits the highest percentage inaccuracy i.e., 80% in terms of phase angles of S parameters. But for higher frequencies (> 10 GHz), a positive improvement is noted comparing with single transistor buffer amplifier. (4) The error percentage in single and multi transistor buffer amplifiers is almost negligible at 50 and 100 GHz. Finally, it is determined that the proposed simple small signal equivalent model can be replaced with the MM9 MOSFET for easy and quick analysis of CMOS circuits at high frequencies, such as in millimeter and terahertz applications.

## 5 Future Scope

The proposed MOSFET small signal equivalent model is unsuitable for applications where the gain requirement is greater than 0 dB because it only includes passive components (capacitors). To date, the aforementioned gain need has been satisfied in all literature by using a dependent current source that is not portable. However, there is a possibility that when Schottky diodes are used in the suggested model, the gain could rise over 0 dB, as in the Cockcroft-Walton Voltage Multiplier [26].

### 6 Conclusion

A novel and concise small signal equivalent model has been introduced to precisely forecast the RF characteristics of Philips MOS Model 9 transistor operating at millimeter and terahertz frequencies. The proposed model consists of three capacitors arranged in a pi network configuration. A  $0.25 \times 400~\mu m$  CMOS technology model has been developed. This model provides high accuracy over a broad range of frequencies especially for applications where the gain requirement is less than or equal to 0 dB. Ultimately, an assessment was carried out at the circuit level using single and multi transistor bilateral buffer amplifiers. The outcomes indicate a favorable correspondence between the suggested model and MM9 from 10 GHz onwards.

Supplementary Information The online version contains supplementary material available at https://doi.org/10.1007/s10836-024-06154-2.

Funding No funding was received.

#### **Declarations**

**Competing Interests** The authors declare no competing interests.

## References

- Qian Y, Shen Y, Hu S (2023) Millimeter-wave CMOS lownoise amplifier with high gain and compact footprint. IEEE Microw Wirel Technol Lett 33(6):699–702. https://doi.org/10. 1109/LMWT.2023.3246166

- Zheng Yan, Jixin Chen, Zhe Chen, Dawei Tang, Zekun Li, Rui Zhang, Peigen Zhou, and Wei Hong, "A D-band power amplifier with 60-GHz large-signal bandwidth and 7.6% peak PAE in 28-nm CMOS," IEEE Microw Wirel Technol Lett, vol. 34, no. 5, pp. 540–543, May 2024, doi: https://doi.org/10.1109/LMWT.2024.3380441

- Q.Zhong, W.-Y.Choi, D.-Y.Kim, Z. Ahmad, R.Xu, Y. Zhang, R.Han, S. Kshattry, N.Sharma, Z.-Y.Chen, D. Shim, SnSankaran, E.-Y.Seok, C. Mao, F.C.DeLucia, J.P.McMillan, C.F.Neese, I.Kim, I.Momson, P.Yelleswarapu, S.Dong, B.Pouya, P.Byreddy, Z.Chen, Y.Zhu, S.Ghosh, T.Dinh, F.Jalalibidgoli, J. Newman, K.K.O, "CMOS terahertz receivers," 2018 Proc.IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 2018, pp. 1–8, doi: https://doi.org/10.1109/CICC.2018.8357054

- K. Jokiniemi, K. Ryynänen, J. Vähä, E. Kankkunen, K. Stadius and J. Ryynänen, "55–100-GHz Enhanced Gilbert Cell Mixer Design in 22-nm FDSOI CMOS," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, doi: https://doi. org/10.1109/TVLSI.2024.3454350

- Moran Guizan C, Baumgartner P, Heinen S, Lauritano M (2024) Millimeter-wave tunable impedance matching network in an advanced CMOS process. IEEE Trans Microw Theory Tech 72(8):4590–4596. https://doi.org/10.1109/TMTT.2024. 3361992

- Kang K, Lin F, Pham D-D, Brinkhoff J, Heng C-H, Guo YX, Yuan X (2010) A 60-GHz OOK receiver with an on-Chip antenna in 90 nm CMOS. IEEE J Solid State Circuits 45(9):1720–1731. https://doi.org/10.1109/JSSC.2010.2053095

- Cheng Y, Jeng M-C, Liu Z, Huang J, Chan M, Chen K, Ko PK, Hu C (1997) A physical and scalable I-V model in BSIM3v3 for analog/digital circuit simulation. IEEE Trans Electron Devices 44(2):277–287. https://doi.org/10.1109/16.557715

- Enz CC, Krummenacher F, Vittoz EA (1995) An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. Analog Integr Circ Sig Process 8:83–114. https://doi.org/10.1007/ BF01239381

- Lee S, Yu HK, Kim CS, Koo JG, Nam KS (1997) A novel approach to extracting small-signal model parameters of silicon MOSFET's. IEEE Microw Guided Wave Lett 7(3):75–77. https://doi.org/10.1109/75.556037

- Liu S, Nagel LW (1982) Small-signal MOSFET models for analog circuit design. IEEE J Solid State Circuits 17(6):983– 998. https://doi.org/10.1109/JSSC.1982.1051852

- Chang K-M, Wang H-P (2004) A new small-signal MOSFET model and parameter extraction method for RF IC's application. Microelectron J 35(9):749–759. https://doi.org/10.1016/j. mejo.2004.06.001

- Vandamme EP, Schreurs D, van Dinther C, Badenes G, Deferm L (2002) Development of a RF large signal MOSFET model, based on an equivalent circuit, and comparison with the BSIM3v3 compact model. Solid State Electron 46(3):353–360. https://doi.org/10.1016/S0038-1101(01)00108-3

- Klaassen DBM, Nauta B, Vanoppen RRJ (2001) RF modelling of MOSFETs. In: Sansen W, van de Plassche RJ, Huijsing JH (eds) Analog circuit design. Springer, Boston, MA. https://doi. org/10.1007/978-1-4613-1443-1\_1

- Iversen CR (2001) An embedded MOS model 9 for CMOS RF circuit design. Microw J:22–40

- C. R. Iversen, "A MOS Model 9 Extension for GHz CMOS RF Circuit Design," 2001 Proc.31st European Microwave Conference, London, UK, 2001, pp. 1–4, doi: https://doi.org/10.1109/ EUMA.2001.339129

- Saijets J, Andersson M, Åberg M (2002) A comparative study of various MOSFET models at radio frequencies. Analog Integr Circ Sig Process 33:5–17. https://doi.org/10.1023/A: 1020376811342

- Enz C, Cheng Y (2000) MOS transistor modeling for RF IC design. IEEE J Solid State Circuits 35(2):186–201. https://doi. org/10.1109/4.823444

- 18. Yang T, Zhang L, Wang Y (2010) Accurate small signal modeling and extraction of silicon MOSFET for RF IC application. Solid State Electron 54(11):1312–1318. https://doi.org/10.1016/j.sse.2010.06.025

- Cao Y, Zhang W, Fu J, Wang Q, Liu L, Guo A (2019) A complete small-signal MOSFET model and parameter extraction technique for millimeter wave applications. IEEE J Electron Devices Soc 7:398–403. https://doi.org/10.1109/JEDS.2019. 2900202

- Lee J, Bae H, Hwang JS, Ahn J, Jang JT, Yoon J, Choi S-J, Kim DH, Kim DM (2015) Modeling and separate extraction technique for gate Bias-dependent parasitic resistances and overlap length in MOSFETs. IEEE Trans Electron Devices 62(3):1063–1067. https://doi.org/10.1109/TED.2015.2388704

- Wang SC, Huang GW, Chen KM, Peng AS, Tseng HC, Hsu TL (2004) A practical method to extract extrinsic parameters for the silicon MOSFET small signal model. Proc NSTI-Nanotech 2:151–154

- Kwon I, Je M, Lee K, Shin H (2002) A simple and analytical parameter-extraction method of a microwave MOSFET. IEEE Trans Microw Theory Tech 50(6):1503–1509. https://doi.org/ 10.1109/TMTT.2002.1006411

- Zárate-Rincón F, Torres-Torres R, Murphy-Arteaga RS (2015)

Consistent DC and RF MOSFET modeling using an S-parameter measurement-based parameter extraction method in the linear region. IEEE Trans Microw Theory Tech 63(12):4255–4262. https://doi.org/10.1109/TMTT.2015.2495363

- Frickey DA (1994) Conversions between S, Z, Y, H, ABCD, and T parameters which are valid for complex source and load impedances. IEEE Trans Microw Theory Tech 42(2):205–211. https://doi.org/10.1109/22.275248

- A. Megej, K. Beilenhoff, C. Sydlo and H. L. Hartnagel, "Fully Monolithically Integrated Wide-Band RF-Source," 2001 Proc.31st European Microwave Conference, London, UK, 2001, pp. 1–4, doi: https://doi.org/10.1109/EUMA.2001.339154

- N. Rani, J. Kaur, H. Bhatia, S. S. Saini, R. Kaur and E. Sidhu,

"Design and performance analysis of Cockroft-Walton Voltage Multiplier (CWVM) energy harvesting for low power applications,"

2017 Progress In Electromagnetics Research Symposium - Spring (PIERS), St. Petersburg, Russia, 2017, pp. 2131–2136, doi: https://doi.org/10.1109/PIERS.2017.8262103

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

**Aswini Kumar Gadige** received the Bachelor's and Master's degrees in 2007 and 2011 from Jawaharlal Nehru Technological University Hyderabad and Kakinada, India respectively. From

2011-2022 he worked as an Assistant Professor in various Engineering Colleges. Currently he is pursuing his Ph.D. degree at Electronics and Communication Engineering Department, School of Engineering Central University of Karnataka, Kalaburagi, India. His research interests include millimeter wave technology and VLSI.

Paramesha received the Bachelor's degree from University of Mysore, India, the Masters degree from the Indian Institute of Technology (IIT) Varanasi, India, and the Ph.D. degree from the IIT Kharagpur. From 1990 to 2020, he worked as a Faculty member in the Electronics and Telecommunication Engineering Department, College of Engineering, India, at various positions. Since 2023, he has been an Associate Professor and Dean at School of Engineering, Central University of Karnataka, Kalaburagi, India. Dr. Paramesha has published over 33 papers in technical journals and conferences. His research interests include millimeter wave technology.