#### RESEARCH

# **ADC Dynamic Parameter Testing Scheme Under Relaxed Conditions**

Jun Yuan<sup>1</sup> · Yuyang Zhang<sup>1</sup> · Liangrui Zhang<sup>1</sup> · Shuaiqi Hou<sup>1</sup> · Yukun Han<sup>1</sup>

Received: 13 December 2023 / Accepted: 2 July 2024 / Published online: 17 July 2024 © The Author(s), under exclusive licence to Springer Science+Business Media, LLC, part of Springer Nature 2024

#### **Abstract**

Traditional ADC dynamic parameter testing algorithms have high requirements for signal amplitude, purity, and coherence, which not only have high test cost but also low efficiency. Therefore, a set of ADC dynamic parameter testing algorithms was developed to relax the testing conditions. The algorithm fits the clipped signal through an interpolated fitting algorithm to obtain the residual sequence to relax the input signal amplitude limit; reduces the parameter fitting error and spectral leakage on the spurious components by data preprocessing, restores the ADC's own parameters by external noise cancellation method. Under 14-bit signal source, 5.2-V amplitude, and 0.3 leakage, the signal-to-noise ratio, signal-to-noise-and-distortion ratio, effective-number- of-bits, and total-harmonic-distortion of the 16-bit ADC chip 7606 have errors from the typical values of 0.39 dB, 0.23 dB, 0.16 bit, and 7.24 dB, respectively, which are within the manual range. The results demonstrate the functionality and robustness of the proposed relaxed testing algorithm.

$\textbf{Keywords} \ \ Analog-to-digital\ converter\ (ADC) \cdot Dynamic\ parameter\ test \cdot Incoherent\ sampling \cdot Low-precision\ signal \cdot Clipping\ identification$

#### 1 Introduction

With the rapid development of automotive electronics, medicine, and other fields and the improvement in the working speed of digital circuits, electronic systems require increasing signal sensitivity, and the signal acquisition circuit has become an important element in assessing the performance of electronic systems. Therefore, a test method for high-precision analog-to-digital converter (ADC) performance parameters has become a focus of current research [1].

Responsible Editor: T. Xia

☐ Jun Yuan yuanjun@cqupt.edu.cn

> Yuyang Zhang yuyang\_z616@163.com

Liangrui Zhang zhangliangruicqupt@163.com

Shuaiqi Hou sq\_Hou11@163.com

Yukun Han yonghg77@163.com

College of Optoelectronics Engineering, Chongqing University of Posts and Telecommunications, Chongqing 404100, China

The performance of an ADC measure the ADC's ability to digitally reconstruct the analog signal, and the commonly used test methods include sinusoidal fitting and spectral testing. The sinusoidal fitting method [2] searches for the best matching function of the ADC output sequence by minimizing the mean square deviation, and the effective -numberof-bits (ENOB) of the ADC can be measured based on the fitting residuals between the original sequence and the fitted sequence. The spectrum testing method [3] measures the ADC dynamic parameters by analyzing the relationship between fundamental, harmonic, and noise components through the Fast Fourier Transform (FFT). The latter method can test all dynamic parameters of the ADC and multifrequency testing, so it is more applicable. However, the challenge of this approach lies in the stringent requirements imposed by IEEE Standards 1057 [4] and 1241 [5] on the test conditions of ADCs, which include signal source amplitude, purity, and coherence.

In the actual spectrum test, the signal frequency and clock frequency are limited by the accuracy of the equipment, it is difficult to achieve complete synchronization, the spectrum will appear trailing, leakage and other phenomena, increasing the spurious component. Therefore, researchers typically use such methods as the addition of windows and coherent substitution to suppress spectral leakage. The window

function method [6–8] mainly enhances the continuity of the first and last ADC output sequences through the window function; thus, the signal can be expanded continuously. Different windows have different performances, usually using a window function with a narrow main flap and side flap attenuation greater than the ADC bottom noise to suppress leakage and accurately obtain spectral information. Because of the contradictory nature of the main and side flap parameters of the window function, this method requires a high degree of professionalism from testers. The coherent replacement method [9, 10] extracts the spurious components of the ADC output sequence according to the input signal parameters and coherently reconstructs the ADC output sequence using frequency transformation. This method depends on the fit of the algorithm to the input signal parameters and the accuracy of the reconstructed signal. It is difficult to achieve better suppression when the fitting error is large.

Moreover, harmonics are higher order nonlinear functions of the input amplitude, and the true parameters of the ADC can only be effectively evaluated when the input signal is equal to full scale. When tested at full scale, the amplitude is susceptible to factors such as device aging and clock jitter, resulting in clipping distortion of the waveform and the addition of extra spurious components to the spectrum. Thus, precision equipment is usually employed to control the input signal amplitude such that it is always slightly below full scale. To eliminate the dependence on external highprecision equipment, Xu et al. proposed the use of traditional code value estimation [11], parameter estimation [12], and other methods intended to reconstruct clipped signals and perform spectral analysis. However, the accuracy of the method is affected by the parameter fit and the larger the limiting cutoff range the larger the dynamic parameter test error.

In addition, the test standard also stipulates that the linearity of the signal source should be  $3 \sim 4$  bits higher than the ADC under test, which is difficult to realize due to the high cost of the signal source for high precision ADC test. In digital signal processing, average filtering [13] is typically used to reduce random noise. However, for low-precision signal sources, it fails to achieve the test results. Although the traditional noise cancellation method [14] can measure the ADC parameters under a low-purity signal source, it is

necessary to adjust the input signal amplitude repeatedly, so it is not suitable for large-scale testing.

Therefore, in order to break through the limiting conditions of spectrum testing, this paper proposes a set of engineering-friendly algorithms for dynamic testing of ADCs, which are mainly based on digital signal processing techniques to solve the problem of spectral distortion caused by amplitude limiting, phase discontinuity, and signal source noise under non-standard testing conditions.

In Section 2, the dynamic testing of ADCs based on spectral analysis is discussed. In Section 3, the proposed dynamic testing algorithm is introduced. The performances of the algorithm in simulations and experiments are discussed in Section 4. Section 5 concludes the article.

# 2 Fundamentals of ADC Dynamic Testing

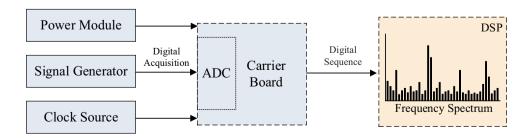

The block diagram of spectrum test of ADC dynamic parameters is shown in Fig. 1. The board captures the ADC output sequence and analyzes the power relationship between signal, noise, and harmonics in the spectrum by discrete Fourier transform to obtain the ADC dynamic parameters. The important performance parameters of the ADC include the signal-to-noise ratio (SNR), signal-to-noise-and-distortion ratio (SINAD), total-harmonic-distortion (THD), and ENOB.

The ratio of the signal power  $P_s$  to the ADC noise power  $P_{an}$  is the SNR, which reflects the internal noise of the ADC,

$$SNR = 10\lg(\frac{P_s}{P_n}). \tag{1}$$

For an ideal ADC, there is only quantization noise caused by the encoder quantization error, the quantized noise power  $P_a$  is,

$$P_{\rm q} = \frac{\int_{-0.5Lsb}^{0.5Lsb} (V_{in} - code \cdot Lsb)^2 dV_{in}}{Lsb} = \frac{(Lsb)^2}{12}.$$

(2)

Here, *code* is the ADC output code value, *Lsb* is the ADC quantization level  $F_s/2^N - 1$ , and  $F_s$  is the ADC limiting voltage.

Fig. 1 ADC dynamic test block diagram

The SNR of an ideal ADC is related to the number of ADC bits *N*.

$$SNR_{ideal} = 10 \lg(\frac{P_s}{P_q}) = 6.02N + 1.76.$$

(3)

The THD is the ratio of the total harmonic power  $P_{ah}$  of the system to the signal power  $P_s$ ,

$$THD = 10\lg(\frac{P_h}{P_s}) \tag{4}$$

which is mainly affected by the nonlinearity of the components, and is generally used to describe the degree of distortion of the waveform after the signal has been sampled by the ADC.

The ratio of total system spurious power to signal power is the SINAD.

$$SINAD = 10\lg(\frac{P_s}{P_n + P_h}) \tag{5}$$

which reflects the spurious components generated by the ADC and evaluates the overall dynamic performance of the ADC.

The ENOB is related to the spurious component of the ADC:

$$ENOB = \frac{SINAD - 1.76}{6.02}, ENOB_{ideal} = \frac{SNR - 1.76}{6.02}$$

(6)

which not only determines the resolution of the ADC but also measures the conversion quality of the signal over the Nyquist bandwidth. It is mainly used to reflect the equivalence between the actual and ideal ADC bits. The ideal ADC has no distortion, and the SNR is equal to the SINAD; therefore, its ENOB is determined only by the quantization noise.

Since the spectral spuriousness is the sum of the ADC's own spuriousness and external spuriousness. Therefore, Eqs. (1) to (6) can effectively characterize the dynamic parameters of the ADC provided that the test setup meets the standard test conditions and the spectrum is free of large-component spuriousness other than the ADC's own spuriousness.

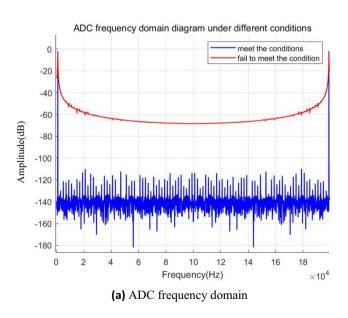

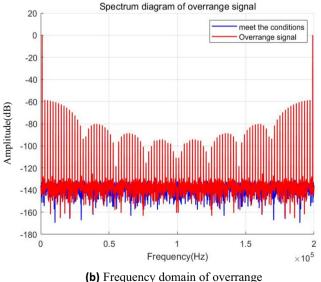

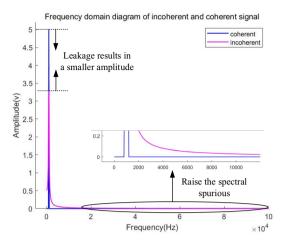

When the test setup does not meet the coherence, purity, amplitude and other conditions required for standard testing, phase discontinuity, limiting, signal source noise and other factors will not only increase the spectral noise floor and increase the amplitude of the spectral harmonic component, but also reduce the amplitude of the spectral fundamental component, as shown in Fig. 2. At this time, the spectral spurious can't be equivalent to the ADC itself spurious, the Eqs. (1) to (6) can't be correctly characterized by the ADC dynamic parameters, so it is necessary to study how to reduce the spectral leakage under non-standard conditions by means of digital signal processing and to separate the ADC own noise and external noise.

# 3 The Proposed Algorithm

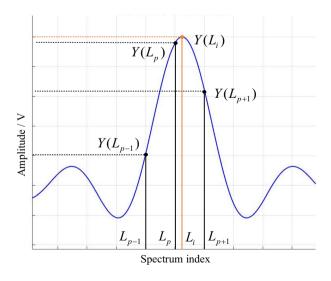

In order to realize ADC test under non-standard test conditions and reduce test difficulty and cost. This paper proposes a test algorithm based on the traditional spectrum test method to solve the problem of spectrum distortion caused by limiting,

Fig. 2 Frequency domain of ADC output sequence

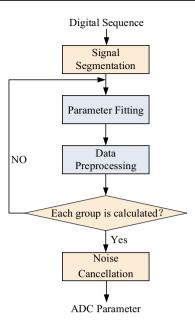

Fig. 3 Overall flowchart of spectrum testing algorithm under relaxed conditions

phase discontinuity, and source noise through digital signal processing technology. The algorithm is divided into three main parts and the overall flow is shown in Fig. 3. First, the input signal parameters are fitted by a spectral parameter estimation algorithm to obtain the residual sequence of the two. Then, the data preprocessing algorithm reduces the parameter fitting error and spectral leakage, and the dynamic parameters of the ADC with external noise are obtained through the spectrum. Finally, the noise estimation algorithm separates the intrinsic noise and random noise to offset the external noise input in order to restore the ADC's own performance parameters.

#### 3.1 Clipping Recognition and Reconstruction

The input signal model of the ADC is shown in Eq. (7).

$$x(t) = A \sin(2\pi f t + \varphi) + V_{os} + h f + n_{all}$$

(7)

where A, f, $\varphi$ , and  $V_{os}$  are the amplitude, frequency, phase, and DC of the input signal, respectively, hf is the higher-order nonlinear distortion, and  $n_{all}$  is the sum of the noise.

The digitally reconstructed sequence of the signal after sampling by the ADC is shown in Eq. (8), with x(n) representing the Nth sampling point of x(t).

$$x(n) = \begin{cases} \frac{1}{2}V_{fs}, x(n) > \frac{1}{2}V_{fs} \\ x(n), -\frac{1}{2}V_{fs} < x(n) < \frac{1}{2}V_{fs} \\ -\frac{1}{2}V_{fs}, x(n) < -\frac{1}{2}V_{fs}, n = 0, 1...N - 1 \end{cases}$$

(8)

$$Y(k) = FFT(x(n)) = \sum_{n=0}^{N-1} x(n)e^{-j2\pi \frac{nk}{N}}.$$

(9)

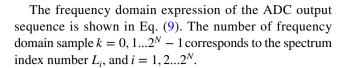

In incoherent sampling, the spectral index  $L_i$  corresponding to the fundamental frequency is a non-integer that falls between the  $L_{i-1}$  and  $L_{i+1}$  spectral lines and is affected by spectral leakage and the fence effect. The frequency estimation error caused by the fence effect is

$$f_{Err} \in (0, \frac{F_s}{2N}). \tag{10}$$

In addition to increasing the number of sampling points N to reduce the impact of the fence effect on parameter acquisition, the spectral line  $L_p$  corresponding to the largest component of the spectrum and its left and right two spectral lines  $L_{p-1}L_{p+1}$  can be used to correct the actual frequency spectral line  $L_i$ , as shown in Fig. 4. The relationship between the spectral lines is given by Eq. (11),

$$\begin{split} \eta &\in (-0.5, 0.5) : \\ \eta &= L_i - L_p, \\ \eta &- 1 &= L_i - L_{p-1}, \\ \eta &+ 1 &= L_i - L_{p+1}. \end{split} \tag{11}$$

To improve the correction effect and reduce the influence of spectral leakage before frequency correction, the classical cosine window with a good side-flap performance is used. The time and frequency domain expressions are shown in Eq. (12):

Fig. 4 Schematic diagram of spectrum interpolation

$$w(n) = \sum_{i=0}^{I-1} (-1)^{i} a_{i} \cos \frac{2\pi ni}{N},$$

$$W(\frac{2\pi k}{N}) = \sum_{i=0}^{I-1} \frac{(-1)^{i} e^{-jk\pi} \sin \frac{2k\pi}{N} \sin(k\pi) a_{i}}{2\sin \frac{\pi(k+i)}{N} \sin \frac{\pi(k+i)}{N}},$$

$$\sum_{i=0}^{I-1} a_{i} = 1, \sum_{i=0}^{I-1} (-1)^{i} a_{i} = 0.$$

(12)

Here, *I* is the number of window function terms, and  $a_i$  is the window function coefficient. When *N* is sufficiently large, then  $\cos(\theta) \cong 1$ ,  $\sin(\theta) \cong \theta$ ,  $(|\theta| \ll 1)$ .

$$x(n) = A \sin(2\pi f \frac{n}{N} + \varphi)w(n)$$

$$= \frac{A}{2j} \cdot (e^{j(2\pi f \frac{n}{N} + \varphi)} - e^{-j(2\pi f \frac{n}{N} + \varphi)})w(n),$$

$$X(\frac{2\pi k}{N}) = \frac{A}{2j}e^{j\varphi}W(\frac{2\pi (k - k_j)}{N}),$$

$$k_i = \frac{f}{F_s}N, \quad k = 0, 1...2^N - 1.$$

(13)

Equation (14) with the actual amplitude of the spectrum Y(L) yields,

$$X(\frac{2\pi L_p}{N}) = \frac{A}{2j} \sum_{i=0}^{I-1} (-1)^{i} \frac{a_i(-\eta)N \sin(-\eta\pi)}{\eta^2 - i^2\pi},$$

$$X(\frac{2\pi L_{p-1}}{N}) = \frac{A}{2j} \sum_{i=0}^{I-1} (-1)^{i} \frac{a_i(1-\eta)N \sin((1-\eta)\pi)}{(1-\eta)^2 - i^2\pi},$$

$$X(\frac{2\pi L_{p+1}}{N}) = \frac{A}{2j} \sum_{i=0}^{I-1} (-1)^{i} \frac{a_i(-1-\eta)N \sin((-1-\eta)\pi)}{(-1-\eta)^2 - i^2\pi}.$$

(14)

By substituting the sampled discrete points  $L_p$ ,  $L_{p-1}$ , and  $L_{p+1}$  into Eq. (13) yields the ideal amplitude corresponding to the spectral line.

Setting the amplitude ratio function [15] and associating Eq. (14) with the actual amplitude of the spectrum yields,

$$\xi = \frac{Y(L_{p+1}) - Y(L_{p-1})}{Y(L_p)} = \frac{X(L_{p+1}) - X(L_{p-1})}{X(L_p)}, \eta = f^{-1}(\xi)$$

(15)

$$\eta = \frac{Q(Y(L_{p-1}) - Y(L_{p+1}))}{(2Y(L_p) + Y(L_{p+1}) + Y(L_{p-1}))}, \quad \eta \in (-0.5, 0.5)$$

$$L_i = (L_p + \eta), \quad f = \frac{F_s}{N}(L_i - 1).$$

(16)

The amplitude and phase parameters are obtained using a three-parameter fitting algorithm for a sine wave with minimum residuals. The expression for the fitted sinusoidal function is,

$$x(\hat{n}) = A_0 \cos(2\pi \hat{f} \frac{n}{N}) + B_0 \sin(2\pi \hat{f} \frac{n}{N}) + C_0$$

(17)

The residual matrix is constructed, and the unknowns  $A_0, B_0, C_0$  are solved in Eq. (18).

Fig. 5 Flowchart of the parameter fitting algorithm

(14)

$$E = \sum_{n=1}^{N} [x(n) - x(n)]^{2}$$

$$= \sum_{n=1}^{N} [x(n) - A_{0} \cos(2\pi \hat{f} \frac{n}{N}) - B_{0} \sin(2\pi \hat{f} \frac{n}{N}) - C_{0}]^{2}$$

$$= (x - Mr)^{T} (x - Mr),$$

and

$$x = \begin{bmatrix} x(1) \ x(2) \ x(3) \end{bmatrix}^{T}, \quad r = \begin{bmatrix} A_{0} \ B_{0} \ C_{0} \end{bmatrix}^{T}, \quad (18)$$

ating of

$$x = \begin{bmatrix} \cos(2\pi \hat{f} \frac{n}{N}) & \sin(2\pi \hat{f} \frac{n}{N}) & 1 \\ \cos(2\pi \hat{f} \frac{1}{N}) & \sin(2\pi \hat{f} \frac{1}{N}) & 1 \\ \cos(2\pi \hat{f} \frac{(N-1)}{N}) & \sin(2\pi \hat{f} \frac{(N-1)}{N}) & 1 \end{bmatrix}$$

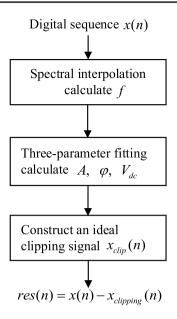

The ideal clipping sequence is constructed based on the desired parameters is show in Eq. (19).

$$x_{clipping}(n) = \begin{cases} \frac{1}{2}V_{fs}, x(\hat{n}) > \frac{1}{2}V_{fs} \\ x(\hat{n}), -\frac{1}{2}V_{fs} < x(\hat{n}) < \frac{1}{2}V_{fs} \\ -\frac{1}{2}V_{fs}, x(\hat{n}) < -\frac{1}{2}V_{fs} \end{cases},$$

$$x(\hat{n}) = \hat{A}\sin(2\pi\hat{f}\frac{n}{N} + \hat{\varphi}) + C_{0},$$

$$\hat{A} = \sqrt{A_{0}^{2} + B_{0}^{2}}, \quad \hat{\varphi} = \begin{cases} \arctan\frac{-B_{0}}{A_{0}}, \quad A_{0} \ge 0 \\ \arctan\frac{-B_{0}}{A_{0}} + \pi, \quad A_{0} \le 0 \end{cases},$$

$$[A_{0} B_{0} C_{0}]^{T} = (M^{T}M)^{-1}(M^{T}x),$$

$$(19)$$

The residuals of the ideal and actual clipping sequences are as follows, and the accuracy of the spurious component of the resulting ADC output sequence is affected by the parameter fitting error err(n):

$$res(n) = x_{in}(n) - x_{clipping}(n) = err(n) + hf + n_{all}.$$

(20)

The overall flow of the first part of the ADC dynamic testing algorithm is shown in Fig. 5. Compared with the traditional interpolation algorithms [16, 17], one can directly obtain the input signal parameters without calculating the higher-order inverse function. Compared with the sinusoidal four-parameter fitting method [18], it is unnecessary to consider the problem of iterative convergence. Compared with FIRE [19], the trigonometric method [20] not only reduces the leakage error but also reduces the error of the fenestration effect. Compared with the overfitting algorithm [13, 21, 22], there is no dependence on the selection of the set of over-zero points.

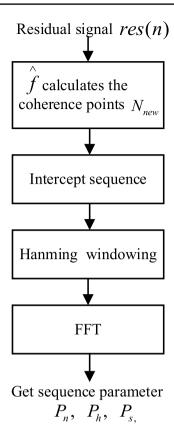

# 3.2 Data Preprocessing

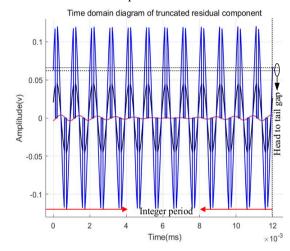

According to the sampling formula, the non-integer sampling period J is transformed into an integer sampling period  $J_{\text{int}}$ , and the corresponding number of sampling points  $N_{new}$  is obtained to intercept the signal, which can convert an incoherent sequence to a coherent sequence.

$$J_{\text{int}} = \text{int}(\frac{N}{Fs} \stackrel{\wedge}{f}), \ N_{new} = \frac{F_s}{\stackrel{\wedge}{f}} J_{\text{int}}, \ N_{\text{int}} = \text{int}(N_{new}).$$

(21)

In actual testing, problems such as aging equipment can result in the actual sampling frequency set not being an integer multiple of the signal frequency, so the truncated sequence is only an approximate correlation sequence, the significant spectrum leakage remains after the FFT  $\eta' \in (0,0.005)$ . The main flap convergence can be enhanced by the Hanning window to reduce the spectrum leakage:

$$x(n)' = x(n)w(n) = \frac{1}{2}x(n)(1 - \cos\frac{2\pi n}{N_{new}}), n = 1, 2...N_{new}.$$

(22)

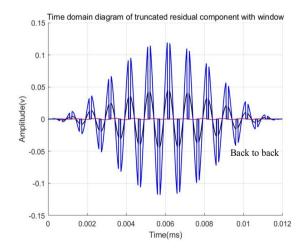

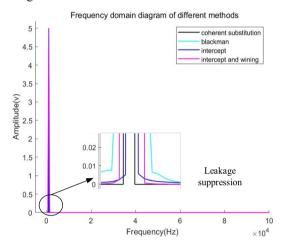

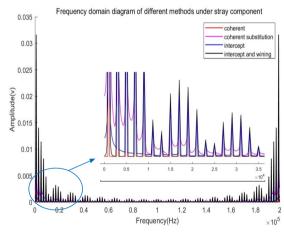

The time and frequency domain effects of data preprocessing on the residual signal obtained in the first part of the algorithm are shown in Figs. 6 and 7. The sequence after data preprocessing not only leaves an integer number of sampling periods but also has better continuity at the beginning and end of the sequence. For a single-frequency sine without extracting the fundamental, the suppression effect is better than that of the Blackman window with 58.1-dB side-flap attenuation, but the effect of the fundamental component is slightly worse than that of coherent replacement [9, 10]. However, when the object sequence becomes a residual containing periodic characteristics, the leakage suppression effect is much better than that of coherent substitution because it does not contain a large component of the fundamental wave, and coherent substitution does not change the residual frequency.

### (a) Noncoherent residual sequence time domain

# (b) Intercepted sequence time domain

(c) Preprocessing sequence time domain

Fig. 6 Time domain effect of algorithm

#### (a) Leakage of coherent and incoherent

#### (b) Leakage suppression effect original sequence

(c) Leakage suppression of preprocessing sequence

Fig. 7 Frequency domain effect of algorithm

When the effect of the algorithm's processing of the leakage is compared with the direct input of the coherent sequence, the resulting spectrum is not perfect. Therefore,

Fig. 8 Flowchart of data preprocessing algorithm

when calculating the spectral parameters, the fundamental harmonic amplitude is adjusted to improve the test accuracy.

Taking the power sum in the range of [-1, 1] around the even harmonics as the actual power value can reduce the effect of additional spuriousness caused by leakage and period residuals. Here, A is the estimated amplitude, and  $Y(k_p)$  is the residual value corresponding to the fundamental frequency in the residual sequence.

$$P_s = (\widehat{A} + |Y(k_p)|)^2,$$

$$P_h = 2\sum_{i=-1}^{1} Y(k_h + i), \quad h = 2, 4, 6...10.$$

(23)

The overall flow of the second part of the algorithm in ADC dynamic testing is shown in Fig. 8. Compared with the traditional algorithm, the energy convergence and side-valve attenuation functions of the complex window function can be realized with the most basic window function by transforming the residuals, and the periodic residual spectrum leakage can be suppressed.

#### 3.3 Restoring ADC Parameters

When the purity of the signal source does not meet the test conditions, the spurious component in the spectrum consists

of the ADC, the signal source, and the spurious component generated by the clock jitter.

$$SNR_{fs} = 10 \lg(\frac{P_s/k^2}{P_{an} + P_{sn}/k^2}),$$

$$THD_{fs} = 10 \lg(\frac{P_{ah} + P_{sh}/k^2}{P_s/k^2}),$$

$$10^{-SNR_{fs}/10} = k^2 10^{-SNR_{adc}/10} + 10^{-SNR_{src}/10},$$

$$10^{THD_{fs}/10} = k^2 10^{-THD_{adc}/10} + 10^{-THD_{src}/10}.$$

(24)

Here,  $P_{sn}$  and  $P_{sh}$  are the noise and harmonic power generated by the signal source as a function of the signal amplitude [2, 14].  $P_{an}$  and  $P_{ah}$  are the ADC noise and harmonics, which are independent of the signal amplitude.  $SNR_{adc}$  and  $THD_{adc}$  are the ADC's own parameters,  $SNR_{src}$  and  $SNR_{src}$  are the signal source parameters.

The THD derivation process is the same as SNR by canceling the signal source spurious power through the sequence.  $SNR_{fs}$  is the SNR obtained by direct calculation of the spectrum.

$$10^{-SNR_{fs1}/10} - 10^{-SNR_{fs2}/10}$$

$$= k_1^2 10^{-SNR_{adc1}/10} - k_2^2 10^{-SNR_{adc2}/10} + 10^{-SNR_{src1}/10} - 10^{-SNR_{src2}/10}$$

(25)

Spectral noise consists of intrinsic and random noise.  $P_{anr}$ ,  $P_{ani}$  are random noise power and intrinsic noise power of ADC.  $P_{snr}$ ,  $P_{sni}$  are random noise power, signal source and intrinsic noise power of signal source.

$$10^{-SNR_{fi1}/10} - 10^{-SNR_{fi2}/10} = k_1^2 \frac{P_{anr_1} + P_{ani}}{P_s} - k_2^2 \frac{P_{anr_2} + P_{ani}}{P_s} + \frac{P_{snr_1} + P_{sni}}{P_s} - \frac{P_{snr_2} + P_{sni}}{P_s}$$

(26)

Substituting the same amplitude sequence and ignoring the effect of amplitude jitter, then  $k_1 = k_2 = k = 1$ . Here  $P_n$  is the total spectral noise power and is the total harmonic power.

$$P_{\Delta n} = P_{n1} - P_{n2} = (P_{anr1} - P_{anr2}) + (P_{snr1} - P_{snr2})$$

$$P_{\Delta h} = P_{h1} - P_{h2} = (P_{ahr1} - P_{ahr2}) + (P_{shr1} - P_{shr2})$$

(27)

The ADC's own parameters can be estimated from the random power and the ADC's inherent quantization noise power.

$$\begin{split} SNR_{adc} &\approx 10 \lg(\frac{P_s}{P_{n1} - P_{n2} + P_q}), \\ THD_{adc} &\approx 10 \lg(\frac{P_s}{P_{h1} - P_{h2}}), \\ SINAD_{adc} &= 10 \lg(\frac{P_s}{P_{h1} - P_{h2} + P_{n1} - P_{n2} + P_q}) \\ ENOB_{adc} &= \frac{SINAD_{adc} - 1.76}{6.02}. \end{split} \tag{28}$$

In summary, the ADC parameter reduction algorithm flow is as follows: firstly, the random power is estimated by the noise power and harmonic power difference of each segmented sequence, and then the ADC power is calculated by adding the intrinsic power. In order to avoid the chance

### 4 Algorithm Simulation and Verification

In this section, the functionality and robustness of the proposed algorithm for dynamic parameter testing of ADCs under relaxed test conditions are verified through simulations, experiments and the test results are compared with conventional test results and datasheets.

#### 4.1 Simulation Results

MATLAB simulation results verify the effectiveness of this algorithm. The 16-bit ADC is modeled by MATLAB so that the sampling frequency is 200 kHz, the input sine wave frequency is 1 kHz, the number of samples is 16,200, the phase is 60°, and the signal source is 120 dB. The results of the traditional algorithm and the proposed algorithm for different amplitude sinusoidal waveforms are shown in Table 1.

From Table 1, it can be obtained that when the input amplitude slightly exceeds the full scale, there is a certain error in the input signal parameter fitting, which leads to the failure of the traditional algorithm, and therefore the input signal amplitude needs to be strictly controlled when measuring the ADC parameters by the traditional algorithm. However, for the proposed algorithm, the dynamic parameters can be accurately tested even if there is an error in the amplitude fitting. For example, when the input amplitude is 5.2 V, the errors of the measured SNR, SINAD, THD, and ENOB with respect to the reference values are 3.46 dB, 14.02 dB, 2.78 dB, and 0.46 bit, respectively, which can be eliminated by the third part of the proposed algorithm.

Moreover, from Table 2, the proposed algorithm also has superior results in suppressing spectral leakage when the number of sampling points is 16,384 points and the input signal is 5 V for non-coherent sampling. From Table 3, the proposed algorithm remains effective even when the input signal purity is 80 dB, and the test results are not affected by external input signal noise. When the input signal is 5.2 V, the test results of the proposed algorithm have an error of 1.06 dB, 1.9 dB, 0.74 dB, and 0.13bit for SNR, SINAD, THD, and ENOB, respectively, compared to the reference value, which is effectively improved by the third part compared to Table 1. Moreover, in the actual test species, this error can also be improved by increasing the test sample group.

**Table 1** Test performance of different ADC dynamic test algorithms under overrange

| Arithmetic         | Input amplitude (V) | Estimated amplitude (V) | SNR<br>(dB) | THD (dB) | SINAD (dB) | ENOB<br>(Bit) |

|--------------------|---------------------|-------------------------|-------------|----------|------------|---------------|

| Reference          | 5.00                | 5.00                    | 98.71       | 106.35   | 98.03      | 15.99         |

| Interpolation [10] | 5.00                | 5.00                    | 98.66       | -106.57  | 98.02      | 15.99         |

|                    | 5.05                | 5.04                    | 52.72       | -55.75   | 58.61      | 8.17          |

| Fitting [17]       | 5.00                | 5.00                    | 98.71       | -106.30  | 98.02      | 15.99         |

|                    | 5.05                | 5.04                    | 67.80       | -68.38   | 64.80      | 10.47         |

| Proposed           | 5.00                | 5.00                    | 98.46       | -108.32  | 98.43      | 16.05         |

|                    | 5.05                | 5.04                    | 98.37       | -114.78  | 98.32      | 16.03         |

|                    | 5.10                | 5.08                    | 96.81       | -116.71  | 96.70      | 15.8          |

|                    | 5.20                | 5.16                    | 95.25       | -120.37  | 95.23      | 15.53         |

|                    |                     |                         |             |          |            |               |

**Table 2** Test performance of different ADC dynamic test algorithms under incoherent sampling

| Arithmetic           |                    | Input<br>amplitude<br>(V) | SNR<br>(dB) | THD (dB) | SINAD (dB) | ENOB (bit) |

|----------------------|--------------------|---------------------------|-------------|----------|------------|------------|

| Direct FFT           |                    | 5.00                      | 31.43       | -51.40   | 31.41      | 4.93       |

| Blackman [8]         |                    | 5.00                      | 96.11       | -119.93  | 96.11      | 15.67      |

| Coherent Replacement | Interpolation [17] | 5.00                      | 97.90       | -109.63  | 97.88      | 15.97      |

|                      | Fitting [10]       | 5.00                      | 96.34       | -111.54  | 96.32      | 15.71      |

| Proposed             |                    | 5.00                      | 95.78       | -115.60  | 95.78      | 15.62      |

**Table 3** ADC dynamic parameter test results of the proposed algorithm at 80 dB signal source

| Input<br>amplitude<br>(V) | Estimated amplitude (V) | SNR<br>(dB) | THD (dB) | SINAD (dB) | ENOB (bit) |

|---------------------------|-------------------------|-------------|----------|------------|------------|

| 5.00                      | 5.00                    | 97.37       | -113.65  | 97.27      | 15.86      |

| 5.05                      | 5.045                   | 97.63       | -114.13  | 97.53      | 15.91      |

| 5.10                      | 5.08                    | 97.31       | -113.10  | 97.20      | 15.85      |

| 5.20                      | 5.16                    | 97.65       | -108.25  | 97.29      | 15.86      |

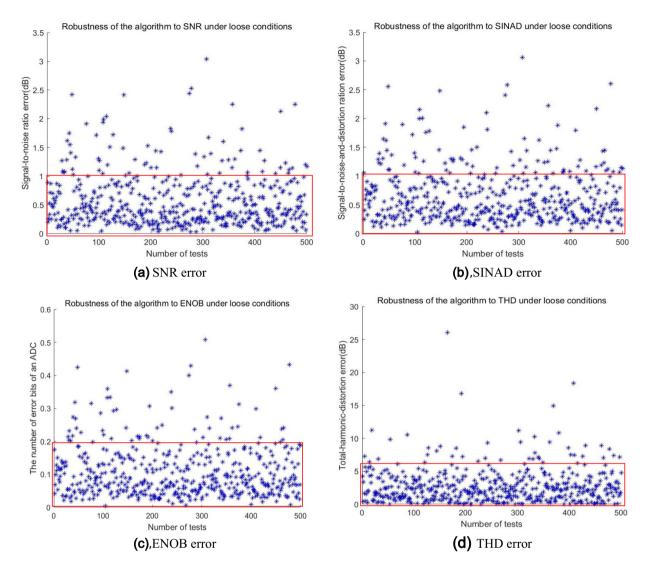

To verify the robustness of the algorithm for ADC performance testing under loose test conditions, 500 random parameter simulation experiments were conducted, in which the input signal purity, amplitude, and leakage size were randomly generated in the ranges of 75–95 dB, 5–5.2 V, and 0–0.5, respectively. The errors between the parameters SNR, SINAD, THD, and ENOB and the ideal parameters are shown in Fig. 9. The SNR and SINAD ratio errors are centrally distributed within 0–1 dB, the effective number of bit errors is centrally distributed within 0–0.2, and the THD error is centrally distributed within 0–5 dB.

In summary, the algorithm proposed in this paper can effectively relax the dependence of high-precision ADC test on high-precision signal source, reduce the test error caused by limiting, and reduce the test cost.

### 4.2 Experiment Results

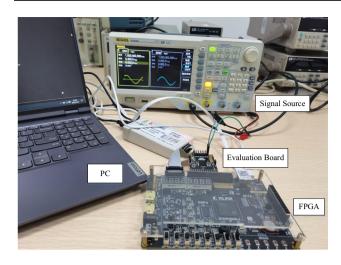

To verify the practicality of the proposed algorithm further, a test system using an ACX720 series field-programmable gate array (FPGA) equipped with an ADC was employed, and a dynamic performance test of the AD760 commercial high-precision ADC was conducted under loose conditions. The overall scheme of the ADC dynamic parameter test is shown in Fig. 10, and the test system was constructed as shown in Fig. 11. A high-speed and low-power Artix-7 series FPGA was used as the core processor, and the sampling clock and power supply of the ADC were generated by dividing the frequency of the FPGA crystal. The system was configured with the number of sampling points and sampling frequency through the Ethernet, and the FPGA drove the ADC to perform sampling after it received the data, and then stored the ADC output sequence captured by the serial port in a DDR3. After completing the sampling, the FPGA sent the data to a PC through the Ethernet for calculation.

The test results of the 16-bit ADC chip 7606 are shown in Table 4 when the sampling frequency is 200 kHz, the signal source frequency is 1 kHz, the signal source resolution is 14 bits, and the number of sampling points is 16,384 points. The measured SNR, SINAD, THD, and ENOB have errors of 0.39 dB, 0.23 dB, 7.24 dB, and 0.16 bits, respectively, compared to the typical values in the datasheet when amplitude is 5.2 V. Although the value of THD has a large error from the typical values, it is

Fig. 9 Robustness of the proposed algorithm

**Fig. 10** General scheme of ADC dynamic parameter testing

within the range of the minimum and typical values given in the manual. In addition, the test results of devices such as the 16-bit ADC ADS8361, ADS8689, the 14-bit ADC AD9248 etc. under this algorithm are shown in Table 5.

### 5 Conclusion

To address the limitation of high-precision ADC testing under severe testing conditions, an ADC dynamic

Fig. 11 ADC test system

parameter testing algorithm was developed for relaxing ADC testing that can measure the ADC dynamic parameters by over-ranging signals when coherence and purity do not satisfy the testing conditions. This enables the dynamic testing of ADCs to be separated from highprecision equipment, reducing test costs and improving test efficiency. The simulation and experimental results demonstrate the functionality and robustness of the algorithm under loose test conditions. The accuracy of the 16-bit ADC chip 7606 has an accuracy of 99.56%, 99.74%, 98.89%, and 93.23% for SNR, SINAD, ENOB, and THD, respectively, compared with the typical values of the handbook under the test conditions of an amplitude of 5.2 V, purity of 80 dB, and leakage of 0.3. Moreover, the harmonic distortion has an error of 7.24 dB compared with the typical values. The harmonic distortion is within the specified range of the manual, although it has an error of 7.24 dB from the typical value. The low dependence of the algorithm on the accuracy of external devices enables it not only to be used in ADC test prototyping projects but also to be ported to digital-analog hybrid automatic test equipment (ATE) testers to expand the scope of testing. In

**Table 5** Dynamic parameter test results of ADC devices under relaxed conditions

| chip    | Data<br>source | SNR (dB) | SINAD<br>(dB) | THD (dB) | ENOB (bit) |

|---------|----------------|----------|---------------|----------|------------|

| ADS8689 | Reference      | 91.53    | 91.53         | -112.73  | 14.91      |

|         | proposed       | 90.76    | 89.35         | -104.49  | 14.55      |

| ADS8361 | Reference      | 83.21    | 83.06         | -94.78   | 13.51      |

|         | proposed       | 81.98    | 81.56         | -88.94   | 13.25      |

| `       | Reference      | 73.48    | 73.00         | -88.21   | 11.83      |

|         | proposed       | 72.11    | 71.82         | -92.36   | 11.63      |

addition, the ability of the algorithm to test the dynamic parameters of overrange signals lays the foundation for sharing a common set of sampling data for static and dynamic parameter testing of ADCs, which can be used to improve the efficiency of ADC testing.

In addition, since the algorithm still has the ability to test dynamic parameters when the input signal amplitude exceeds the full scale of the ADC, the collected data can be used directly for dynamic parameter testing to avoid the repetition of the sampling process when the static parameter testing algorithm is performed using a signal slightly larger than the full scale. Moreover, when the algorithm carrier board is an FPGA, its parallelism can also be used to realize the simultaneous testing of static and dynamic parameters of the ADC.

Funding This work does not include any funding items.

**Data Availability** The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **Declarations**

**Conflict of Interest** The authors declare that they have no known conflict of interests that could have appeared to influence the work reported in this study.

**Table 4** AD7606 dynamic parameter test results under relaxed conditions

| Algorithm        | Amplitude (V) | SNR (dB) | SINAD (dB) | THD (dB) | ENOB (bit) |

|------------------|---------------|----------|------------|----------|------------|

| Reference        | 5.00          | 89.00    | 89.00      | -107.00  | 14.49      |

| Traditional [17] | 5.00          | 83.03    | 78.12      | -79.78   | 12.68      |

|                  | 5.05          | 61.69    | 60.72      | -67.70   | 9.70       |

|                  | 5.10          | 48.68    | 46.33      | -50.11   | 7.40       |

|                  | 5.20          | 42.33    | 38.33      | -40.53   | 6.07       |

| Proposed         | 5.00          | 88.89    | 88.38      | -109.81  | 14.46      |

|                  | 5.05          | 87.14    | 86.99      | -103.15  | 14.15      |

|                  | 5.10          | 89.57    | 89.30      | -101.66  | 14.54      |

|                  | 5.20          | 89.39    | 88.77      | -99.76   | 14.33      |

### References

- Luo HW, Liu JS, Yu YT et al (2021) Current status and Key Technologies of VLSI testing. Electron Prod Reliab Environ Test 39(S2):16–20

- Simoes JB, Loureiro CFM, Landeck J et al (1996) A new method for testing the effective number of bits of analog to digital converters. IEEE Nuclear Sci Symp Conf Rec 1:483–486. https://doi.org/ 10.1109/NSSMIC.1996.591036

- Song ZY (2016) MATLAB digital signal processing 85 practical cases: introduction to advanced. Beijing University of Aeronautics and Astronautics Press

- IEEE Std 1241TM-2010 (2011) IEEE standard for terminology and test methods for analog-to-digital converters. IEEE, New York, NY, USA, pp 1–139. https://doi.org/10.1109/IEEESTD. 2011.5692956

- IEEE Std 1658-2011 (2012) IEEE standard for terminology and test methods of digital-to-analog converter devices. IEEE, New York, NY, USA, pp 1–126. https://doi.org/10.1109/IEEESTD. 2012.6152113

- Agarwal P, Kumar S, Singh SP (2019) Closed form solutions of various window functions in fractional fourier transform domain. 2019 6th International Conference on Computing for Sustainable Global Development (INDIACom). IEEE, pp 64–68

- Belega D, Ciugudean M, Stoiciu D (2007) Choice of the cosineclass windows for ADC dynamic testing by spectral analysis. Measurement 40:361–371. https://doi.org/10.1016/j.measurement. 2006.06.016

- Sato K, Ishida T, Okamoto T et al (2021) Revisit to accurate ADC testing with incoherent sampling using proper sinusoidal signal and sampling frequencies. 2021 IEEE International Test Conference (ITC). IEEE, pp 284–288. https://doi.org/10.1109/ITC50571. 2021 00038

- Jiang J, Li J, Zhang D et al (2022) Research on analog-to-digital converter (ADC) dynamic parameter method based on the sinusoidal test signal. Electronics 11(14):2125. https://doi.org/10.3390/ electronics11142125

- Peng X, Li J, Zhang D et al (2022) High-precision ADC spectrum testing under non-coherent sampling conditions. Sensors 22(21):8170. https://doi.org/10.3390/s22218170

- Xu L, Sudani SK, Chen D (2013) Efficient spectral testing with clipped and noncoherently sampled data. IEEE Trans Instrum Meas 63(6):1451–1460. https://doi.org/10.1109/TIM.2013.22922 73

- Sudani S, Xu L, Chen D (2013) Accurate full spectrum test robust to simultaneous non-coherent sampling and amplitude clipping. 2013 IEEE International Test Conference (ITC). IEEE, pp 1–10. https://doi.org/10.1109/TEST.2013.6651920

- He Q, Huang P, Yu ZG et al (2014) The method for testing dynamic parameters of high-speed ADCs based on average spectrum. J Electron Meas Instrum 28(07):755–762. https://doi.org/ 10.13382/j.jemi.2014.07.011

- Simoes JB, Loureiro CFM, Landeck J et al (1998) Testing highresolution digitizers using conventional signal sources. Meas Sci Technol 9(1):6. https://doi.org/10.1088/0957-0233/9/1/002

- Jacobsen E, Kootsookos P (2007) Fast, accurate frequency estimators [DSP Tips & Tricks]. IEEE Signal Process Mag 24(3):123–125. https://doi.org/10.1109/MSP.2007.361611

- Lu M (2013) An enhanced procedure for calculating dynamic properties of high-performance DAC on ATE. 2013 IEEE

- International Test Conference (ITC). IEEE, pp 1–10. https://doi.org/10.1109/TEST.2013.6651877

- Yang Y (2022) A windowed interpolation algorithm for high-precision ADC spectrum testing. Advances in Natural Computation, Fuzzy Systems and Knowledge Discovery: Proceedings of the ICNC-FSKD 2021. Springer International Publishing, pp 69–78. https://doi.org/10.1007/978-3-030-89698-0\_8

- Pálfi V, Kollár I (2013) Acceleration of the ADC test with sinewave fit. IEEE Trans Instrum Meas 62(5):880–888. https://doi. org/10.1109/TIM.2013.2243500

- Sudani SK, Chen D (2013) FIRE: A fundamental identification and replacement method for accurate spectral test without requiring coherency. IEEE Trans Instrum Meas 62(11):3015–3025. https://doi.org/10.1109/TIM.2013.2267473

- Sudani S, Wu M, Chen D (2011) A novel robust and accurate spectral testing method for non-coherent sampling. 2011 IEEE International Test Conference. IEEE, pp 1–10. https://doi.org/10. 1109/TEST.2011.6139176

- Šaliga J, Kollár I, Michaeli L et al (2013) A comparison of least squares and maximum likelihood methods using sine fitting in ADC testing. Measurement 46(10):4362–4368. https://doi.org/10. 1016/j.measurement.2013.05.004

- Wu M, Chen D (2011) A faster method for accurate spectral testing without requiring coherent sampling. 2011 IEEE International Instrumentation and Measurement Technology Conference. IEEE, pp 1–6. https://doi.org/10.1109/IMTC.2011.5944273

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

Jun Yuan received B.E. and M.E. degrees in Electrical Engineering in 2006 and 2009 respectively, from Southwest Jiaotong University, China. And then in 2012 he received D.Eng. degree from Kochi University of Technology, Japan. Then he joined College of Optoelectronics Engineering, Chongqing University of Posts and Telecommunication, China. His areas of research interests are analog—digital mixed signal IC design, DFT research and noise processing IC design.

**Yuyang Zhang** is a postgraduate student in integrated circuit engineering at Chongqing University of Posts and Telecommunications, China. Her areas of research interest are digital signal processing and ADC testing.

**Liangrui Zhang** is a postgraduate student in integrated circuit engineering at Chongqing University of Posts and Telecommunications, China. His research directions are digital signal processing and ADC testing.

**Shuaiqi Hou** is an undergraduate in integrated circuit engineering at Chongqing University of Posts and Telecommunications, China.

**Yukun Han** is an undergraduate in integrated circuit engineering at Chongqing University of Posts and Telecommunications, China.