### Introduction to Digital and Analog IC Designs

#### **Topics**

- Introduction to Wireless Communications (1.5 classes)

- Basic Concepts for Integrated Circuits (3 classes)

- Analog IC Design Using Cadence Analog IC Design Tools (2.5 classes)

- Switching and Logic Circuits (1.5 classes)

- Bandgap Reference and Current Mirrors (2.5 classes)

- Exam I (1 class)

- Amplifiers (3 classes)

- Oscillators (2 classes)

- Digital IC Design Using Verilog HDL (3 classes)

- Digital Frequency Dividers (1 class)

- Digital Delta-sigma Modulators (2.5 classes)

- Exam II (1 class)

- Digital Phase Locked Loop (1 class)

- Conclusions and Final Reviews (1 class)

- Final Project Presentation (1 class)

- Final Project Report

## **Chapter 3**

### **Cadence® Analog Design Environment**

- Getting started with Cadence Tool

- Schematic Editor

- Project

Cadence tool information @

http://www.cadence.com/datasheets/

It supports RF/Analog and mixed-signal simulation

# **Required Software**

• Xming: is a free software port of the X Window Server to Microsoft Windows. Window Server to Microsoft Windows. Xming-fonts is required to display fonts correctly.

X Xming-6-9-0-31-setup.exe 2,154 KB X Xming-fonts-7-5-0-47-setup.exe 31,589 KB

- Secure CRT6.75:

- <u>http://www.eng.auburn.edu/ens/helpdesk/o</u> <u>ff-campus/downloads.html</u>

# **Access Workstations**

- SecureCRT 6.75 and Xming

- First, double click Xming to start the window interface for the workstation we will use.

Then, double click SecureCRT 6.75 and you will see a log-on window as shown in next slide.

# **Setup for SecureCRT**

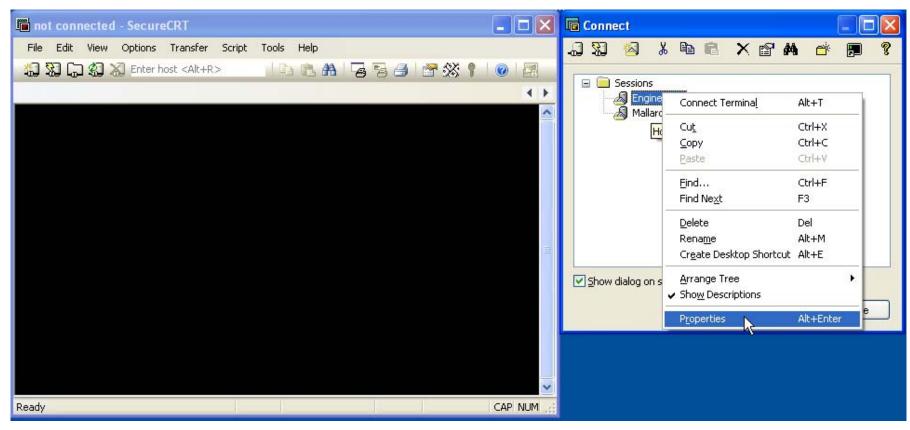

## Right click "Engineering" and click Properties

# **SecureCRT**

When you open secureCRT, go to "Session Options", select "Remote/X11" and check "Forward X11 packets". Then click OK

## How to login to a workstation

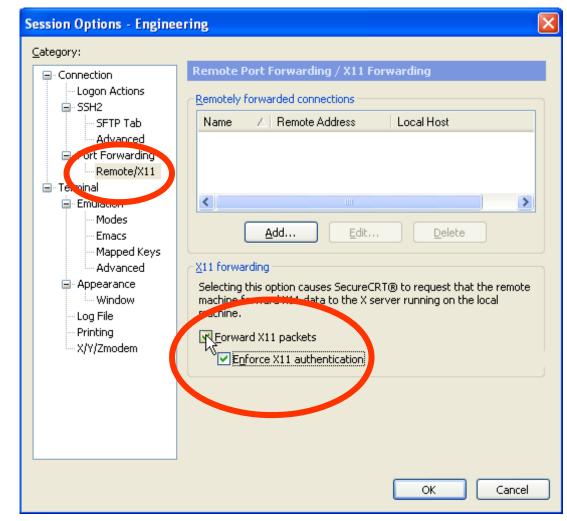

• Click connect and then type in your username and password

# **SecureCRT Interface**

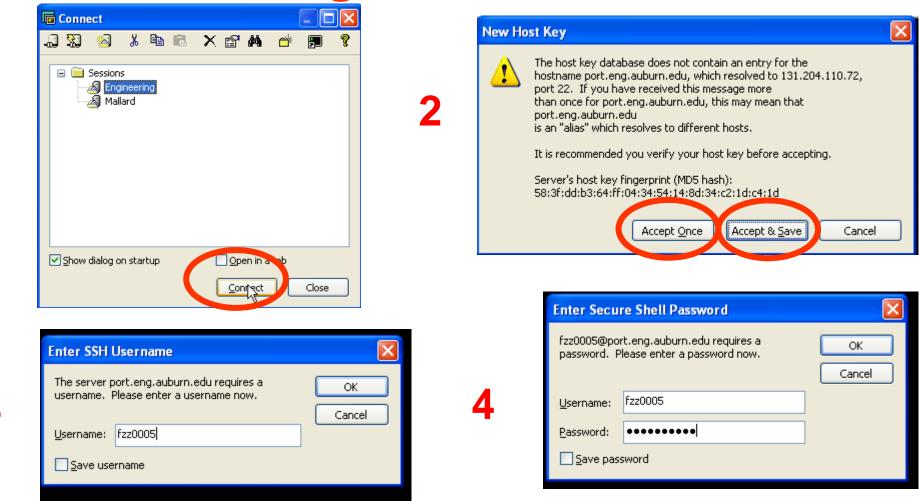

- Press "Enter"

- Then type "yes" and press "enter"

- Type your password and "enter"

| 👼 Er                                                                                                                                                                                                                                                                                                                                                                                                                                               | nginee          | ring - | SecureC                                | RT                                                                                                                                                             |         |          |              |         |       |     |    |              |        | K |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|--------------|---------|-------|-----|----|--------------|--------|---|

| File                                                                                                                                                                                                                                                                                                                                                                                                                                               | Edit            | View   | Options                                | Transfer                                                                                                                                                       | Script  | Tools    | Help         |         |       |     |    |              |        |   |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30 G            | 1 🕄 🕻  | 🐔 Enter l                              | nost <alt+r< th=""><td>&gt;</td><td></td><th>12. <b>A</b></th><th>1 😼</th><th>58 🗄</th><th>) 🖻</th><td>28</td><td><b>°</b>. (</td><th>0</th><td></td></alt+r<> | >       |          | 12. <b>A</b> | 1 😼     | 58 🗄  | ) 🖻 | 28 | <b>°</b> . ( | 0      |   |

| 💜 Er                                                                                                                                                                                                                                                                                                                                                                                                                                               | ngineer         | ing    |                                        |                                                                                                                                                                |         |          |              |         |       |     |    |              | 4      | Þ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |        |                                        | s, or ge<br>.auburn.                                                                                                                                           |         | contac   | t,           |         |       |     |    |              |        | ^ |

| ====                                                                                                                                                                                                                                                                                                                                                                                                                                               | SE EM8<br>===== | arr ac | ====================================== | -auburn.                                                                                                                                                       | ======= |          |              |         |       |     |    |              |        |   |

| NO                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TE:             |        |                                        |                                                                                                                                                                |         |          |              |         |       |     |    |              |        |   |

| The ssh protocol is used to login to unix/linux machines. You<br>will be prompted to accept a machine key the first time you login<br>to an individual machine. You will also be prompted for a password a<br>second time each time you login.                                                                                                                                                                                                     |                 |        |                                        |                                                                                                                                                                |         |          |              |         |       |     |    |              |        |   |

| If you choose the default login location you will be connecting<br>to a linux machine, not a Sun machine. If you have particular Sun<br>you wish to log into, manually type the hostname below.                                                                                                                                                                                                                                                    |                 |        |                                        |                                                                                                                                                                |         |          |              |         |       |     |    |              |        |   |

| ****                                                                                                                                                                                                                                                                                                                                                                                                                                               | *****           | *****  | ******                                 | ******                                                                                                                                                         | ******  | *****    | *****        | *****   | ***** | *** |    |              |        |   |

| Please enter the name of an Engineering host <anywhere>:<br/>The authenticity of host '131.204.14.185 (131.204.14.185)' can't be established.<br/>RSA key fingerprint is 43:62:ce:77:15:11:88:fd:f0:57:20:86:c4:f2:6c:4b.<br/>Are you sure you want to continue connecting (yes/no)? yes<br/>Warning: Permanently added '131.204.14.185' (RSA) to the list of known hosts.<br/>fzz0005@131.204.14.185's password:<br/>fzz0005@tux185:**</anywhere> |                 |        |                                        |                                                                                                                                                                |         |          |              |         |       |     |    |              |        |   |

| Ready                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,               |        | ssh2: /                                | AES-128                                                                                                                                                        | 24,     | , 19   2 | 4 Rows,      | 80 Cols | VT220 | )   |    | 0            | AP NUM | Í |

## How to login to a workstation

- When the system prompts "Please enter the name of an Engineering host <anywhere>:", just enter and input password. It will randomly select a workstation for you to use. The workstation name should starting with "tux" and ending with a number.

- Type "xterm" then you will see a pop-up window.

- Copy the class-provided .bashrc file to your home directory ("~" is your home directory).

- Type "source .bashrc" when you are under home directory.

# **Setup Cadence Tool**

- Creat your own starting directory for your cadence by using command "mkdir class"

- Copy the cadence configuration files to this newly created directory. Those files include .cdsenv .cdsinit display.drf cds.lib.

- From your "class" directory, type "icfb&" to start cadence.

### **Design System Initialization Files**

- .bashrc or .cshrc and .login → configure the operating system environment and the UNIX environment when you login and start a UNIX application. (Linux environment is preferred)

- .cdsinit  $\rightarrow$  customizes the Affirma Analog Circuit Design Environment.

- .cdsenv  $\rightarrow$  configure Cadence Analog Artist tool environment.

- cds.lib → set paths to the libraries used by the Analog Artist software.

Cadence default lib:

INCLUDE /linux\_apps/cadence/IC/share/cdssetup/cds.lib

User defined lib:

DEFINE sige5am /class/ibm\_lib/5am/IBM\_CDS/sige5am/relAM/sige5am DEFINE Dai6970 ~/elec6190/Dai6970

Cadence process design kit (PDK) can be downloaded www.cadencePDK.com

## **Start Cadence Tool**

- icfb& → front to back design, default CDS\_Netlisting\_Mode "Digital"

- icms& → mixed signal design, default CDS\_Netlisting\_Mode "Digital"

- msfb& → mixed signal front to back design, default CDS\_Netlisting\_Mode "Analog", don't need to add setenv CDS\_Netlisting\_Mode "Analog " in .bashrc or .cshrc.

- Schematic cellview to cellview defaults for creating a symbol with Artist. The default is to not create an Artist symbol. The following has been added in .cdsinit: schSetEnv( "tsgTemplateType" "artist" )

### **Initializing Design Framework II Environment**

The Design Framework II software reads your *.cdsinit* file at startup to set up your environment.

#### .cdsinit.

Sets user-defined bindkeys. Redefines system-wide defaults. Contains SKILL commands.

The search order for the .cdsinit file is: <Filename><install\_dir>/tools/dfll/local the current directory [Name6970] ← put .cdsenv, .cdsinit, cds.lib here the home directory

When a .cdsinit file is found, the search stops unless a command in *.cdsinit* reads other files.

Path to a sample .cdsinit file:

<*Filename*><*install\_dir*>/*tools*/dfll/samples/artist/cdsinit<*install\_dir*>=/opt/cadence/ic5.033

## **Summary of Cadence Tool Setup**

#### 1) Sign Non-Disclosure Agreement.

During the course, students ("Receiving Party") may receive or use information regarding analog and digital IC design tools and processing technology libraries. The receiving party agrees to keep any information received during the course strictly confidential and NOT to disclose any information regarding the class notes, EDA tools and technology libraries to any party outside of the class. Upon the completion of the class, the access to the technology files should be removed and the manuals and any other information related to the technology files should be destroyed.

2) Copy .bashrc to your home directory

3) Place .cdsenv and .cdsinit files at your launch directory.

4) Place or update cds.lib file at your launch directory. Make sure to include: INCLUDE /linux\_apps/cadence/IC/share/cdssetup/cds.lib

DEFINE sige5am /class/ibm\_lib/5am/IBM\_CDS/sige5am/relAM/sige5am

5) Type "icfb&" to launch the tool.

6) Go though Cadence "Virtuoso® Schematic Composer Tutorial"

- 7) Further reading on simulation: "Affirma Spectre Circuit Simulation User Guide" and "Affirma RF Simulator User Guide "

- 8) Further reading on layout: "Cell Design Tutorial" and "Virtuoso Layout Editor User Guide"

## **Analog Circuit Simulator Setup**

- Select Tools>Analog Environment to see the simulator.

- Setup --> Model Library: /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre/design.scs /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre/process.scs

- Make sure design.scs is above process.scs

- Setup --> Simulation Files:

Include Path: /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre

**Definition Files:** definitions.scs

The above steps were saved in a state file. In class directory, under Cadence, copy the "state\_template" directory to your unix directory: ~/.artist\_states/your\_lib/your\_design/spectre/. Then, load this state in Cadence "Analog Environment under tools".

IBM manuals located at: /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/doc

## **Summary of Cadence Setup Procedure**

- (1). Change IC tools version to 5.141. It can be done with the user setup interface or manually.

- (2). Add sige5am library. Choose /class/ibm\_lib/5am/IBM\_CDS/sige5am/relAM/sige5am using library path editor, save it. The relAM is a symbol link to V2.3.0.5AM, you can use V2.3.0.5AM as well.

- (3). Copy .cdsinit and .cdsenv from //class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/examples/ to your working directory. You may want to use Cadence binding key instead of that from IBM, just comment out or delete the line contains Key binding in the file .cdsinit (add the write permission: chmod +w .cdsinit).

- (4). Setup CDS\_Netlisting\_Mode variable.

- If you use CSH, add this to the ~/.cshrc: setenv CDS\_Netlisting\_Mode Analog

- If you use BASH, add this to the ~/.bashrc: export CDS\_Netlisting\_Mode Analog

- (5). Add AMS property to your design library: select from the CIW menu, IBM\_PDK ->library->Add A&MS properties. A dialog will pop up, then choose the library name as your design library name and the technology such as sige5am. The other two options are number of the metal layers and type of the capacitor, you can leave it as default.

- (6). During the simulation, add model and definition files.

- Setup --> Model Library: /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre/design.scs /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre/process.scs

- Setup --> Simulation Files: include path: /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre definition files: /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre/definitions.scs

- (7). To print the schematic and the waveform to postscript file (.ps).

- copy .cdsplotinit to work directory: cp /linux\_apps/cadence/IC/tools/plot/etc/cdsplotinit .cdsplotinit

- When plot in schematic window or hardcopy in waveform window, choose postscript output.

## **Start Cadence Tool**

#### **Command Interpreter Window (CIW)**

| 🎽 icfb - Log: /home/dai/yaoyuan/                                                                                                                                                                                                                                                                                                                         | <u>- </u> _                    |        |      |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------|------|--|

| File Tools Options IBM_PDK                                                                                                                                                                                                                                                                                                                               |                                | Help   | 1    |  |

| Licensed Materials - Propert<br>Copyright: International Bus<br>This Material may not be cop<br>Semiconductor Research and D<br>"AIX"<br>System hardware set for IBM<br>"IBM_PDK Menu added"<br>registering "Schematics" wit<br>registering "Symbol" with sc<br>registering "Layout" with le<br>"<br>"IBM_PDK Menu added"<br>Xlib: extension "Generic Ev | h schAMSTrigger<br>hAMSTrigger | 11.0". | AL D |  |

| mouse L:                                                                                                                                                                                                                                                                                                                                                 | И:                             | R:     | _    |  |

| >                                                                                                                                                                                                                                                                                                                                                        |                                |        |      |  |

### **Library Manager**

CIW: Tools -> Library Manager.

| Show Categories                                                                                                         | Show Files                                                                                                                                                               |                                                                          |  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

| - Library                                                                                                               | Cell                                                                                                                                                                     | View                                                                     |  |

| <u>]</u> analogLib                                                                                                      | žanos4                                                                                                                                                                   | Isymbol                                                                  |  |

| US_8ths<br>ahdlLib<br>basic<br>cdsDefTechLib<br>ee425<br>functional<br>mosis<br>refLib<br>rfExamples<br>rfLib<br>ripper | nbsim4<br>njfet<br>nmes<br>nmes4<br>nmos<br>nmos4<br>nodeQuantity<br>noise<br>npn<br>nsoi<br>oscport<br>pbsim<br>pbsim4<br>pcapacitor<br>pcccs<br>pccvs<br>pdc<br>pdiode | A auCdl<br>auLvs<br>cdsSpice<br>hspiceS<br>spectre<br>spectreS<br>symbol |  |

|                                                                                                                         |                                                                                                                                                                          |                                                                          |  |

| - Messages                                                                                                              |                                                                                                                                                                          |                                                                          |  |

### Library Manager -- View

- schematic contains the logical design of the device.

- **symbol** contains the symbol representation of the schematic.

- *layout* contains the silicon -level representations of the transistors and wiring.

- **CdsSpice**, **HspiceS**, **Spectre**, **spectreS** –contain spice information for the element.

- **abstract** contains an abstract representation of the layout for use by Cadence place and route software.

- extracted contains layout connectivity for use by verification programs.

- **behavioral** contains the VHDL description of the cell

### **Creating a New Cellview**

In the CIW or library manager, select FILE – New – Cellview.

Create a new cellview from the Library Manager or CIW.

- Specify the library Name, Cell Name, View Name, and Tool to use. The path to the *cds.lib* file will appear in the form and is not editable.

- Modify the Tool field to create a layout, verilog, symbol, schematic, vhdl, or ahdl view.

# **Creat your own Library**

• Select Tools>Library Manager.

|                                                                                                | e_start_tutorial                 |      |              |

|------------------------------------------------------------------------------------------------|----------------------------------|------|--------------|

| ile <u>E</u> dit <u>View</u> <u>D</u> esign Manager                                            |                                  |      | <u>H</u> elp |

| Show Categories 📃 Show Files                                                                   |                                  |      |              |

| Library                                                                                        | Cell                             | View |              |

|                                                                                                | a second                         | Ĭ.   |              |

| 5_8the<br>hdLib<br>haloglib<br>asic<br>dsDefTeckLib<br>motional<br>EExamples<br>ELib<br>igeSam |                                  |      |              |

| Messages                                                                                       |                                  |      |              |

| og file is "/home/dai/yaoyuan/Cadence                                                          | _start_tutorial/libManager.log". |      |              |

# **Creat your own Library**

- From Lib manager menu, select File>New>Library.

- Type library name, e.g. my\_test. Then click Next to see "Technology file for new library" window, select "Attach to an existing techfile", click OK. Then select "Sige5am".

- Click my\_test lib and select File>New>cell view. Name your own cell and make sure view name is "schematic" and tool is "Composer-schematic". Then click OK, you will see schematic interface.

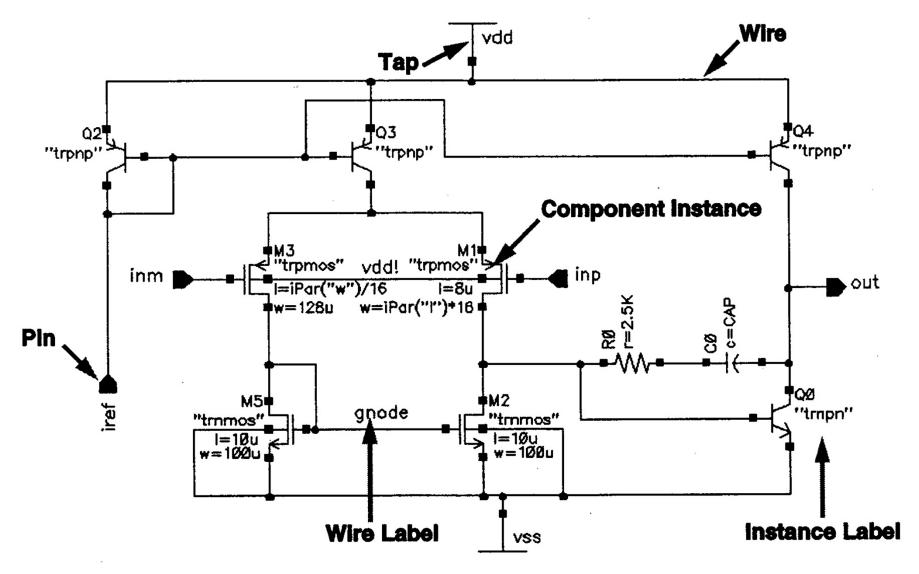

### **Contents of Schematic**

Chap 3, Cadence, 5190/6190, Foster Dai, 2013

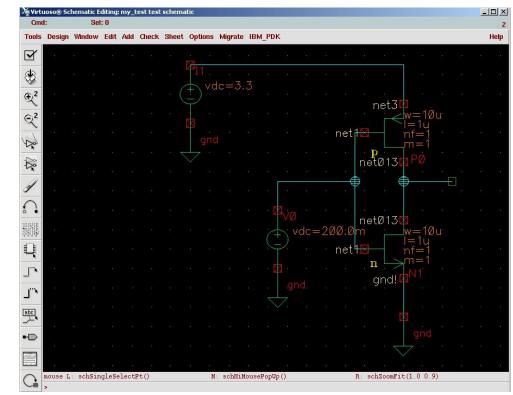

# Add instance to your schematic

- Select Add Instance or the bindkey "I" to display the ADD Instance form.

- Parameter units, such as ohms are implicit.

- Select "pfet" "nfet" from sige5am lib. Select "vdc" "gnd" from "analogLib".

- Use "w" to add a wire.

- Use hotkey "Q" to change the instance property. Set your Vdd DC voltage as 3.3V, your input DC voltage Vin as 0.2V.

### **Adding Component Instances**

• Design components are generally instances of a symbol cellview and might be design primitives. Here are some properties associated with design component instances:

| Parameter     | Example Value |

|---------------|---------------|

| Library Name  | analogLib     |

| Cell Name     | res           |

| View Name     | symbol        |

| Instance Name | R2            |

The Instance Name is assigned automatically, unless explicitly specified.

Find analog design primitives in the analogLib library. This library is included wherever the Analog Artist software is installed in the path *../tools/dfll/etc/cdslib/artist*. Include this path in your library search path to use analogLib components.

The system prompts for component parameters when instantiating the components. Attach multiplier suffixes, such as k for 1000, to numerical quantities.

Use the rotate, upsidedown, and sideways buttons to change the orientation of your components as they are placed in the schematic.

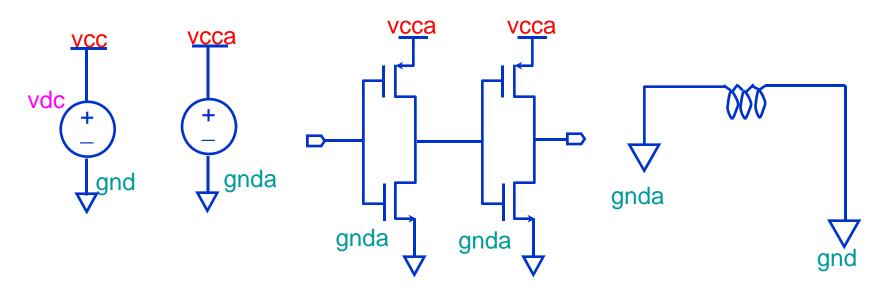

### **Adding Source and Ground**

Sources, taps, and grounds are instance of cells. Sample source cells are in the *analog library*.

- Choose from independent, dependent, and place-wise linear (PWL) sources.

- Choose tap and ground cells, which use to establish global nets.

- An instance of the cell gnd is required in the design for DC convergence.

### **Adding Source and Ground**

#### **Adding Sources and Ground**

Ground

Always include the symbol gnd found in the analogLib library, Analog simulators require that all nodes in the circuit must have a DC path ground. This would be represented as node 0 in the Cadence SPICE circuit simulator, for example. Use other ground symbols, such as gnda, for a ground that is connected to the reference ground through an analog circuit.

• Voltage sources

Include all of your DC and transient voltage and current sources in the schematic, There are many types of voltage sources in analogLib. For example, some of the independent voltage sources are *vdc*, *vsin*, *vpulse*, *vexp*, *vpwl* and *vpwlf*. Each source has a current equivalent that begins with the letter i. There are also equivalent dependent sources.

All sources generate input waveforms except for pwlf sources, which simulate a circuit using a text file of data tables. It is not necessary to include sources in the schematic, although this is often convenient. Attaching a stimulus file to the final netlist is discussed in the analog simulation section of this course.

• Voltage taps

Use taps symbol to transfer voltages and currents throughout the design without using wires. Voltage tap symbols, such as *vcc,vdd,vcca*, and *vccd* are in the analogLib library.

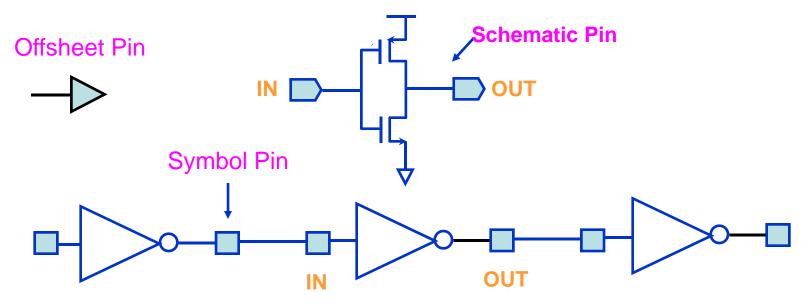

### **Adding Pins**

Pins have a user-defined Name and a Direction (input, output or input/output). Pins are of three types:

- Schematic pins provide ports to a schematic.

- Symbol pins provide ports to a symbol representing a schematic, and are connection points to the symbol in a hierarchal design.

- Offsheet pins are used in large designs without hierarchy.

Pin names and directions must match in all cellviews of a cell.

### Pins

For analog designers, pins have two primary functions:

- Pins represent connection points between different cellviews such as schematic, symbol, and layout representation. Using named pins identifies eqivalent inputs, outputs, and I/O ports throughout the design environment.

- Pins provide connection points for objects which are hierarchically instantiated.

**Pin Properties**

Pins have a pin name, pin type, and pin direction. These should be consistent throughout your design.

Multiple Sheet Design with Offset Pins

The composer: Design Entry Help manual includes a section on multiple sheet design methodology and information on the offsheet pin type.

Pins (*ipin, opin, iopin, sympin*) now come from "basic" library.

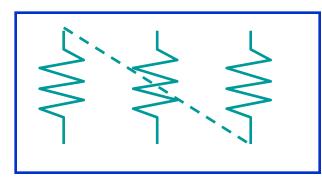

### Adding Wires and Wire Labels

Automatic routing is the default mode.

**Route Entered**

The System Routes

When not labeling a wire, the system names the net formed by the wires.

If the router cannot find a path between two points,

- Adotted "fight linw" is placed to establish connectivity only.

- •Click on intermediate points to guide the router to yield a solid line of connectivity.

- •Use the Cmd Options icon or F3 key to modify the wiring options.

#### Wires

Draw wires between the instance pins and schematic pins to connect them. Use wide wires to indicate multiple signals on a wire, the system does not force or check this. Draw wires at any angle, but most designers frequently restrain wires to orthogonal lines

• Using Route Methodology

The route draw mode chooses two points in your design and then it automatically routes a wire around components. If a routed net remains dotted, it is because there are no clear routing channel. This can happen if the instances sre too close or overlap the selection boxes. To solve this, move the components further apart to give a routing channel. Routing method options exits to wire together two points immediately (the default) or indicate many points to route together later in a single

step. More information on route methods in included in the design entry reference documentation.

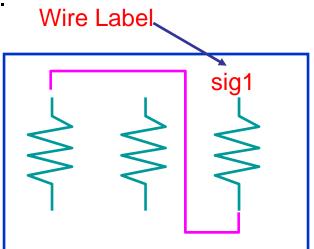

• Wire Labels

Labeling wires gives the corresponding net a meaningful name in the simulation results data. Otherwise nets are system named. There is some control over the automatically generated names, but these may not be meaningful as custom names

Click the Cmd Options icon in the schematic window or press the F3 key to change the default wiring setup.

Schematic Pins and glabal symbol pins name wires by adoption.

Note: Inherited connections, not shown, will be discussed in the Inherited Connection chapter

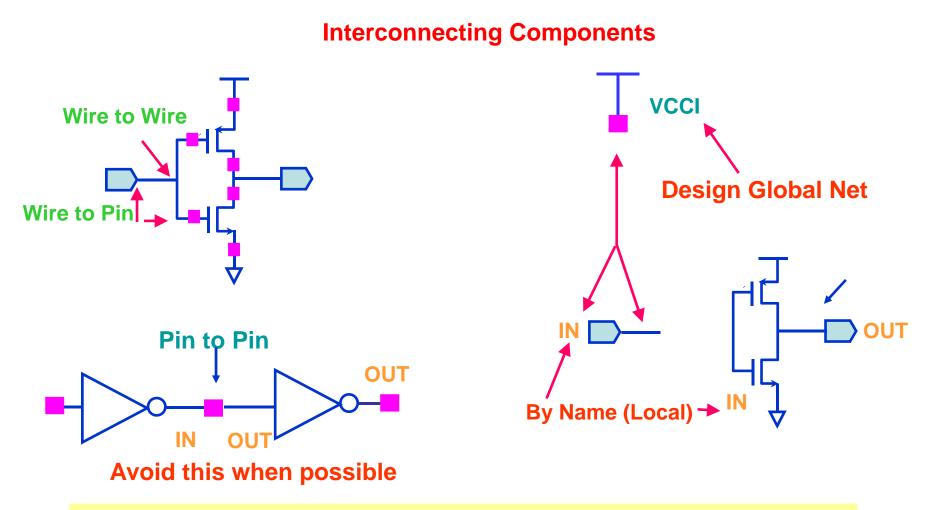

#### Interconnecting Components

- Physical Connectivity All physical connections are made by wire to pin, wire to wire, or pin to pin connections.

- Connectivity by Name

If two wires have been labeled with the same name, they become part of the same net when connectivity is established.

• System Assigned Names

If a net is unnamed, the system generates a name such as net100 or net7. optionally change the base name from net to something else. If a wire is connected to a schematic pin, then the pin is used to name the net by adoption when connectivity is established,

Global Nets

Any net or pin name that ends in an exclamation point will be part of a global net when connectivity is established. Global nets are automatically connected through the hierarchy without the use of wires. For example, voltage taps have symbol pin names that end in an exclamation point. If a wire is connected to a pin that has global name, the pin name is used to name the net by adoption. This is how voltage and ground signals are propagated throughout a design.

#### Schematic Checking

During schematic checking, all of the following are performed by default:

- Update Connectivity

This process associates wires and pins with logical connections called nets.

- Schematic Rules Check

- Logical checks

- Physical checks

- Name checks

- Cross View Checker

This option checks for pin name and direction consistency between cellviews.

Select **check** – **Rules setup** from a schematic window to edit the rules. Disable any or all of these schematic checking features, if not needed.

#### **Schematic Checking**

Schematic checking is a critical step in the design process.

Either check a single cellview or descend through the hierarchy to check all cellviews in your design.

Checking a schematic accomplishes the following:

- Update Connectivity When connectivity is established, wires and pins in the design entry window become associated with logical connections called nets. It is necessary to correct connectivity problems prior to going on to the next design phase.

- Schematic Rules Check This process checks the schematic with a set of rules. Access them with the Check – Rules Setup command from the schematic window.

The checks include:

- -- Logical checks, such as Floating Input Pins and Shorted Output Pins.

- -- Physical checks, such as Unconnected Wires and Overlapping Instances.

- -- Name checks, such as Instances Name Syntax.

- Cross-View Checker This option checks the pin consistency between different views of the cell. Pin name directions must match between cellviews.

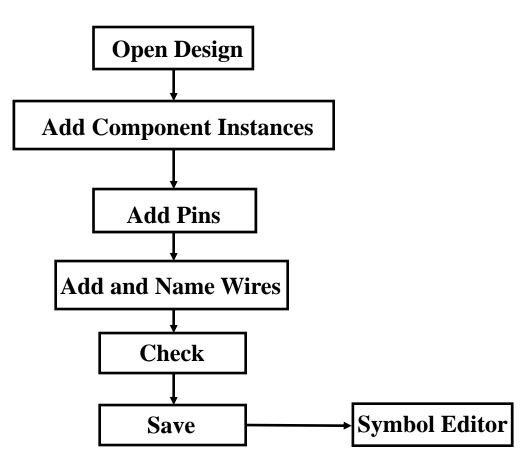

### **Schematic Entry Flow**

Chap 3, Cadence, 5190/6190, Foster Dai, 2013

## **Simulator Setup**

| 🗙 Virtuoso?Analog Design Environment (1)          |                                            |                | T=27 C Simulator: spectre                                                                                                | 2       |

|---------------------------------------------------|--------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------|---------|

| Status: Ready                                     | T=27 C Simulator: spectre                  | 3              | otions Migrate                                                                                                           | Help    |

| Session Setup Analyses Variables Outputs          | Simulation Results Tools                   | Help           |                                                                                                                          |         |

| Design                                            | Analyses                                   | ٠Ę             | N                                                                                                                        |         |

| Simulator/Directory/Host                          |                                            | ्रि            | X spectre0: Model Library Setup                                                                                          |         |

| Library D                                         | Arguments Enable                           | ⊐ AC<br>⊏ TRAN | OK Cancel Defaults Apply                                                                                                 | Help    |

|                                                   | 0 1u mode yes                              | ⊐ DC           |                                                                                                                          |         |

| View ≋ Stimuli                                    |                                            |                | #Disable Model Library File Section                                                                                      | Biable  |

| Simulation Files                                  |                                            | XYZ            | /IBM_CDS/sige5am/V2.3.0.5AM/models/spectre/definitions.scs                                                               |         |

| Des Mattab/Similaik                               | Outputs                                    | <b>I</b> ∎″    | b/Sam/IBM_CDS/sige5am/V2.3.0.5AM/models/spectre/design.scs<br>/Sam/IBM_CDS/sige5am/V2.3.0.5AM/models/spectre/process.scs | Disable |

| # Name Environment ignal/                         | /Expr Value Plot Save March                | 14             | ·····),                                                                                                                  | Up      |

|                                                   |                                            | - Jal          |                                                                                                                          |         |

|                                                   |                                            | 8              |                                                                                                                          | Down    |

|                                                   |                                            |                | Model Library File Section (op                                                                                           | i.)     |

|                                                   |                                            | 8              | Į.                                                                                                                       |         |

| > Results in /scratch/fzz0005/simulation/tb_inv/s | Plotting mode: Replace = spectre/schematic | $\sim$         | Adit Delete Change Edit File                                                                                             | Browse  |

#### • Add the following files with correct order.

- /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre/definitions.scs

- /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre/design.scs

- /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre/process.scs

## **Simulator Setup**

| 🔀 Virtuoso® Analog Design E | nvironment (1)                                                   |                        |

|-----------------------------|------------------------------------------------------------------|------------------------|

| Status: Ready               | T=27 C Simulator: spectre 3                                      | Down                   |

| Session Setup Analyses      | Variables Outputs Simulation Results Tools Help ction (opt.)     |                        |

| Design                      | Analyses - 곳 -                                                   |                        |

| Library my_test             | # Type Arguments Enable                                          | Browse                 |

| Cell test                   | 1 dc t yes dc                                                    |                        |

| <b>View</b> schematic       | T T T T T T T T T T T T T T T T T T T                            |                        |

| Design Variables            | Outputs E                                                        |                        |

| # Name Value                | # Name (Signal / Room Walve Blat Save March                      | ×                      |

|                             | OK Cancel Defaults Apply Browse                                  | Help                   |

|                             | Include Path                                                     |                        |

|                             | Definition Files [bm_lib/Sam/IBM_CDS/sigeSam/V2.3.0.5AM/models/s | pectre/definitions.scs |

| >                           | Stimulus File                                                    |                        |

- Another place for definition file

- /class/ibm\_lib/5am/IBM\_CDS/sige5am/reIAM/models/spectre/definitions.scs

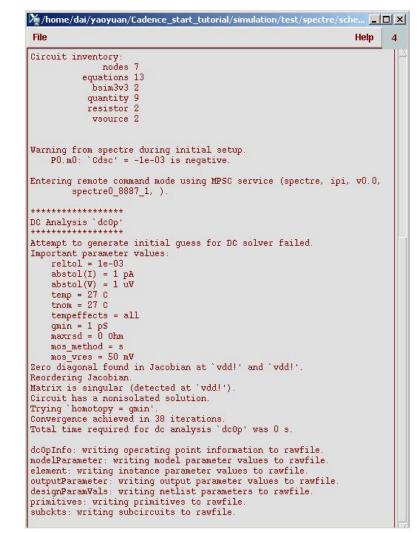

# Simulate the circuit

- Select Analyses>Choose>DC

- Enable the DC analysis and save DC operating point

- Select Simulation>Netlist and Run. Then you will see a window pop-up and shows the simulation process.

# **Viewing simulation results**

- Choose "Session"-> AWD for waveform viewer.

- From simulator, select Results>Annotate>DC node voltages and DC operating points. Then you will see the DC simulation results have been labeled in your schematic.

- You can select other analysis like "tran" and "ac" to verify your circuit's functionality and performance.

- Usually Results>Direct Plot>Main form command can give you a lot of simulation information you want.

**Other Tools in Cadence Design Environment**

Virtuoso Composer for schematic capture,

Analog Environment for simulation,

Virtuoso Layout for layout,

Diva for DRC (design rule checking),

Diva for extraction,

Diva for LVS (layout vs. schematic),

Analog Environment for postlayout simulation

## **DIVA Verification Tools**

- Diva Design Rule Checker (DRC)

- Diva Layout vs. Schematic (LVS) Verifier (includes electrical rule checks (ERC) and extraction of device layout parameters)

- **Diva Parasitic Extractor (RCX)**

- Diva Physical Verification Suite (consists of Diva DRC and Diva LVS)

- Diva Physical Verification and Extractor Suite (consists of Diva DRC, Diva LVS, and Diva RCX)

### **General Bindkey Chart**

| Z<br>^v<br>↓<br>↓<br>↑   | Previous View<br>Go To CIW<br>Pan Down<br>Pan Left<br>Pan Right<br>Pan Up | VERILOG HDL or<br>Check and<br>^ s Save As<br>Search<br>Open<br>Print |

|--------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------|

| F3<br>F4                 | Toggle Options Form<br>Toggle Partial Selection                           | ^ e Return<br>Return To<br>Close Win                                  |

| r<br>R<br>^ r            | Rotate (EF)<br>Sideways (EF)<br>Upside Down (EF)                          |                                                                       |

| Del<br>Esc<br>F1<br>Help | Undo Point (EF), Delete<br>Stop Command Iteration<br>Help<br>Help         |                                                                       |

#### or VHDL nd Save

- о Тор ndow

#### **Mouse Buttons Bindkey Chart**

#### Left Mouse Button – Select and Deselect

Click Select Point Double ClickExtend Select Shift ClickSelect Point (Add) Cntl ClickDeselect Point DrawthroughSelect Box or Direct Edit\* Shift DrawthroughSelect Box (Add) or Direct Edit\* Cntl DrawthroughDeselect Box or Direct Edit\* Click (EF)Add Point

\*Direct Edit applies only when over object.

#### Middle Mouse Button – Pop-Up Menus

Click Pop-Up Menus Click (EF)Pop-Up Menus Double Click (EF)Toggle Options Form

#### Right Mouse Button – Repeat, Zoom, Options

Click Repeat Last Command DrawthroughZoom In Shift DrawthroughZoom Out (EF) Command Options

#### **Schematic Editor Bindkey Chart**

| DESIGN<br>X Check and Save<br>S Save (not needed)<br>^s Save As                   | WINDOWzZoom In]Zoom In By 2[Zoom Out By 2 | u<br>U<br>m   | EDIT<br>Undo<br>Redo<br>Stretch                                                                             |

|-----------------------------------------------------------------------------------|-------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------|

| E Hierarchy–Descend Edit                                                          | ↓ Pan Down                                | C             | Сору                                                                                                        |

| e Hierarchy–Descend Read<br>Hierarchy–Edit In Place<br>Hierarchy–Show Scope       | ← Pan Left<br>→ Pan Right<br>↑ Pan Up     | M<br>Del<br>r | Move<br>Delete<br>Rotate                                                                                    |

| ^ e Hierarchy–Return<br>Hierarchy–Return To Top<br>Create Cellview<br>New<br>Open | f Fit<br>F6 Redraw<br>Utilities<br>Close  | q<br>Q        | Properties–Objects<br>Properties–Cellviews<br>Reset Invisible Labels<br>Component Display<br>Alternate View |

| Discard Edits<br>Make Read Only                                                   |                                           | ^ f           | Select–Filter<br>Search                                                                                     |

| Make Editable                                                                     |                                           | 5             | Route Flight                                                                                                |

| 9 Probe–Add Net<br>Plot                                                           |                                           |               |                                                                                                             |

| / Renumber Instances                                                              |                                           |               |                                                                                                             |

|   | ADD            |     | CHECK               |     | OPTIONS           |

|---|----------------|-----|---------------------|-----|-------------------|

| i | Instance       | х   | Current Cellview    | 0   | Editor            |

| W | Wire (narrow)  |     | Hierarchy           | 0   | Display           |

| W | Wire (wide)    |     | Options             | ^ f | Select Filter     |

| I | Wire Name      |     | Rules Setup         |     | Check             |

| р | Pin            |     | Label Attachment    |     | Check Rules Setup |

| b | Block          | g   | Find Marker         |     | Parameter Filter  |

|   | Net Expression | ^ g | Delete Marker       |     | Save Defaults     |

|   | Solder Dot     | C C | Delete All Markers  |     | Load Defaults     |

| L | Note–Text      |     | Simulation Monitors |     |                   |

| n | Note-Shape     |     |                     |     |                   |

#### **Symbol Editor Bindkey Chart**

|     | DESIGN                  | w             | NDOW          |     | EDIT                   |

|-----|-------------------------|---------------|---------------|-----|------------------------|

| Х   | Check and Save          | z             | Zoom In       | u   | Undo                   |

| S   | Save (not needed)       | ]             | Zoom In By 2  | U   | Redo                   |

| ^ s | Save As                 | [             | Zoom Out By 2 | m   | Stretch                |

| Е   | Hierarchy–Descend Edit  | $\downarrow$  | Pan Down      | с   | Сору                   |

| е   | Hierarchy–Descend Read  | $\leftarrow$  | Pan Left      | Μ   | Move                   |

|     | Hierarchy–Edit In Place | $\rightarrow$ | Pan Right     | Del | Delete                 |

|     | Hierarchy–Show Scope    | Ť             | Pan Up        | r   | Rotate                 |

| ^ e | Hierarchy–Return        | f             | Fit           | q   | Properties–Objects     |

|     | Hierarchy–Return To Top | F6            | Redraw        | Q   | Properties–Cellviews   |

|     | Create Cellview         |               | Utilities     |     | Reset Invisible Labels |

|     | New                     |               | Close         | ^ f | Select–Filter          |

|     | Open                    |               |               |     | Search                 |

|     | Discard Edits           |               |               |     | Origin                 |

|     | Make Read Only          |               |               |     |                        |

|     | Make Editable           |               |               |     |                        |

| 9   | Probe–Add Net           |               |               |     |                        |

|     | Plot                    |               |               |     |                        |

|   | ADD                      |     | CHECK              | (   | OPTIONS       |

|---|--------------------------|-----|--------------------|-----|---------------|

| р | Pin                      | х   | Cross View Check   | 0   | Editor        |

|   | Shape                    | g   | Find Marker        | 0   | Display       |

| I | Label                    | ^ g | Delete Marker      | ^ f | Select Filter |

|   | Selection Box            |     | Delete All Markers |     | Save Defaults |

| L | Note $\Rightarrow$ Text  |     |                    |     | Load Defaults |

| n | Note $\Rightarrow$ Shape |     |                    |     |               |

|   | Net Expression           |     |                    |     |               |

|   | Custom Pin               |     |                    |     |               |

Chap 3, Cadence, 5190/6190, Foster Dai, 2013

Import Symbol

### Layout Bindkey Map

| F keys                |             |     |                             |                |                              |                |  |

|-----------------------|-------------|-----|-----------------------------|----------------|------------------------------|----------------|--|

| F1                    | F2          | F3  | F4                          | F5             | F6                           | F7             |  |

| Help                  | Save        |     | Toggle<br>Partial<br>Select | Open<br>Design | Maintain<br>Connec-<br>tions | Guided<br>Path |  |

| F8                    | F9          | F10 | F11                         | F12            |                              |                |  |

| Guided<br>Path Create | Filter Size |     |                             |                |                              |                |  |

| Alphabet keys                          |                     |             |                 |                |  |  |

|----------------------------------------|---------------------|-------------|-----------------|----------------|--|--|

| Key to Map: 1=Top row is Control + key |                     |             |                 |                |  |  |

| 2=Middle row is                        | Shift + key         |             |                 |                |  |  |

| 3=Bottom row is                        | 3=Bottom row is key |             |                 |                |  |  |

| А                                      | В                   | С           | D               | E              |  |  |

| 1 Select All                           | 1                   | 1 Interrupt | 1 Deselect All  | 1              |  |  |

| 2 Select Area                          | 2 Return            | 2 Chop      | 2 Deselect Area | 2 Display Ops. |  |  |

| 3 Select                               | 3 Go to Level       | 3 Сору      | 3 Deselect      | 3 Edit Options |  |  |

### Layout Bindkey Map

| F                   | G                | н                     | I                       | J                |

|---------------------|------------------|-----------------------|-------------------------|------------------|

| 1 View O            | 1                |                       | 1                       |                  |

| 2 View 32           | 2 Zoom To Grid   |                       | 2                       |                  |

| 3 Fit All           | 3 Toggle Gravity |                       | 3 Create<br>Instance    |                  |

| К                   | L                | М                     | N Snap mode<br>options: | 0                |

| 1                   | 1                | 1                     | 1 diagonal              | 1                |

| 2 Clear Rulers      | 2                | 2 Merge               | 2 orthogonal            | 2 Rotate         |

| 3 Draw Rulers       | 3 Label          | 3 Move                | 3 L90XFirst             | 3 Create Contact |

| Р                   | Q                | R                     | S                       | Т                |

| 1 Create Pin        | 1                | 1 Redraw              | 1 Split                 | 1 Zoom to Set    |

| 2 Create<br>Polygon | 2 Design Prop    | 2 Reshape             | 2 Search                | 2 Tree           |

| 3 Create Path       | 3 Object Prop    | 3 Create<br>Rectangle | 3 Stretch               | 3 Layer Tap      |

| U                   | v                | w                     | x                       | Y                |

| 1                   | 1 Type in CIW    | 1 Close               | 1 Fit Edit              | 1 Cycle Select   |

| 2 Redo              | 2                | 2 Next View           | 2 Descend               | 2 Paste          |

| 3 Undo              | 3 Attach         | 3 Previous View       | 3 Edit-In-Place         | 3 Yank           |

| Z                   | Esc              | Tab                   | Delete                  | Back Space       |

| 1 Zoom In x2        | Cancel           | Pan                   | Delete                  | Undo Point       |

| 2 Zoom out x2       |                  |                       |                         |                  |

| 3 Zoom In           |                  |                       |                         |                  |

| Return              |                  |                       |                         |                  |

| Enter last point    |                  |                       |                         |                  |

### Layout Bindkey Map

| Arrow keys     |                     |            |  |  |  |  |

|----------------|---------------------|------------|--|--|--|--|

| Control + key: | Fit cell to portion | of window  |  |  |  |  |

| Shift + key: M | ove Cursor          |            |  |  |  |  |

| Key: Pan to po | ortion of cellview  |            |  |  |  |  |

| R7 Home        | R8 🛉                | R9 PgUp    |  |  |  |  |

| up left        | top                 | up right   |  |  |  |  |

| 👞 R10          | R11                 | R12        |  |  |  |  |

| left           | center              | right      |  |  |  |  |

| R13 End        | R14 ]               | R15 PgDn   |  |  |  |  |

| down left      | bottom              | down right |  |  |  |  |

| Symbol keys on arrow key pad |                                                                           |                                                                            |                              |                        |             |  |

|------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------|------------------------|-------------|--|

| = R4                         | / R5                                                                      | * R6                                                                       | -                            | +                      | Enter       |  |

| when used                    | Moves cursor<br>1 grid point<br>when used<br>with Shift and<br>arrow keys | Moves cursor<br>2 grid points<br>when used<br>with Shift and<br>arrow keys | Delete<br>reference<br>point | Set reference<br>point | Enter point |  |

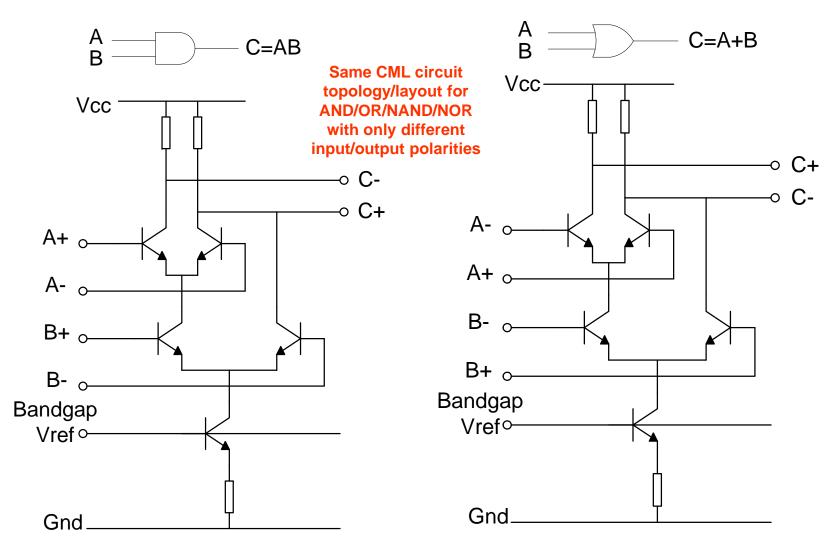

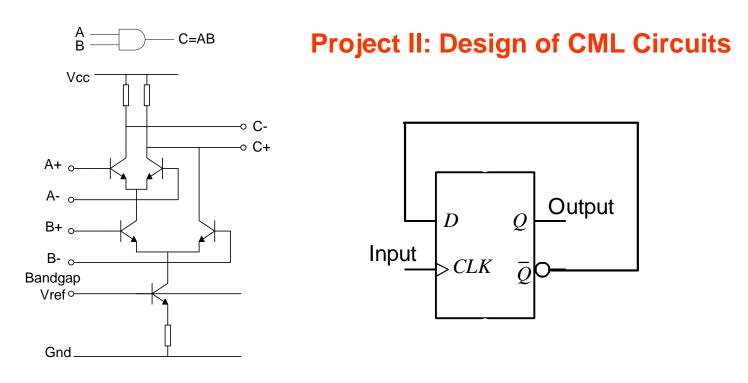

#### **Differential Current Mode Logic**

Chap 3, Cadence, 5190/6190, Foster Dai, 2013

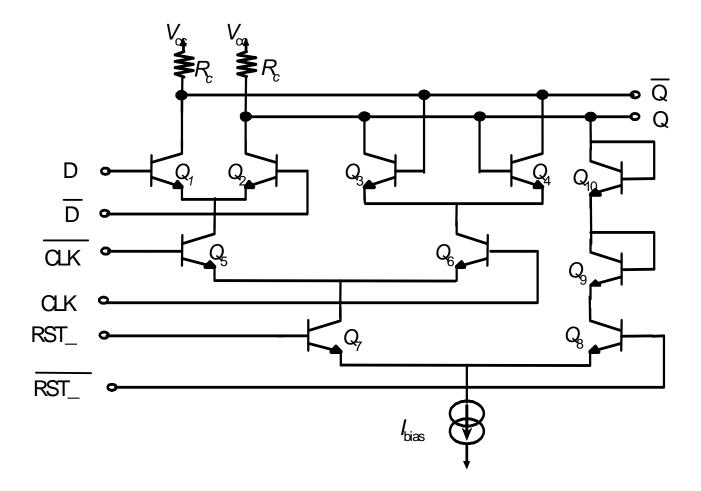

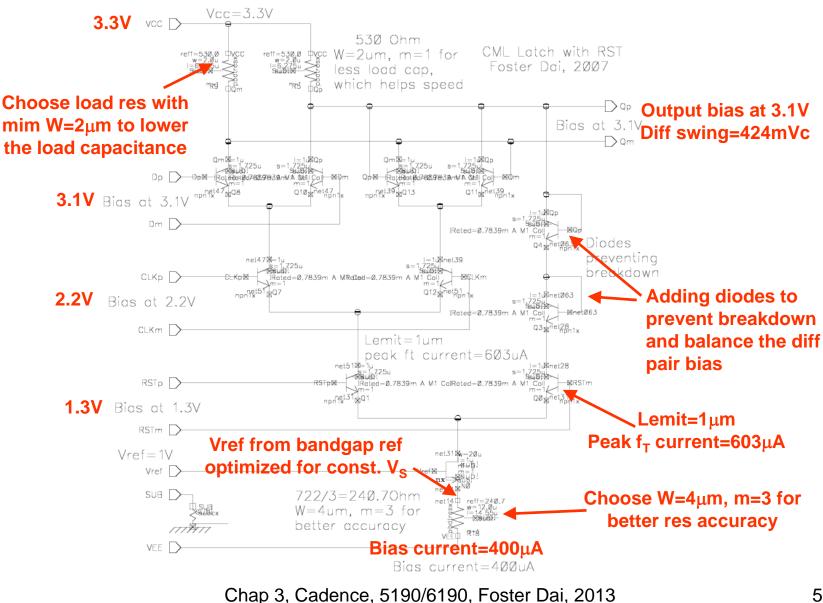

## CML latch with active low reset using 4-level transistors

## **Bias for Current Mode Logic**

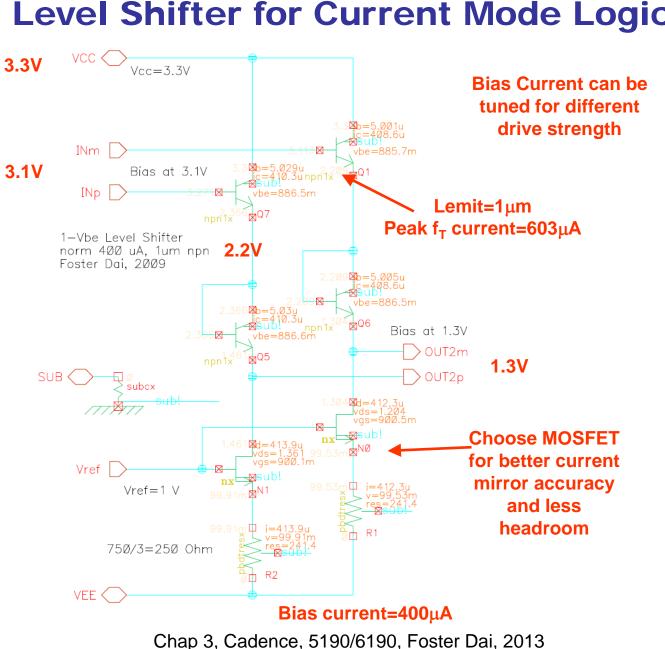

**Level Shifter for Current Mode Logic**

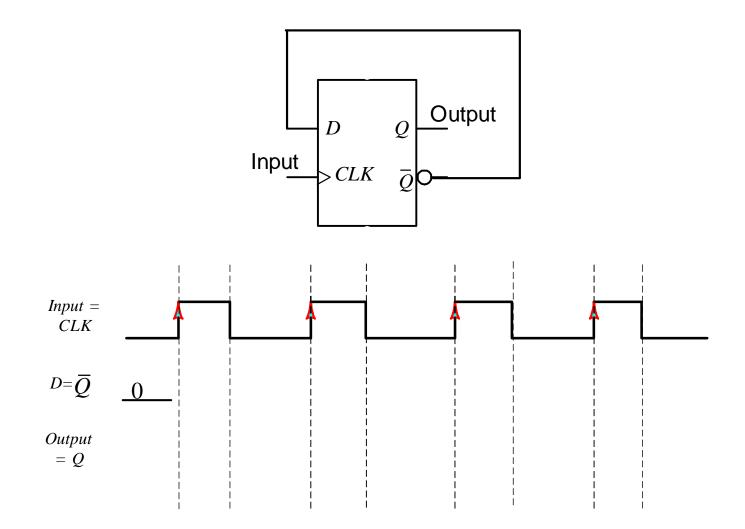

A Divided-By-2 Circuit

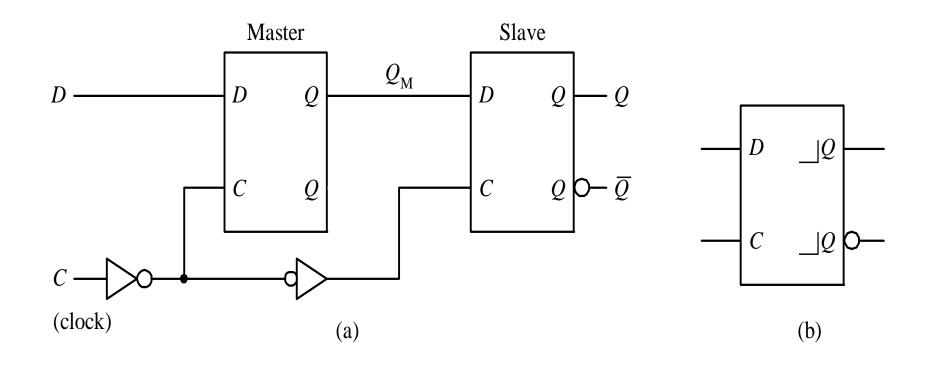

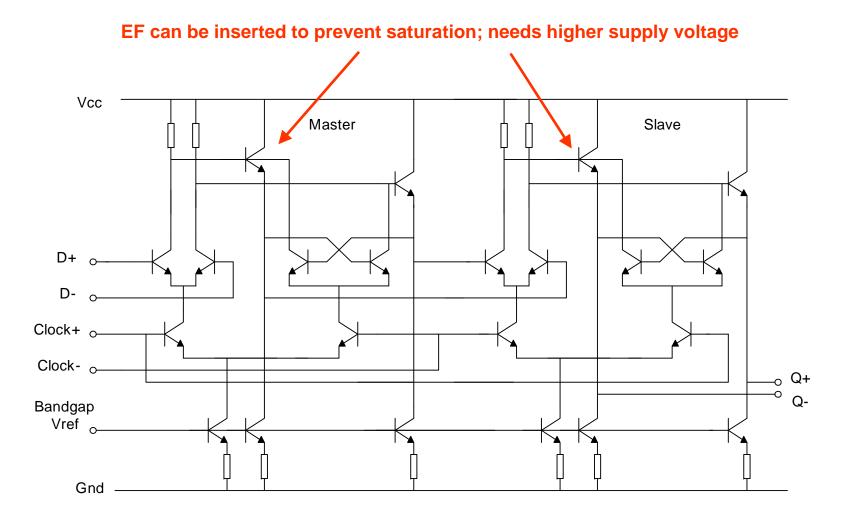

#### Master-Slave D Flip-Flop

#### **Current Mode Master-Slave D-Flip-Flop w. EF**

Chap 3, Cadence, 5190/6190, Foster Dai, 2013

57

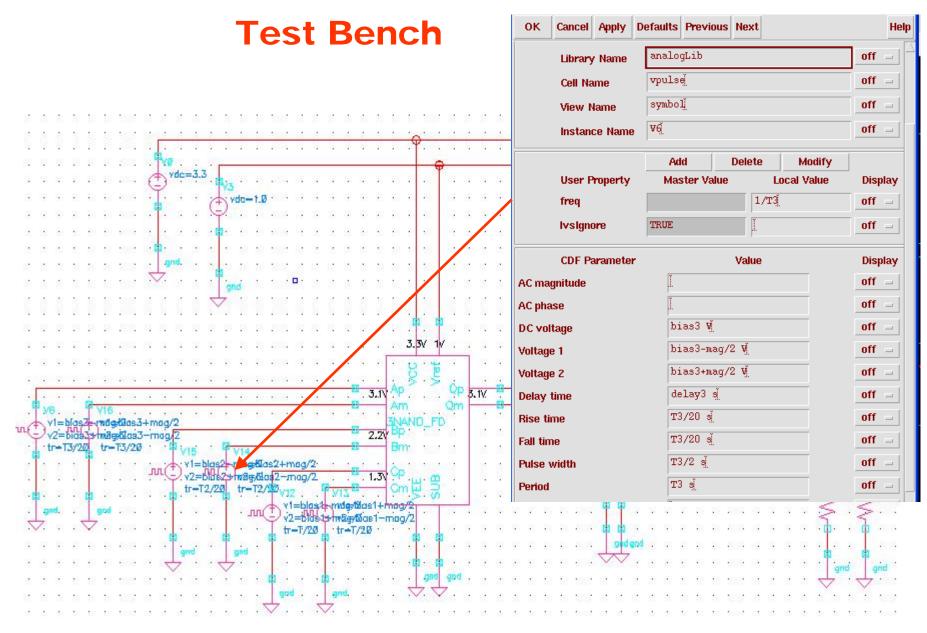

- Use minimum size npn transistors with Lemit=1um to design the following CML circuit:

- (1) 5130/6130: differential AND gate (left);

- (2) 6130 only: Divided by 2 circuit (right);

Project report due on Oct. 22, Email your report in yourname\_proj2.doc format to <u>daifa01@auburn.edu</u>. Report includes schematics and Cadence transient simulation results for input/output waveforms showing the maximum operation frequency.

### **Copy Cadence Schematic and Waveform to Word**

- 1. Copy .cdsplotinit to your launch directory. In schematic window, Choose "design → plot → deselect header → plot options → plotter name → send plot only to file". In waveform window, Choose "hardcopy → deselect header → plotter name → send plot only to file". It will generate a ps file in the specified directory.

- 2. You may also do printscreen. After editing it with MS Paint, you need to save it as .jpg format instead of the default .bmp format. Then you can insert the .jpg file in the word document using Insert --> Picture --> From File option. This way, the size of the .jpg file is approximately 30KB.

- 3. Another way is to use GhostView, GhostScript softwares to get the .jpg files. These softwares can be downloaded from: <u>http://www.cs.wisc.edu/~ghost/doc/AFPL/get811.htm</u>

- 4. In Cadence, you can get .ps file by selecting the Tools on the Command Interpreter Window and then Camera --> PostScript then select the window to get the .ps file. (you need to wait for sometime until the process is complete). This .ps file is opened with the ghostview software and converted into a .jpg format file which is later used in the word document as explained above.

- 5. Do your best to minimize the file size for your report.