# Lab 4 – Interrupt-driven operations

- Interrupt handling in Cortex-M CPUs

- Nested Vectored Interrupt Controller (NVIC)

- Externally-triggered interrupts via GPIO pins

- Software setup for interrupt-driven applications

# Interrupt-driven operations

- An interrupt is an event that initiates the automatic transfer of software execution from one program thread to an interrupt handler

- Event types:

- Signal from a "device" (keyboard, timer, data converter, etc.)

- Device external to the CPU (possibly within a microcontroller)

- Signals that a device needs, or is able to provide service

(i.e. device goes from "busy" to "ready")

- Asynchronous to the current program thread

- Allows CPU to do other work until device needs service!

- An internal event or "exception" caused by an instruction Ex. invalid memory address, divide by 0, invalid op code

- A software interrupt instruction

Ex. ARM Cortex SVC (supervisor call) instruction

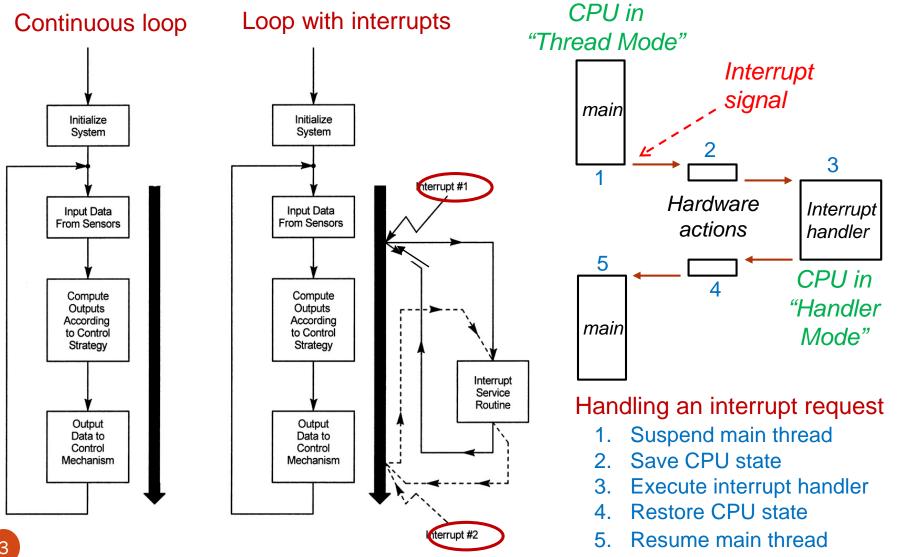

# Interrupts in control systems

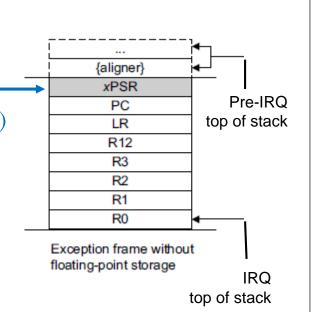

# Cortex-M Interrupt Process

(much of this is transparent when using C)

- 1. Interrupt signal detected by CPU

- 2. Suspend main program execution

- finish current instruction

- save CPU state (push registers onto stack)

- set LR to 0xFFFFFF9 (indicates interrupt return)

- set IPSR to interrupt number

- load PC with ISR address from vector table

- 3. Execute interrupt service routine (ISR)

- save other registers to be used <sup>1</sup>

- clear the "flag" that requested the interrupt

- perform the requested service

- communicate with other routines via global variables

- restore any registers saved by the ISR

- 4. Return to and resume main program by executing **BX LR**

- saved state is restored from the stack, including PC

<sup>1</sup> C compiler takes care of saving/restoring registers

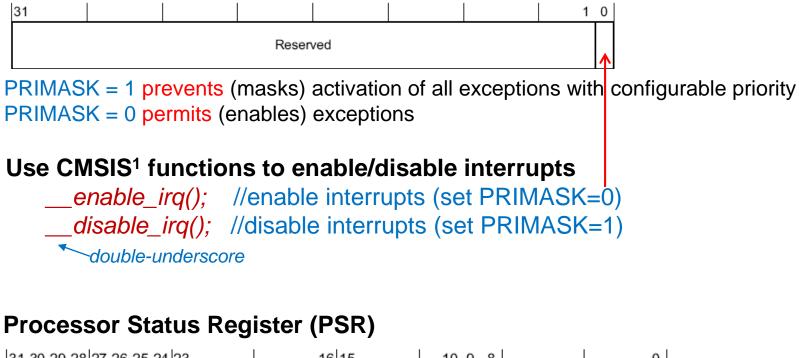

# Special CPU registers

### **Prioritized Interrupts Mask Register (PRIMASK)**

<sup>1</sup> **Cortex Microcontroller Software Interface Standard** – Functions for all ARM Cortex-M CPUs. Automatically included in your project; defined in header files: *core\_cmFunc.h, core\_cm3.h*

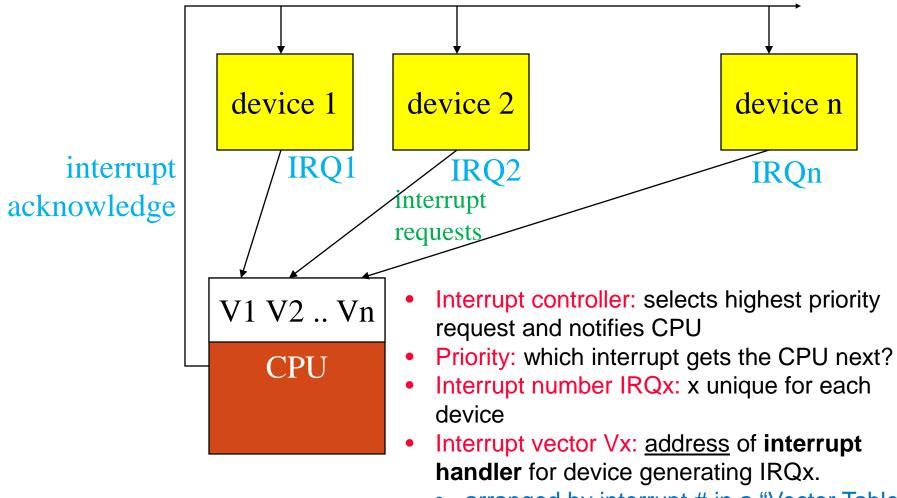

# Prioritized, vectored interrupts

arranged by interrupt # in a "Vector Table"

## Cortex-M CPU and peripheral exceptions

|                    |                                 | <b>Priority</b> <sup>1</sup> | IRQ# <sup>2</sup> | Notes                                                                                               |  |

|--------------------|---------------------------------|------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|--|

| US                 | Reset                           | -3                           |                   | Power-up or warm reset                                                                              |  |

|                    | NMI                             | -2                           | -14               | Non-maskable interrupt from peripheral or software                                                  |  |

|                    | HardFault                       | -1                           | -13               | Error during exception processing or no other handler                                               |  |

| ptio               | MemManage                       | Config                       | -12               | Memory protection fault (MPU-detected)                                                              |  |

| ARM CPU Exceptions | BusFault                        | Config                       | -11               | AHB data/prefetch aborts                                                                            |  |

|                    | UsageFault                      | Config                       | -10               | Instruction execution fault - undefined instruction, illegal unaligned access                       |  |

|                    | SVCcall                         | Config                       | -5                | System service call (SVC) instruction                                                               |  |

|                    | DebugMonitor                    | Config                       |                   | Break points/watch points/etc.                                                                      |  |

|                    | PendSV                          | Config                       | -2                | Interrupt-driven request for system service                                                         |  |

|                    | SysTick                         | Config                       | -1                | System tick timer reaches 0                                                                         |  |

|                    | IRQ0                            | Config                       | 0                 | Signaled by peripheral or by software request                                                       |  |

|                    | IRQ1 (etc.)                     | Config                       | 1                 | Signaled by peripheral or by software request                                                       |  |

|                    | -<br>endor peripher<br>IRQ0 IRC | -                            |                   | <ol> <li>Lowest priority # = highest priority</li> <li>IRQ# used in CMSIS function calls</li> </ol> |  |

7

|                        | Position | Priority | Type of priority | Acronym       | Description                                          | Address     |                        |

|------------------------|----------|----------|------------------|---------------|------------------------------------------------------|-------------|------------------------|

|                        | 0        | 7        | settable         | WWDG          | Window Watchdog interrupt                            | 0x0000_0040 | External<br>interrupts |

| Interrupt              | 1        | 8        | settable         | PVD           | PVD through EXTI Line detection<br>interrupt         | 0x0000_0044 |                        |

| Table for<br>STM32L1xx | 2        | 9        | settable         | TAMPER_STAMP  | Tamper and TimeStamp through<br>EXTI line interrupts | 0x0000_0048 |                        |

| Peripherals            | 3        | 10       | settable         | RTC_WKUP      | RTC Wakeup through EXTI line<br>interrupt            | 0x0000_004C |                        |

|                        | 4        | 11       | settable         | FLASH         | Flash global interrupt                               | 0x0000_0050 |                        |

|                        | 5        | 12       | settable         | RCC           | RCC global interrupt                                 | 0x0000_0054 |                        |

| IRQ6 →                 | 6        | 13       | settable         | EXTI0         | EXTI Line0 interrupt                                 | 0x0000_0058 |                        |

|                        | 7        | 14       | settable         | EXTI1         | EXTI Line1 interrupt                                 | 0x0000_005C |                        |

| Tech. Ref.             | 8        | 15       | settable         | EXTI2         | EXTI Line2 interrupt                                 | 0x0000_0060 |                        |

| Manual:                | 9        | 16       | settable         | EXTI3         | EXTI Line3 interrupt                                 | 0x0000_0064 |                        |

|                        | 10       | 17       | settable         | EXTI4         | EXTI Line4 interrupt                                 | 0x0000_0068 |                        |

| Table 48               | 11       | 18       | settable         | DMA1_Channel1 | DMA1 Channel1 global interrupt                       | 0x0000_006C |                        |

|                        | 10       | 40       | cattable         | DMA1 Channel? | DMA1 Channel? alshal internat                        | 0-000 0070  |                        |

| Also - refer           | 25       | 32       | settable         | TIM9          | TIM9 global interrupt                                | 0x0000_00A4 |                        |

| to vector              | 26       | 33       | settable         | TIM10         | TIM10 global interrupt                               | 0x0000_00A8 |                        |

| table in               | 27       | 34       | settable         | TIM11         | TIM11 global interrupt                               | 0x0000_00AC | Timer                  |

| startup                | 28       | 35       | settable         | TIM2          | TIM2 global interrupt                                | 0x0000_00B0 | interrupts             |

| code                   | 29       | 36       | settable         | TIM3          | TIM3 global interrupt                                | 0x0000_00B4 |                        |

| code                   | 30       | 37       | settable         | TIM4          | TIM4 global interrupt                                | 0x0000_00B8 |                        |

|                        | 31       | 38       | settable         | I2C1_EV       | I <sup>2</sup> C1 event interrupt                    | 0x0000_00BC |                        |

|                        | 32       | 39       | settable         | I2C1_ER       | I <sup>2</sup> C1 error interrupt                    | 0x0000_00C0 |                        |

|                        | 33       | 40       | settable         | 12C2_EV       | I <sup>2</sup> C2 event interrupt                    | 0x0000_00C4 |                        |

|                        | 34       | 41       | settable         | I2C2_ER       | I <sup>2</sup> C2 error interrupt                    | 0x0000_00C8 |                        |

| 8                      | 35       | 42       | settable         | SPI1          | SPI1 global interrupt                                | 0x000_00CC  |                        |

### STM32L1 vector table in startup code (partial)

#### \_Vectors

- DCD \_\_initial\_sp DCD Reset\_Handler

- DCD NMI\_Handler

- DCD SVC Handler ; SVCall Handler DCD DebugMon\_Handler ; Debug Monitor Handler DCD : Reserved 0 DCD PendSV\_Handler ; PendSV Handler SysTick\_Handler DCD ; SysTick Handler ; External Interrupts WWDG\_IRQHandler ; Window WatchDog DCD DCD **PVD IRQHandler** ; PVD via EXTI Line detection DCD TAMP\_STAMP\_IRQHandler ; Tamper/TimeStamps via EXTI ; RTC Wakeup via EXTI line RTC\_WKUP\_IRQHandler DCD FLASH\_IRQHandler DCD ; FLASH DCD RCC IRQHandler ; RCC DCD EXTI0 IRQHandler : EXTI Line0 Use these names EXTI1\_IRQHandler : EXTI Line1 DCD for your interrupt EXTI2\_IRQHandler : EXTI Line2 DCD handler functions EXTI3 IRQHandler : EXTI Line3 DCD DCD EXTI4 IRQHandler : EXTI Line4

- ; Pointer to top of Stack

- ; Reset Handler

- ; NMI Handler

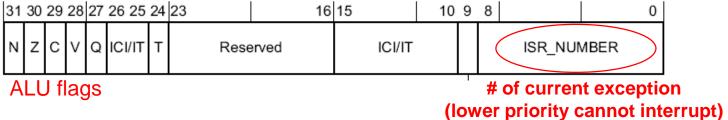

#### Interrupt signal: from device to CPU Peripheral Device ("Enabled" in three places) **Registers:** In <u>each</u> peripheral device: Flag Enable Each potential interrupt source has a separate **enable** bit xIE xF Set to enable the peripheral to send an interrupt signal to the CPU -7 Clear to prevent the peripheral from interrupting the CPU & Each potential interrupt source has a separate flag bit • Flag set by hardware when an "event" occurs > IRQn Interrupt request = (flag & enable) -Test flag in software if interrupt not desired ISR software must clear the flag to acknowledge the request Nested Vectored Interrupt Controller (NVIC • Receives all interrupt requests **NVIC** Each has an enable bit and a priority within the NVIC # of highest-priority enabled interrupt sent to the CPU PRIMASK Within the CPU: Global interrupt enable bit in PRIMASK register & **CPU** Interrupt if priority of IRQ < that of current thread Access interrupt vector table with IRQ# 10 Interrupt

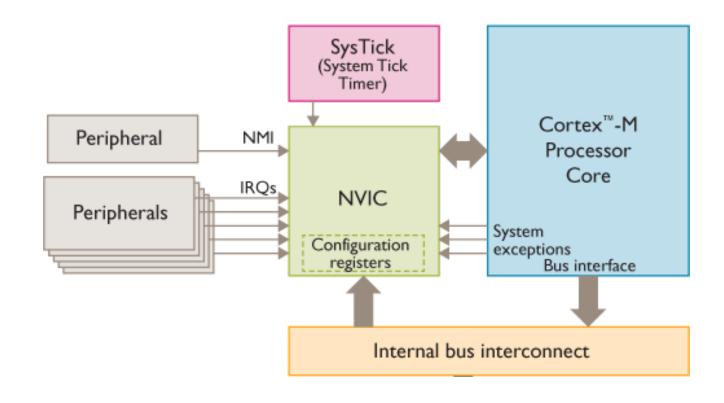

## Nested Vectored Interrupt Controller (NVIC)

- NVIC manages and prioritizes external interrupts in Cortex-M

- 45 IRQ sources from STM32L1xx peripherals

- NVIC interrupts CPU with IRQ# of highest-priority IRQ signal

- CPU uses IRQ# to access the vector table & get intr. handler start address

### NVIC setup: enable interrupts

- Each IRQ has its own **enable** bit within the NVIC

- NVIC only considers IRQs whose enable bits are set

- Interrupt Set Enable Register: each bit enables one interrupt

- CMSIS function: NVIC\_EnableIRQ(n); //set bit n to enable IRQn

- Interrupt Clear Enable Register: each bit disables one interrupt

- CMSIS function: NVIC\_DisableIRQ(n); //set bit n to disable IRQn

- For convenience, *stm32l1xx*.*h* defines symbols for each IRQn Examples: EXTIO\_IRQn = 6; //External interrupt EXTIO is IRQ #6 TIM3\_IRQn = 29; //TimerTIM3 interrupt is IRQ #29

### Usage:

NVIC\_EnableIRQ(EXTI0\_IRQn); //enable external interrupt EXTI0

NVIC\_DisableIRQ(TIM3\_IRQn); //disable interrupt from timer TIM3

### **NVIC:** interrupt pending flags

• Each IRQ has an **interrupt pending flag** within the NVIC

- Pending flag set by NVIC when it detects IRQn request, and IRQn status changed to "pending"

- IRQn status changes to "active" when its interrupt handler is entered

- NVIC clears pending flag when handler exited, changing status to "inactive"

- If IRQn still active when exiting handler, or IRQn reactivates while executing the handler, the pending flag remains set and triggers another interrupt

Avoid duplicate service by clearing IRQn pending flag in software:

CMSIS function: NVIC\_ClearPendingIRQ(IRQn);

- Pending status can be checked:

- CMSIS function: **NVIC\_GetPendingIRQ**(IRQn);

- Software can force IRQn into pending state to simulate an IRQn request

- CMSIS function: **NVIC\_SetPendingIRQ**(IRQn);

### **NVIC:** interrupt priorities

• Each IRQn assigned a **priority** within the NVIC

- NVIC selects highest-priority pending IRQ to send to CPU

- Lower priority# = higher priority (default value = 0)

- Higher priority interrupt can interrupt lower priority one

- Lower priority interrupt not sent to CPU until higher priority interrupt service completed

- If equal priorities, lower IRQ# selected

- Priorities stored in NVIC Interrupt Priority Registers

- STM32L1xx uses 4-bit priority value (0..15)

(NVIC registers allocate 8 bits per IRQ#, but vendors may use fewer bits)

• Set priority via CMSIS function: *NVIC\_SetPriority(IRQn, priority);*

Ex: *NVIC\_SetPriority(EXTIO\_IRQn, 1);* //set ext. intr. EXTI0 priority = 1

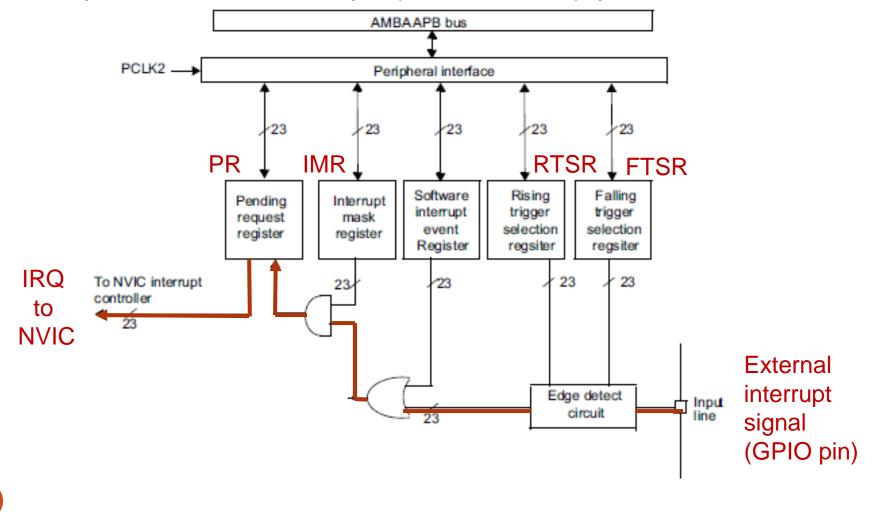

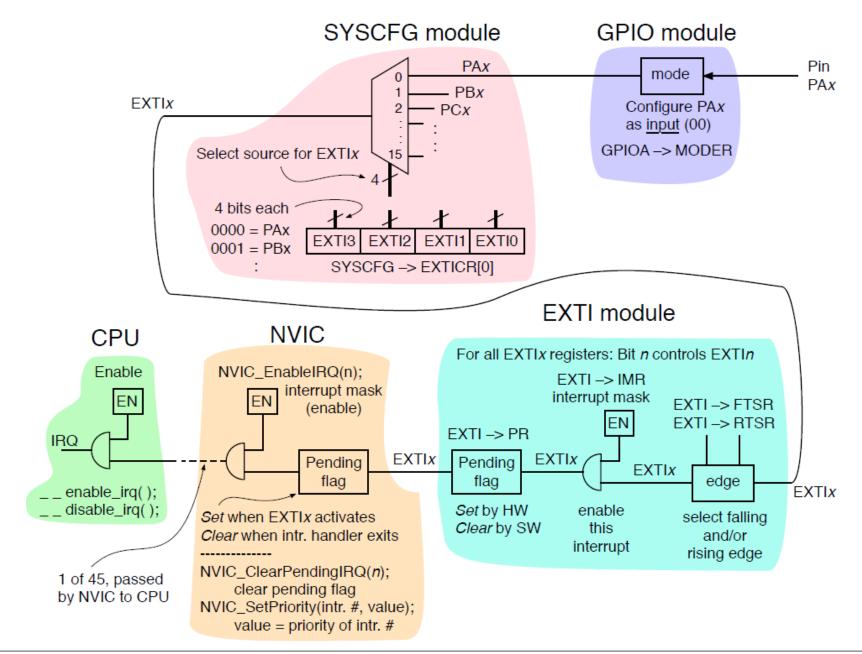

## STM32L1xx external interrupt/event controller

- External devices can interrupt CPU via GPIO pins (Some microcontrollers have dedicated interrupt pins)

- Up to 16 external interrupts (EXTI0-EXTI15), plus 7 internal events

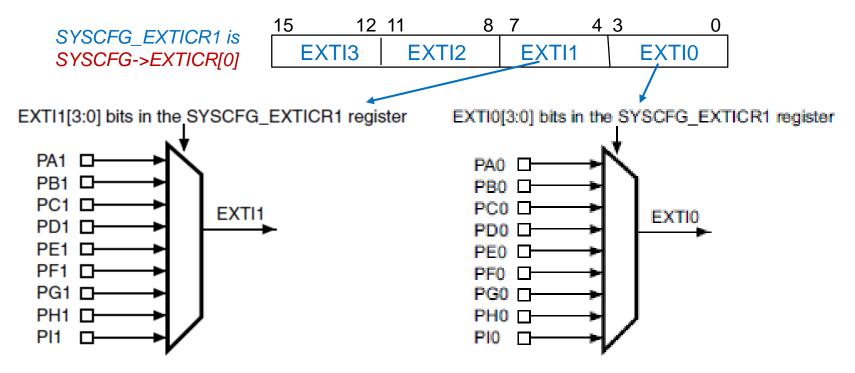

### STM32L1xx external interrupt sources (Select in System Configuration Module – SYSCFG)

- 16 multiplexers select GPIO pins as external interrupts EXTI0..EXTI15

- Mux inputs selected via 4-bit fields of EXTICR[k] registers (k=0..3)

- EXTIx = 0 selects PAx, 1 selects PBx, 2 selects PCx, etc.

- EXTICR[0] selects EXTI3-EXTI0; EXTICR[1] selects EXTI7-EXTI4, etc

Example: Select pin PC2 as external interrupt EXTI2 SYSCFG->EXTICR[0] &= 0xF0FF; //clear EXTI2 bit field SYSCFG->EXTICR[0] |= 0x0200; //set EXTI2 = 2 to select PC2

## STM32L1xx EXTI configuration registers

- Register bits 15-0 control EXTI15-EXTI0, respectively

- **EXTI\_RTSR/FTSR** rising/falling trigger selection register

- 1 to enable rising/falling edge to trigger the interrupt/event

- 0 to ignore the rising/falling edge

- **EXTI\_IMR** interrupt mask register

- 1 enables ("unmasks") the corresponding interrupt

- 0 disables ("masks") the interrupt

- **EXTI\_PR** interrupt pending register

- bit set to 1 by hardware if interrupt/event occurred (bit is readable)

- clear bit by writing 1 (writing 0 has no effect)

- **interrupt handler** must write **1** to this bit to clear the pending state of the interrupt (to cancel the IRQn request)

Example: Configure EXTI2 as rising-edge triggered

EXTI->RTSR |= 0x0004; //Bit2=1 to make EXTI2 rising-edge trig. EXTI->IMR |= 0x0004; //Bit2=1 to enable EXTI2 EXTI->PR |= 0x0004; //Bit2=1 to clear EXTI2 pending status

Clearing pending status needs to be done in the interrupt handler after every interrupt.

## Project setup for interrupt-driven applications

- 1. Write an **interrupt handler** for each peripheral

- Clear the flag that requested the interrupt (acknowledge the intr. request)

- Perform the desired action(s)

- communicate with other functions via shared global variables

- Use function names from the startup file vector table

Example: void EXTI4\_IRQHandler () { statements }

- 2. Perform all **initialization** for each peripheral device:

- Initialize the device, "enable" its interrupt, and clear its "flag" Example: External interrupt EXTIn

- Configure GPIO pin n as a digital input

- Select the pin as the EXTIn source (in SYSCFG module)

- Enable interrupt to be requested when a flag is set by the desired event (rising/falling edge)

- Clear the pending flag (to ignore any previous events)

- NVIC

- Enable interrupt: NVIC\_EnableIRQ (IRQn);

- Set priority (if desired): NVIC\_SetPriority (IRQn, priority);

- Clear pending status: NVIC\_ClearPendingIRQ (IRQn);

- 3. Initialize counters, pointers, global variables, etc.

- 4. Enable CPU Interrupts: <u>\_\_\_enable\_\_irq();</u>

(diagram on next slide)

### Signal flow/setup for External Interrupt EXTIx, x = 0...15

19

# Lab experiment

- Main program displays two counting sequences on LEDs,

- First increases at period  $\frac{1}{2}$  second from 0-9 & repeat

- Second increases at period 1 second from 0-9 & repeat

- If **user button** (connected to PA0) pressed, interrupt the main program and change count direction to decreasing

- If "Static IO" button (connect to PA1) pressed, interrupt the main program and change count direction to increasing (no change if new direction = old direction)

- Each interrupt should toggle one of the on-board LEDs

- Interrupt routines can set a global "direction" variable