# Analog Integrated Circuits

John Choma, Jr.

University of Southern California

| 1 | Monolithic Device Models Bogdan M. Wilamowski, Guofu Niu,  John Choma, Jr., Stephen I. Long, Nhat M. Nguyen, and Martin A. Brooke                                                                     |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Analog Circuit Cells Kenneth V. Noren, John Choma, Jr., J. Trujillo, David G. Haigh, Bill Redman-White, Rahim Akbari-Dilmaghani, Mohammed Ismail, Shu-Chuan Huang, Chung-Chih Hung, and Trond Saether |

| 3 | High-Performance Analog Circuits Chris Toumazou, Alison Payne,  John Lidgey, Alicja Konczakowska, and Bogdan M. Wilamowski                                                                            |

| 4 | RF Communication Circuits Michiel Steyaert, Wouter De Cock,<br>and Patrick Reynaert                                                                                                                   |

| 5 | PLL Circuits Muh-Tian Shiue and Chorng-Kuang Wang                                                                                                                                                     |

# Monolithic Device Models

|                                                                                                                                                                                 | 1.1 Bipolar Junction Transistor                                                                   | 1-1          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------|

|                                                                                                                                                                                 | Ebers-Moll Model • Gummel-Poon Model • Current                                                    |              |

|                                                                                                                                                                                 | Gains of Bipolar Transistors • High-Current                                                       |              |

|                                                                                                                                                                                 | Phenomena • Small-Signal Model • Technologies • Model                                             |              |

|                                                                                                                                                                                 | Parameters • SiGe HBTs                                                                            |              |

|                                                                                                                                                                                 | References                                                                                        | 1-20         |

|                                                                                                                                                                                 | 1.2 Metal-Oxide-Silicon Field Effect Transistor Introduction • Channel Charge • Volt-Ampere       | 1-21         |

| Bogdan M. Wilamowski                                                                                                                                                            | Characteristics • Transistor Capacitances • Small-Signal                                          |              |

| Auburn University                                                                                                                                                               | Operation • Design-Oriented Analysis Strategy                                                     |              |

| O of MI                                                                                                                                                                         | References                                                                                        | <b>1</b> -81 |

| Guofu Niu aburn University  Ohn Choma, Jr. niversity of Southern California  tephen I. Long niversity of California, Santa Barbara  Ihat M. Nguyen ambus Inc.  Martin A. Brooke | 1.3 JFET, MESFET, and HEMT Technology and Devices<br>Introduction • Silicon JFET Device Operation | 1-82         |

| John Choma, Jr.                                                                                                                                                                 | and Technology • Compound Semiconductor FET Technologies • Conclusion                             |              |

| Oniversity of bouthern dunformu                                                                                                                                                 | References                                                                                        | 1-101        |

| Stephen I. Long University of California, Santa Barbara                                                                                                                         | 1.4 Passive Components                                                                            | 1-103        |

| Nhat M. Nauvon                                                                                                                                                                  | References                                                                                        | 1-131        |

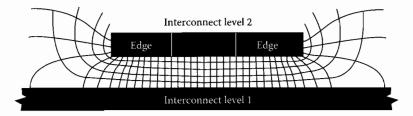

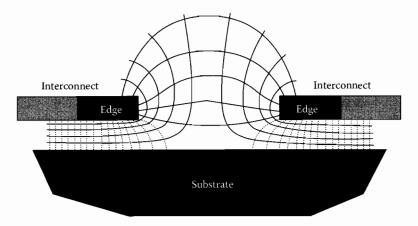

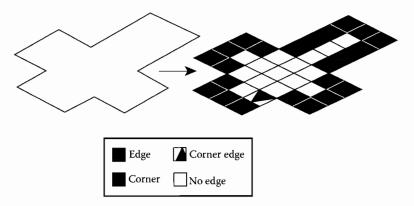

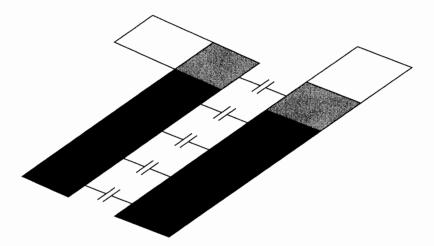

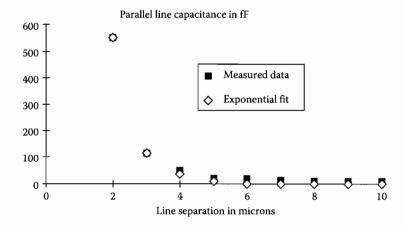

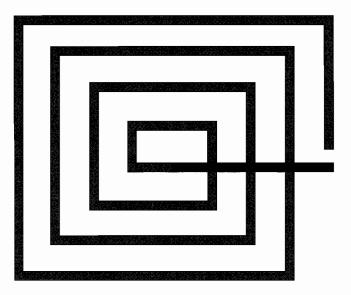

| Rambus Inc.                                                                                                                                                                     | 1.5 Chip Parasitics in Analog Integrated Circuits<br>Interconnect Parasitics • Pad and Packaging  | 1-132        |

| Martin A. Brooke                                                                                                                                                                | Parasitics • Parasitic Measurement                                                                |              |

| Georgia Institute of Technology                                                                                                                                                 | References                                                                                        | 1-145        |

# 1.1 Bipolar Junction Transistor

# Bogdan M. Wilamowski and Guofu Niu

The bipolar junction transistor (BJT) is historically the first solid-state analog amplifier and digital switch, and formed the basis of integrated circuits (ICs) in the 1970s. Starting in the early 1980s, the MOSFET had gradually taken over, particularly for main stream digital ICs. However, in the 1990s, the invention of silicon-germanium base heterojunction bipolar transistor (SiGe HBT) brought the bipolar transistor back into high-volume commercial production, mainly for the now widespread wireless and wire line communications applications. Today, SiGe HBTs are used to design radio-frequency (RF) ICs and systems for cell phones, wireless local area network (WLAN), automobile collision avoidance

radar, wireless distribution of cable television, millimeter wave radios, and many more applications, due to its outstanding high-frequency performance and ability to integrate with CMOS for realizing digital, analog, and RF functions on the same chip.

Below we first introduce the basic concepts of BJT using a historically important equivalent circuit model, the Ebers-Moll model. Then the Gummel-Poon model is introduced, as it is widely used for computer-aided design, and is the basis of modern BJT models like the VBIC, Mextram, and HICUM models. Current gain, high-current phenomena, fabrication technologies, and SiGe HBTs are then discussed.

#### 1.1.1 Ebers-Moll Model

A NPN BJT consists of two closely spaced PN junctions connected back to back sharing the same p-type region, as shown in Figure 1.1a. The drawing is not drawn to scale. The emitter and base layers are thin, typically less than 1  $\mu$ m, and the collector is much thicker to support a high output voltage swing. For forward mode operation, the emitter-base (EB) junction is forward biased, and the collector-base (CB) junction is reverse biased. Minority carriers are injected from emitter to base, travel across the base, and are then collected by the reverse biased CB junction. Therefore, the collector current is transported from the EB junction, and thus proportional to the EB junction current. In the forward-active mode, the current-voltage characteristic of the EB junction is described by the well-known diode equation

$$I_{\rm EF} = I_{\rm E0} \left[ \exp\left(\frac{V_{\rm BE}}{V_{\rm T}}\right) - 1 \right] \tag{1.1}$$

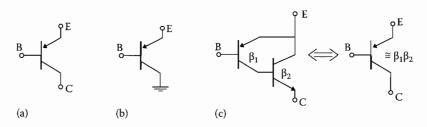

FIGURE 1.1 (a) Cross-sectional view of a NPN BJT. (b) Circuit symbol. (c) The Ebers-Moll equivalent circuit model.

where

$I_{\rm E0}$  is the EB junction saturation current

$V_{\rm T} = kT/q$  is the thermal potential (about 25 mV at room temperature)

The collector current is typically smaller than the emitter current  $I_{CF} = \alpha_F I_{EF}$ , where  $\alpha_F$  is the forward current gain.

Under reverse mode operation, the CB junction is forward biased and the EB junction is reverse biased. Like in the forward mode, the forward biased CB junction current gives the collector current

$$I_{\rm CF} = I_{\rm C0} \left[ \exp\left(\frac{V_{\rm BC}}{V_{\rm T}}\right) - 1 \right] \tag{1.2}$$

where  $I_{\rm C0}$  is the CB junction saturation current. Similarly  $I_{\rm ER} = \alpha_R I_R$ , where  $\alpha_R$  is the reverse current gain. Under general biasing conditions, it can be proven that to first order, a superposition of the above described forward and reverse mode equivalent circuits can be used to describe transistor operation, as shown in Figure 1.1b. The forward transistor operation is described by Equation 1.1, and the reverse transistor operation is described by Equation 1.2. From the Kirchoff's current law one can write  $I_{\rm C} = I_{\rm CF} - I_{\rm CR}$ ,  $I_{\rm E} = I_{\rm EF} - I_{\rm ER}$ , and  $I_{\rm B} = I_{\rm E} - I_{\rm C}$ . Using Equations 1.1 and 1.2 the emitter and collector currents can be described as

$$\begin{split} I_{\rm E} &= a_{11} \left( \exp \frac{V_{\rm BE}}{V_{\rm T}} - 1 \right) - a_{12} \left( \exp \frac{V_{\rm BC}}{V_{\rm T}} - 1 \right) \\ I_{\rm C} &= a_{21} \left( \exp \frac{V_{\rm BE}}{V_{\rm T}} - 1 \right) - a_{22} \left( \exp \frac{V_{\rm BC}}{V_{\rm T}} - 1 \right) \end{split} \tag{1.3}$$

which are known as the Ebers-Moll equations [1]. The Ebers-Moll coefficients  $a_{ij}$  are given as

$$a_{11} = I_{E0}, \quad a_{12} = \alpha_R I_{C0}, \quad a_{21} = \alpha_F I_{E0}, \quad a_{22} = I_{C0}$$

(1.4)

The Ebers-Moll coefficients are a very strong function of the temperature

$$a_{ij} = K_x T^m \exp \frac{V_{go}}{V_T} \tag{1.5}$$

where

$K_x$  is proportional to the junction area and independent of the temperature

$V_{\rm go} = 1.21 \text{ V}$  is the bandgap voltage in silicon (extrapolated to 0 K)

m is a material constant with a value between 2.5 and 4

When both EB and CB junctions are forward biased, the transistor is called to be working in the saturation region. Current injection through the collector junction may activate parasitic transistors in ICs using p-type substrate, where base acts as emitter, collector as base, and substrate as collector. In typical ICs, bipolar transistors must not operate in saturation. Therefore, for the integrated bipolar transistor the Ebers–Moll equations can be simplified to the form

$$\begin{split} I_{\rm E} &= a_{11} \left( \exp \frac{V_{\rm BE}}{V_{\rm T}} - 1 \right) \\ I_{\rm C} &= a_{21} \left( \exp \frac{V_{\rm BE}}{V_{\rm T}} - 1 \right) \end{split} \tag{1.6}$$

where  $a_{21}/a_{11} = \alpha_F$ . This equation corresponds to the circuit diagram shown in Figure 1.1c.

#### 1.1.2 Gummel-Poon Model

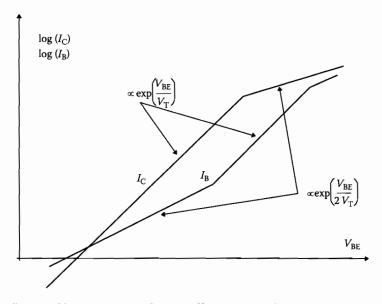

In real bipolar transistors the current voltage characteristics are more complex than those described by the Ebers-Moll equations. Typical current-voltage characteristics of the bipolar transistor, plotted in semilogarithmic scale, are shown in Figure 1.2. At small-base emitter voltages, due to the generation-recombination phenomena, the base current is proportional to

$$I_{\rm BL} \propto \exp \frac{V_{\rm BE}}{2V_{\rm T}} \tag{1.7}$$

Also, due to the base conductivity modulation at high-level injections, the collector current for larger voltages can be expressed by the similar relation

$$I_{\rm CH} \propto \exp \frac{V_{\rm BE}}{2V_{\rm T}} \tag{1.8}$$

Note, that the collector current for wide range is given by

$$I_{\rm C} = I_{\rm s} \exp \frac{V_{\rm BE}}{V_{\rm T}} \tag{1.9}$$

The saturation current is a function of device structure parameters

$$I_{s} = \frac{qAn_{i}^{2}V_{T}\mu_{B}}{\int_{0}^{\infty}N_{B}(x)dx}$$

(1.10)

where

$q = 1.6 \times 10^{-19}$  C is the electron charge

A is the EB junction area

$n_i$  is the intrinsic concentration ( $n_i = 1.5 \times 10^{10}$  at 300 K)

$\mu_B$  is the mobility of the majority carriers in the transistor base

$w_B$  is the effective base thickness

$N_{\rm B}(x)$  is the distribution of impurities in the base

FIGURE 1.2 Collector and base currents as a function of base-emitter voltage.

Note, that the saturation current is inversely proportional to the total impurity dose in the base. In the transistor with the uniform base, the saturation current is given by

$$I_{\rm s} = \frac{qAn_i^2 V_{\rm T} \mu_{\rm B}}{w_{\rm B} N_{\rm B}} \tag{1.11}$$

When a transistor operates in the reverse-active mode (emitter and collector are switched) then the current of such biased transistor is given by

$$I_{\rm E} = I_{\rm s} \exp \frac{V_{\rm BC}}{V_{\rm T}} \tag{1.12}$$

Note, that the  $I_s$  parameter is the same for forward and reverse mode of operation. The Gummel-Poon transistor model [2] was derived from the Ebers-Moll model using the assumption that  $a_{12} = a_{21} = I_s$ . For the Gummel-Poon model, Equations 1.3 are simplified to the form

$$I_{E} = I_{s} \left( \frac{1}{\alpha_{F}} \exp \frac{V_{BE}}{V_{T}} - \exp \frac{V_{BC}}{V_{T}} \right)$$

$$I_{C} = I_{s} \left( \exp \frac{V_{BE}}{V_{T}} - \frac{1}{\alpha_{R}} \exp \frac{V_{BC}}{V_{T}} \right)$$

(1.13)

These equations require only three coefficients, while the Ebers-Moll requires four. The saturation current  $I_s$  is constant for a wide range of currents. The current gain coefficients  $\alpha_F$  and  $\alpha_R$  have values smaller, but close to unity. Often instead of using the current gain as  $\alpha = I_C/I_E$ , the current gain  $\beta$  as a ratio of the collector current to the base current  $\beta = I_C/I_B$  is used. The mutual relationships between  $\alpha$  and  $\beta$  coefficients are given by

$$\alpha_F = \frac{\beta_F}{\beta_F + 1}, \quad \beta_F = \frac{\alpha_F}{1 - \alpha_F}, \quad \alpha_R = \frac{\beta_R}{\beta_R + 1}, \quad \beta_R = \frac{\alpha_R}{1 - \alpha_R} \tag{1.14}$$

The Gummel-Poon model was implemented in Simulation Program with Integrated Circuit Emphasis (SPICE) [3] and other computer programs for circuit analysis. To make the equations more general, the material parameters  $\eta_F$  and  $\eta_R$  were introduced

$$I_{\rm C} = I_{\rm s} \left[ \exp \frac{V_{\rm BE}}{\eta_{\rm F} V_{\rm T}} - \left( 1 + \frac{1}{\beta_{\rm R}} \right) \exp \frac{V_{\rm BC}}{\eta_{\rm R} V_{\rm T}} \right]$$

(1.15)

The values of  $\eta_F$  and  $\eta_R$  vary from 1 to 2.

# 1.1.3 Current Gains of Bipolar Transistors

The transistor current gain  $\beta$  is limited by two phenomena: base transport efficiency and emitter injection efficiency. The effective current gain  $\beta$  can be expressed as

$$\frac{1}{\beta} = \frac{1}{\beta_{\rm I}} + \frac{1}{\beta_{\rm T}} + \frac{1}{\beta_{\rm R}} \tag{1.16}$$

where

$\beta_I$  is the transistor current gain caused by emitter injection efficiency

$\beta_T$  is the transistor current gain caused by base transport efficiency

$\beta_R$  is the recombination component of the current gain

As one can see from Equation 1.16, smaller values of  $\beta_I$ ,  $\beta_T$ , and  $\beta_R$  dominate. The base transport efficiency can be defined as a ratio of injected carriers into the base, to the carriers that recombine within the base. This ratio is also equal to the ratio of the minority carrier life time, to the transit time of carriers through the base. The carrier transit time can be approximated by an empirical relationship

$$\tau_{\text{transit}} = \frac{w_{\text{B}}^2}{V_{\text{T}} \mu_{\text{B}} (2 + 0.9 \eta)}, \quad \eta = \ln \left( \frac{N_{\text{BE}}}{N_{\text{BC}}} \right)$$

(1.17)

where

$\mu_B$  is the mobility of the minority carriers in base

$w_{\rm B}$  is the base thickness

$N_{\rm BE}$  is the impurity doping level at the emitter side of the base

$N_{\mathrm{BC}}$  is the impurity doping level at the collector side of the base

Therefore, the current gain due to the transport efficiency is

$$\beta_{\rm T} = \frac{\tau_{\rm life}}{\tau_{\rm transit}} = (2 + 0.9\eta) \left(\frac{L_{\rm B}}{w_{\rm B}}\right)^2 \tag{1.18}$$

where  $L_B = \sqrt{V_T \mu_B \tau_{life}}$  is the diffusion length of minority carriers in the base.

The current gain  $\beta_I$ , due to the emitter injection efficiency, is given

$$\beta_{\rm I} = \frac{\mu_{\rm B} \int\limits_{0}^{w_{\rm E}} N_{\rm Eeff}(x) \mathrm{d}x}{\mu_{\rm E} \int\limits_{0}^{\infty} N_{\rm B}(x) \mathrm{d}x}$$

(1.19)

where

$\mu_B$  and  $\mu_E$  are minority carrier mobilities in the base and in the emitter

$N_{\rm B}(x)$  is impurity distribution in the base

$N_{\text{Eeff}}$  is the effective impurity distribution in the emitter

The recombination component of current gain  $\beta_R$  is caused by the different current-voltage relationship of base and collector currents as can be seen in Figure 1.2. The slower base current increase is due to the recombination phenomenon within the depletion layer of the base-emitter junction. Since the current gain is a ratio of the collector current to the base current, the relation for  $\beta_R$  can be found as

$$\beta_{R} = K_{R0} I_{C}^{1 - (1/\eta_{R})} \tag{1.20}$$

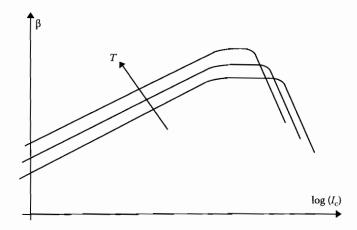

As it can be seen from Figure 1.2, the current gain  $\beta$  is a function of the current. This gain-current relationship is illustrated in Figure 1.3. The range of a constant current gain is wide for bipolar transistors with a technology characterized by a lower number of generation-recombination centers.

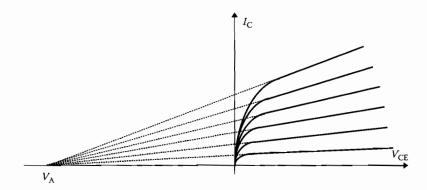

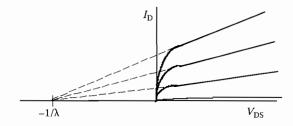

With an increase of CB voltage, the depletion layer penetrates deeper into the base. Therefore, the effective thickness of the base decreases. This leads to an increase of transistor current gain with applied collector voltages. Figure 1.4 illustrates this phenomenon, which is known as the Early's effect. The extensions of transistor characteristics (dotted lines in Figure 1.4) are crossing the voltage axis at

FIGURE 1.3 Current gain β as a function of collector current.

FIGURE 1.4 Current-voltage characteristics of a bipolar transistor.

the point  $-V_A$ , where  $V_A$  is known as the Early voltage. The current gain  $\beta$ , as a function of collector voltage, is usually expressed using the relation

$$\beta = \beta_{\rm o} \left( 1 + \frac{V_{\rm CE}}{V_{\rm A}} \right) \tag{1.21}$$

Similar equation can be defined for the reverse mode of operation.

# 1.1.4 High-Current Phenomena

The concentration of minority carriers increases with the rise of transistor currents. When the concentration of moving carriers exceeds a certain limit, the transistor property degenerates. Two phenomena are responsible for this limitation. The first is related to the high concentration of moving carriers (electrons in the NPN transistor) in the base–collector depletion region. This is known as the Kirk effect. The second phenomenon is caused by a high level of carriers injected into the base. When the concentration of injected minority carriers in the base exceeds the impurity concentration there, then the base conductivity modulation limits the transistor performance.

To understand the Kirk effect consider the NPN transistor in forward-active mode with the base-collector junction reversely biased. The depletion layer consists of the negative lattice charge of the base

region and the positive lattice charge of the collector region. Boundaries of the depletion layer are such that total the positive and negative charges are equal. When a collector current, carrying negatively charged electrons, flows through the junction, effective negative charge on the base side of junction increases. Also, the positive lattice charge of the collector side of the junction is compensated by negative charge of moving electrons. This way, the CB space charge region moves toward the collector, resulting in a thicker effective base. With a large current level, the thickness of the base may be doubled or tripled. This phenomenon, known as the Kirk effect, becomes very significant when the charge of moving electrons exceeds the charge of the lightly doped collector  $N_{\rm C}$ . The threshold current for the Kirk effect is given by

$$I_{\text{max}} = qA\nu_{\text{sat}}N_{\text{C}} \tag{1.22}$$

where  $v_{sat}$  is the saturation velocity for electrons ( $v_{sat} = 10^7$  cm/s for silicon).

The conductivity modulation in the base, or high-level injection, starts when the concentration of injected electrons into the base exceeds the lowest impurity concentration in the base  $N_{\rm Bmin}$ . This occurs for the collector current  $I_{\rm max}$  given by

$$I_{\text{max}} < qAN_{\text{Bmax}}, \quad \nu = \frac{qAV_{\text{T}}\mu_{\text{B}}N_{\text{Bmax}}(2 + 0.9\eta)}{w_{\text{B}}}$$

(1.23)

The above equation is derived using Equation 1.17 for the estimation of base transient time.

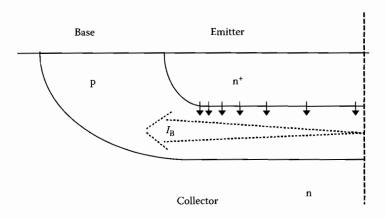

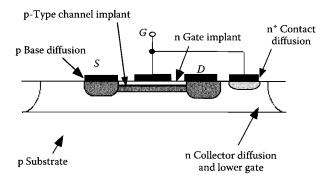

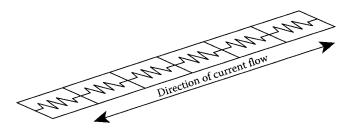

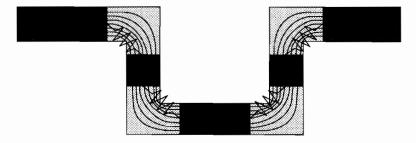

The high-current phenomena are significantly enlarged by the current crowding effect. The typical cross section of bipolar transistor is shown in Figure 1.5. The horizontal flow of the base current results in the voltage drop across the base region under the emitter. This small voltage difference on the base-emitter junction causes a significant difference in the current densities at the junction. This is due to the very nonlinear junction current-voltage characteristics. As a result, the base-emitter junction has very nonuniform current distribution across the junction. Most of the current flows through the part of the junction closest to base contact. For transistors with larger emitter areas, the current crowding effect is more significant. This nonuniform transistor current distribution makes the high-current phenomena, such as the base conductivity modulation and the Kirk effect, start for smaller currents than given by Equations 1.22 and 1.23. The current crowding effect is also responsible for the change of the effective base resistance with a current. As base current increases, the larger part of emitter current flows closer to the base contact, and the effective base resistance decreases.

FIGURE 1.5 Current crowding effect.

## 1.1.5 Small-Signal Model

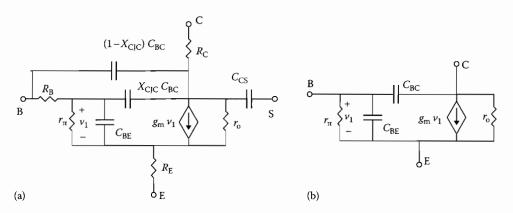

Small-signal transistor models are essential for AC circuit design. The small-signal equivalent circuit of the bipolar transistor is shown in Figure 1.6a. The lumped circuit shown in Figure 1.6a is only an approximation. In real transistors resistances and capacitances have a distributed character. For most design tasks, this lumped model is adequate, or even the simple equivalent transistor model shown in Figure 1.6b can be considered. The small-signal resistances,  $r_{\pi}$  and  $r_{o}$ , are inversely proportional to the transistor currents, and the transconductance  $g_{m}$  is directly proportional to the transistor currents

$$r_{\pi} = \frac{\eta_{\rm F} V_{\rm T}}{I_{\rm B}} = \frac{\eta_{\rm F} V_{\rm T} \beta_{\rm F}}{I_{\rm C}}, \quad r_{\rm o} = \frac{V_{\rm A}}{I_{\rm C}}, \quad g_{\rm m} = \frac{I_{\rm C}}{\eta_{\rm F} V_{\rm T}}$$

(1.24)

where

$\eta_F$  is the forward emission coefficient, ranging form 1.0 to 2.0

$V_{\rm T}$  is the thermal potential ( $V_{\rm T} = 25~{\rm mV}$  at room temperature)

Similar equations to Equation 1.24 can be written for the reverse transistor operation as well.

The series base, emitter, and collector resistances  $R_{\rm B}$ ,  $R_{\rm E}$ , and  $R_{\rm C}$  are usually neglected for simple analysis (Figure 1.6b). However, for high-frequency analysis it is essential to use at least the base series resistance  $R_{\rm B}$ . The series emitter resistance  $R_{\rm E}$  usually has a constant, bias-independent value. The collector resistance  $R_{\rm C}$  may significantly vary with the biasing current. The value of the series collector resistance may lower by one or two orders of magnitude if the collector junction becomes forward biased. A large series collector resistance may force the transistor into the saturation mode. Usually, when collector-emitter voltage is large enough, the effect of collector resistance is not significant. The SPICE model assumes constant value for the collector resistance  $R_{\rm C}$ .

The series base resistance  $R_B$  may significantly limit the transistor performance at high frequencies. Due to the current crowding effect and the base conductivity modulation, the series base resistance is a function of the collector current  $I_C$  [4]

$$R_{\rm B} = R_{\rm Bmin} + \frac{R_{\rm B0} - R_{\rm Bmin}}{0.5 + \sqrt{0.25 + \frac{i_{\rm C}}{I_{\rm KF}}}}$$

(1.25)

where

$I_{KF}$  is  $\beta_F$  high-current roll-off corner

$R_{\rm B0}$  is the base resistance at very small currents

$R_{\rm Bmin}$  is the minimum base resistance at high currents

FIGURE 1.6 Bipolar transistor equivalent diagrams. (a) SPICE model and (b) simplified model.

Another possible approximation of the base series resistance  $R_B$ , as a function of the base current  $I_B$ , is [4]

$$R_{\rm B} = 3(R_{\rm B0} - R_{\rm Bmin}) \frac{\tan z - z}{z \tan^2 z} + R_{\rm Bmin}, \quad z = \frac{\sqrt{1 + \frac{1.44I_{\rm B}}{\pi^2 I_{\rm RB}}} - 1}{\frac{24}{\pi^2} \sqrt{\frac{I_{\rm B}}{I_{\rm RB}}}}$$

(1.26)

where  $I_{RB}$  is the base current for which the base resistance falls halfway to its minimum value.

The base-emitter capacitance  $C_{\rm BE}$  is composed of two terms: the diffusion capacitance, which is proportional to the collector current, and the depletion capacitance, which is a function of the base-emitter voltage  $V_{\rm BE}$ . The  $C_{\rm BE}$  capacitance is given by

$$C_{\rm BE} = \tau_{\rm F} \frac{I_{\rm C}}{\eta_{\rm F} V_{\rm T}} + C_{\rm JE0} \left( 1 - \frac{\nu_{\rm BE}}{V_{\rm JE0}} \right)^{-m_{\rm JE}} \tag{1.27}$$

where

$V_{\rm JE0}$  is the base-emitter junction potential

$\tau_F$  is the base transit time for forward direction

$C_{\rm JE0}$  is the base-emitter zero-bias junction capacitance

$m_{\rm JE}$  is the base-emitter grading coefficient

The base-collector capacitance  $C_{\rm BC}$  is given by a similar expression as Equation 1.27. In the case when the transistor operates in forward-active mode, it can be simplified to

$$C_{\rm BC} = C_{\rm JC0} \left( 1 - \frac{\nu_{\rm BC}}{V_{\rm JC0}} \right)^{-m_{\rm JC}} \tag{1.28}$$

where

$V_{\rm JC0}$  is the base-collector junction potential

$C_{\rm JC0}$  is the base–collector zero-bias junction capacitance

m<sub>IC</sub> is the base-collector grading coefficient

In the case when the bipolar transistor is in the integrated form, the collector-substrate capacitance  $C_{CS}$  has to be considered

$$C_{\rm CS} = C_{\rm JS0} \left( 1 - \frac{V_{\rm CS}}{V_{\rm JS0}} \right)^{-m_{\rm JS}} \tag{1.29}$$

where

$V_{\rm ISO}$  is the collector-substrate junction potential

$C_{\rm ISO}$  the collector-substrate zero-bias junction capacitance

$m_{\rm IS}$  is the collector-substrate grading coefficient

When the transistor enters saturation, or it operates in the reverse-active mode, Equations 1.27 and 1.28 should be modified to

$$C_{\rm BE} = \tau_{\rm F} \frac{I_{\rm S} \exp\left(\frac{V_{\rm BE}}{\eta_{\rm F} V_{\rm T}}\right)}{\eta_{\rm F} V_{\rm T}} + C_{\rm JE0} \left(1 - \frac{V_{\rm BE}}{V_{\rm JE0}}\right)^{-m_{\rm JE}}$$

(1.30)

$$C_{\rm BC} = \tau_{\rm R} \frac{I_{\rm S} \exp\left(\frac{V_{\rm BC}}{\eta_{\rm R} V_{\rm T}}\right)}{\eta_{\rm R} V_{\rm T}} + C_{\rm JC0} \left(1 - \frac{V_{\rm BC}}{V_{\rm JC0}}\right)^{-m_{\rm JC}}$$

(1.31)

#### 1.1.6 Technologies

The bipolar technology was used to fabricate the first ICs more than 40 years ago. A similar standard bipolar process is still used. In recent years, for high-performance circuits and for BiCMOS technology, the standard bipolar process was modified by using the thick selective silicon oxidation instead of the p-type isolation diffusion. Also, the diffusion process was substituted by the ion implantation process, low-temperature epitaxy, and Chemical Vapor Deposition (CVD).

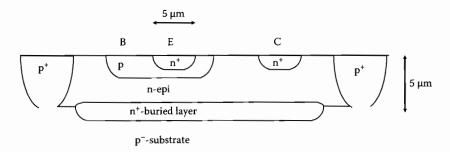

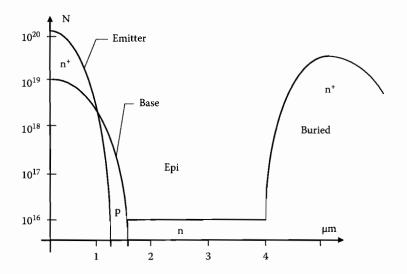

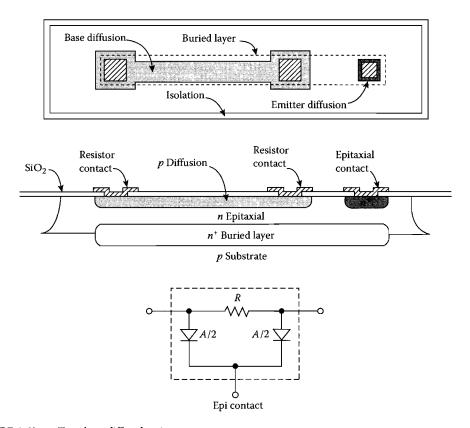

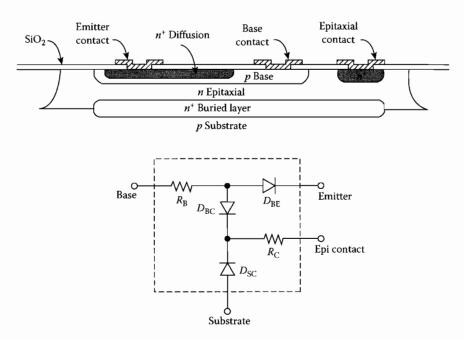

#### 1.1.6.1 Integrated NPN Bipolar Transistor

The structure of the typical integrated bipolar transistor is shown in Figure 1.7. The typical impurity profile of the bipolar transistor is shown in Figure 1.8. The emitter doping level is much higher than the base doping, so large current gains are possible (see Equation 1.19). The base is narrow and it has an impurity gradient, so the carrier transit time through the base is short (see Equation 1.17). Collector concentration near the base-collector junction is low, therefore, the transistor has a large breakdown voltage, large Early voltage  $V_{\rm AF}$ , and CB depletion capacitance is low. High impurity concentration in the buried layer leads to a small collector series resistance. The emitter strips have to be as narrow as technology allows, reducing the base series resistance and the current crowding effect. If large emitter area is required, many narrow emitter strips interlaced with base contacts have to be used in a single

FIGURE 1.7 NPN bipolar structure.

FIGURE 1.8 Cross section of a typical bipolar transistor.

transistor. Special attention has to be taken during the circuit design, so the base-collector junction is not forward biased. If the base-collector junction is forward biased, then the parasitic PNP transistors activate. This leads to undesired circuit operation. Thus, the integrated bipolar transistors must not operate in reverse or in saturation modes.

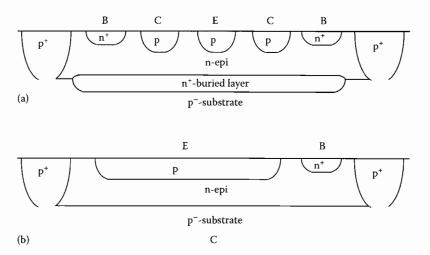

#### 1.1.6.2 Lateral and Vertical PNP Transistors

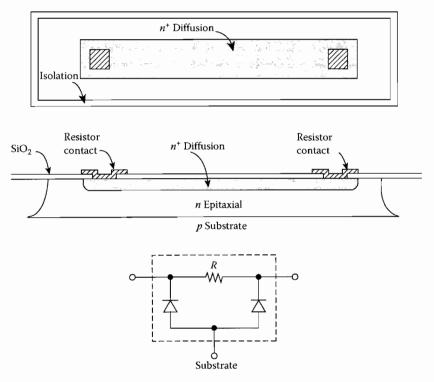

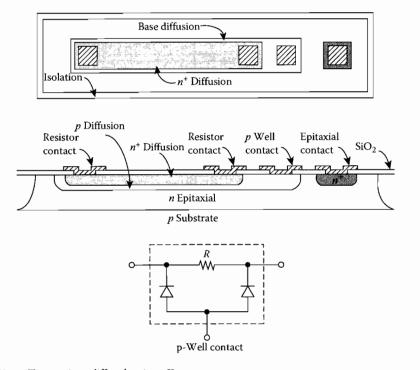

The standard bipolar technology is oriented for fabrication of the NPN transistors with the structure shown in Figure 1.7. Using the same process, other circuit elements, such as resistors and PNP transistors, can be fabricated as well.

The lateral transistor, shown in Figure 1.9a uses the base p-type layer for both emitter and collector fabrication. The vertical transistor, shown in Figure 1.9b uses the p-type base layer for emitter, and the p-type substrate as collector. This transistor is sometimes known as the substrate transistor. In both transistors the base is made of the n-type epitaxial layer. Such transistors with a uniform and thick base are slow. Also, the current gain  $\beta$  of such transistors is small. Note, that the vertical transistor has the collector shorted to the substrate as Figure 1.10b illustrates. When a PNP transistor with a large current gain is required, then the concept of the composite transistor can be implemented. Such a composite transistor, known also as superbeta transistor, consists a PNP lateral transistor, and the standard NPN transistor connected as shown in Figure 1.10c. The composed transistor acts as the PNP transistor and it has a current gain  $\beta$  approximately equal to  $\beta_{pnp}\beta_{npn}$ .

FIGURE 1.9 Integrated PNP transistors: (a) lateral PNP transistor, and (b) substrate PNP transistor.

FIGURE 1.10 Integrated PNP transistors: (a) lateral transistor, (b) substrate transistor, and (c) composed transistor.

#### 1.1.7 Model Parameters

It is essential to use proper transistor models in the computer aided design tools. The accuracy of simulation results depends on the model accuracy, and on the values of the model parameters used. In Section 1.1, the thermal and second-order effect in the transistor model are discussed. The SPICE bipolar transistor model parameters are discussed.

#### 1.1.7.1 Thermal Sensitivity

All parameters of the transistor model are temperature dependent. Some parameters are very strong functions of temperature. To simplify the model description, the temperature dependence of some parameters are often neglected. In this chapter, the temperature dependence of the transistor model is described based on the model of the SPICE program [3–5]. Deviations from the actual temperature dependence will also be discussed. The temperature dependence of junction capacitance is given by

$$C_{\rm J}(T) = C_{\rm J} \left\{ 1 + m_{\rm J} \left[ 4.010^{-4} (T - T_{\rm NOM}) + 1 - \frac{V_{\rm J}(T)}{V_{\rm J}} \right] \right\}$$

(1.32)

where  $T_{\text{NOM}}$  is the nominal temperature, which is specified in the SPICE program in the .OPTIONS statement. The junction potential  $V_{\text{I}}(T)$  is a function of temperature

$$V_{\rm J}(T) = V_{\rm J} \frac{T}{T_{\rm NOM}} - 3V_{\rm T} \ln \left(\frac{T}{T_{\rm NOM}}\right) - E_{\rm G}(T) + E_{\rm G} \frac{T}{T_{\rm NOM}}$$

(1.33)

The value of 3 in the multiplication coefficient of above equation is from the temperature dependence of the effective state densities in the valence and conduction bands. The temperature dependence of the energy gap is computed in the SPICE program from

$$E_{\rm G}(T) = E_{\rm G} - \frac{7.0210^{-4}T^2}{T + 1108} \tag{1.34}$$

The transistor saturation current as a function of temperature is calculated as

$$I_{s}(T) = I_{s} \left(\frac{T}{T_{\text{NOM}}}\right)^{X_{\text{TI}}} \exp\left[\frac{E_{G}(T - T_{\text{NOM}})}{V_{T}T_{\text{NOM}}}\right]$$

(1.35)

where  $E_G$  is the energy gap at the nominal temperature. The junction leakage currents  $I_{SE}$  and  $I_{SC}$  are calculated using

$$I_{SE}(T) = I_{SE} \left(\frac{T}{T_{\text{NOM}}}\right)^{X_{\text{TI}} - X_{\text{TB}}} \exp\left[\frac{E_{G}(T - T_{\text{NOM}})}{\eta_{E} V_{\text{T}} T_{\text{NOM}}}\right]$$

(1.36)

and

$$I_{SC}(T) = I_{SC} \left(\frac{T}{T_{NOM}}\right)^{X_{TI} - X_{TB}} \exp\left[\frac{E_G(T - T_{NOM})}{\eta_C V_T T_{NOM}}\right]$$

(1.37)

The temperature dependence of the transistor current gains  $\beta_F$  and  $\beta_R$  are modeled in the SPICE as

$$\beta_{\rm F}(T) = \beta_{\rm F} \left(\frac{T}{T_{\rm NOM}}\right)^{X_{\rm TB}}, \quad \beta_{\rm R}(T) = \beta_{\rm R} \left(\frac{T}{T_{\rm NOM}}\right)^{X_{\rm TB}}$$

(1.38)

The SPICE model does not give accurate results for the temperature relationship of the current gain  $\beta$  at high currents. For high current levels the current gain decreases sharply with the temperature, as can be seen from Figure 1.3. Also, the knee current parameters IKF, IKR, IKB are temperature-dependent, and this is not implemented in the SPICE program.

#### 1.1.7.2 Second-Order Effects

The current gain  $\beta$  is sometimes modeled indirectly by using different equations for the collector and base currents [4,5]

$$I_{\rm C} = \frac{I_{\rm S}(T)}{Q_{\rm b}} \left( \exp \frac{V_{\rm BE}}{\eta_{\rm F} V_{\rm T}} - \exp \frac{V_{\rm BC}}{\eta_{\rm R} V_{\rm T}} \right) - \frac{I_{\rm S}(T)}{\beta_{\rm R}(T)} \left( \exp \frac{V_{\rm BC}}{\eta_{\rm R} V_{\rm T}} - 1 \right) - I_{\rm SC}(T) \left( \exp \frac{V_{\rm BC}}{\eta_{\rm C} V_{\rm T}} - 1 \right)$$

(1.39)

where

$$Q_{\rm b} = \frac{1 + \sqrt{1 + 4Q_{\rm X}}}{2\left(1 - \frac{V_{\rm BC}}{V_{\rm AF}} - \frac{V_{\rm BE}}{V_{\rm AR}}\right)}$$

(1.40)

$$Q_{\rm X} = \frac{I_{\rm s}(T)}{I_{\rm KF}} \left( \exp \frac{V_{\rm BE}}{\eta_{\rm F} V_{\rm T}} - 1 \right) + \frac{I_{\rm s}(T)}{I_{\rm KR}} \left( \exp \frac{V_{\rm BC}}{\eta_{\rm R} V_{\rm T}} - 1 \right) \tag{1.41}$$

and

$$I_{\rm B} = \frac{I_{\rm S}}{\beta_{\rm F}} \left( \exp \frac{V_{\rm BE}}{\eta_{\rm F} V_{\rm T}} - 1 \right) + I_{\rm SE} \left( \exp \frac{V_{\rm BE}}{\eta_{\rm E} V_{\rm T}} - 1 \right) + \frac{I_{\rm S}}{\beta_{\rm R}} \left( \exp \frac{V_{\rm BC}}{\eta_{\rm R} V_{\rm T}} - 1 \right) + I_{\rm SC} \left( \exp \frac{V_{\rm BC}}{\eta_{\rm C} V_{\rm T}} - 1 \right)$$

(1.42)

where

I<sub>SE</sub> is the base-emitter junction leakage current

I<sub>SC</sub> is the base–collector junction leakage current

$\eta_E$  is the base–emitter junction leakage emission coefficient

$\eta_C$  is the base-collector junction leakage emission coefficient

The forward transit time  $\tau_F$  is a function of biasing conditions. In the SPICE program the  $\tau_F$  parameter is computed using

$$\tau_{\rm F} = \tau_{\rm F0} \left[ 1 + X_{\rm TF} \left( \frac{I_{\rm CC}}{I_{\rm CC} + I_{\rm TF}} \right)^2 \exp \frac{V_{\rm BC}}{1.44 V_{\rm TF}} \right], \quad I_{\rm CC} = I_{\rm s} \left( \exp \frac{V_{\rm BE}}{\eta_{\rm F} V_{\rm T}} - 1 \right)$$

(1.43)

At high frequencies the phase of the collector current shifts. This phase shift is computed in the SPICE program following way

$$I_{\rm C}(\omega) = I_{\rm C} \exp(j\omega P_{\rm TF} \tau_{\rm F}) \tag{1.44}$$

where  $P_{\rm TF}$  is a coefficient for excess phase calculation.

Noise is usually modeled as the thermal noise for parasitic series resistances, and as shot and flicker noise for collector and base currents

$$\overline{i_{\rm B}^2} = \frac{4kT\Delta f}{R} \tag{1.45}$$

$$\overline{I_{\rm B}^2} = \left(2qI_{\rm B} + \frac{K_{\rm F}I_{\rm B}^{A_{\rm F}}}{F}\right)\Delta f \tag{1.46}$$

$$\overline{i_{\rm C}^2} = 2qI_{\rm C}\Delta f \tag{1.47}$$

where  $K_{\rm F}$  and  $A_{\rm F}$  are the flicker-noise coefficient and flicker-noise exponent. More detailed information about noise modeling is given in Section 3.2.

#### 1.1.7.3 SPICE Model of the Bipolar Transistor

The SPICE model of bipolar transistor uses similar or identical equations as described in this chapter [3–5]. Table 1.1 shows the parameters of the bipolar transistor model and its relation to the parameters used in this chapter.

TABLE 1.1 Parameters of SPICE Bipolar Transistor Model

| Name Used            | Equations                                    | SPICE Name | Parameter Description                             | Unit     | Typical<br>Value | SPICE<br>Default |

|----------------------|----------------------------------------------|------------|---------------------------------------------------|----------|------------------|------------------|

|                      | 1.10, 1.11                                   | IS         | Saturation current                                | A        | 1015             | 10-16            |

| $I_{SE}$             | 1.39                                         | ISE        | B-E leakage saturation current                    | A        | 10-12            | 0                |

| $I_{SC}$             | 1.39                                         | 1CS        | B-C leakage saturation current                    | A        | $10^{-12}$       | 0                |

| $\beta_{\mathrm{F}}$ | 1.14, 1.16, 1.21                             | BF         | Forward current gain                              | _        | 100              | 100              |

| $\beta_R$            | 1.14, 1.16, 1.21                             | BF         | Reverse current gain                              | _        | 0.1              | 1                |

| $\eta_{\rm F}$       | 1.15, 1.24, 1.30, 1.31,<br>1.39 through 1.41 | NF         | Forward current emission coefficient              | _        | 1.2              | 1.0              |

| $\eta_R$             | 1.15, 1.24, 1.30, 1.31,<br>1.39 through 1.42 | NR         | Reverse current emission coefficient              | -        | 1.3              | 1.0              |

| $\eta_E$             | 1.39                                         | NE         | B-E leakage emission coefficient                  | _        | 1.4              | 1.5              |

| $\eta_{\rm C}$       | 1.39                                         | NC         | B-C leakage emission coefficient                  | _        | 1.4              | 1.5              |

| $V_{ m AF}$          | 1.21, 1.40                                   | VAF        | Forward Early voltage                             | V        | 200              | $\infty$         |

| $V_{ m AR}$          | 1.21, 1.40                                   | VAR        | Reverse Early voltage                             | V        | 50               | $\infty$         |

| $I_{ m KF}$          | 1.22, 1.23, 1.40                             | 1KF        | $\beta_{\mathrm{F}}$ high-current roll-off corner | A        | 0.05             | $\infty$         |

| $I_{\rm KR}$         | 1.22, 1.23, 1.40                             | IKR        | $\beta_R$ high-current roll-off corner            | A        | 0.01             | $\infty$         |

| $I_{\mathrm{RB}}$    | 1.26                                         | 1RB        | Current where base resistance falls by half       | A        | 0.1              | $\infty$         |

| $R_{ m B}$           | 1.25, 1.26                                   | RB         | Zero base resistance                              | $\Omega$ | 100              | 0                |

| $R_{Bmin}$           | 1.25, 1.26                                   | RBM        | Minimum base resistance                           | $\Omega$ | 10               | RB               |

| $R_{\rm E}$          | Figure 1.6                                   | RE         | Emitter series resistance                         | Ω        | 1                | 0                |

| $R_{\rm C}$          | Figure 1.6                                   | RC         | Collector series resistance                       | Ω        | 50               | 0                |

| $C_{\rm JE0}$        | 1.27                                         | CJE        | B–E zero-bias depletion capacitance               | F        | $10^{-12}$       | 0                |

| $C_{\rm JC0}$        | 1.28                                         | CJC        | B-C zero-bias depletion capacitance               | F        | $10^{-12}$       | 0                |

| $C_{\rm JS0}$        | 1.29                                         | CJS        | Zero-bias collector-substrate capacitance         | F        | $10^{-12}$       | 0                |

| $V_{ m JE0}$         | 1.27                                         | VJE        | B-E built-in potential                            | V        | 0.8              | 0.75             |

| $V_{\rm JC0}$        | 1.28                                         | VJC        | B-C built-in potential                            | V        | 0.7              | 0.75             |

| $V_{ m JS0}$         | 1.29                                         | VJS        | Substrate junction built-in potential             | V        | 0.7              | 0.75             |

| $m_{ m JE}$          | 1.27                                         | MJE        | B-E junction exponential factor                   | _        | 0.33             | 0.33             |

| $m_{ m IC}$          | 1.28                                         | MJC        | B-C junction exponential factor                   | _        | 0.5              | 0.33             |

(continued)

TABLE 1.1 (continued) Parameters of SPICE Bipolar Transistor Model

| Name Used         | Equations              | SPICE Name | Parameter Description                                                              | Unit | Typical<br>Value | SPICE<br>Default |

|-------------------|------------------------|------------|------------------------------------------------------------------------------------|------|------------------|------------------|

| $m_{ m JS}$       | 1.29                   | MJS        | Substrate junction exponential factor                                              | _    | 0.5              | 0                |

| $X_{\rm CJC}$     | Figure 1.6             | XCJC       | Fraction of B–C capacitance<br>connected to internal base node<br>(see Figure 1.6) | _    | 0.5              | 0                |

| $	au_{	extsf{F}}$ | 1.17, 1.28, 1.30, 1.42 | TF         | Ideal forward transit time                                                         | s    | $10^{-10}$       | 0                |

| $\tau_{R}$        | 1.31                   | TR         | Reverse transit time                                                               | s    | $10^{-8}$        | 0                |

| $X_{\mathrm{TF}}$ | 1.43                   | XTF        | Coefficient for bias dependence of $\tau_{\text{F}}$                               | _    |                  | 0                |

| $V_{\mathrm{TF}}$ | 1.43                   | VTF        | Voltage for $	au_{	ext{F}}$ dependence on $V_{	ext{BC}}$                           | V    |                  | $\infty$         |

| $I_{\mathrm{TF}}$ | 1.43                   | ITF        | Current where $\tau_F = f(I_C, V_{BC})$ starts                                     | A    |                  | 0                |

| $P_{\mathrm{TF}}$ | 1.44                   | PTF        | Excess phase at freq = $1/(2\pi\tau_F)$<br>Hz                                      | 0    |                  | 0                |

| $X_{\mathrm{TB}}$ | 1.38                   | XTB        | Forward and reverse beta temperature exponent                                      |      |                  | 0                |

| $E_{\mathrm{G}}$  | 1.34                   | EG         | Energy gap                                                                         | eV   | 1.1              | 1.11             |

| $X_{TI}$          | 1.35 through 1.37      | XTI        | Temperature exponent for effect on $I_s$                                           | _    | 3.5              | 3                |

| $K_{F}$           | 1.46                   | KF         | Flicker-noise coefficient                                                          | _    |                  | 0                |

| $A_{F}$           | 1.46                   | AF         | Flicker-noise exponent                                                             | _    |                  | 1                |

| $F_{\rm C}$       |                        | FC         | Coefficient for the forward<br>biased depletion capacitance<br>formula             | _    | 0.5              | 0.5              |

| $T_{\text{NOM}}$  | 1.32 through 1.38      | TNOM       | Nominal temperature specified in .OPTION statement                                 | K    | 300              | 300              |

The SPICE [3] was developed mainly for analysis of ICs. During the analysis it is assumed that the temperatures of all circuit elements are the same. This is not true for power ICs where the junction temperatures may differ by 30 K or more. This is obviously not true for circuits composed of the discrete elements where the junction temperatures may differ by 100 K and more. These temperature effects, which can significantly affect the analysis results, are not implemented in the SPICE program.

Although the SPICE bipolar transistor model uses more than 40 parameters, many features of the bipolar transistor are not included in the model. For example, the reverse junction characteristics are described by Equation 1.32. This model does not give accurate results. In the real silicon junction the leakage current is proportional to the thickness of the depletion layer, which is proportional to  $V^{1/m}$ . Also the SPICE model of the bipolar transistor assumes that there is no junction breakdown voltage. A more accurate model of the reverse junction characteristics is described in Section 11.5 of Fundamentals of Circuits and Filters. The reverse transit time  $\tau_R$  is very important to model the switching property of the lumped bipolar transistor, and it is a strong function of the biasing condition and temperature. Both phenomena are not implemented in the SPICE model.

#### 1.1.8 SiGe HBTs

The performance of the Si bipolar transistor can be greatly enhanced with proper engineering of the base bandgap profile using a narrower bandgap material, SiGe, an alloy of Si and Ge. Structure wise, a SiGe

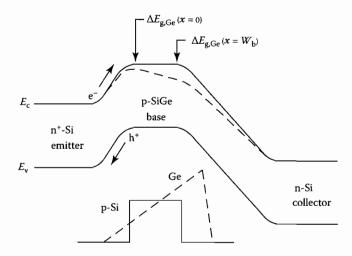

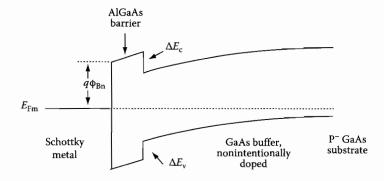

FIGURE 1.11 Energy band diagram of a graded base SiGe HBT and a comparably constructed Si BJT.

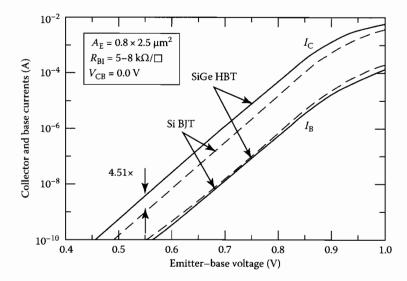

FIGURE 1.12 Experimental collector and base currents versus EB voltage for SiGe HBT and Si BJT.

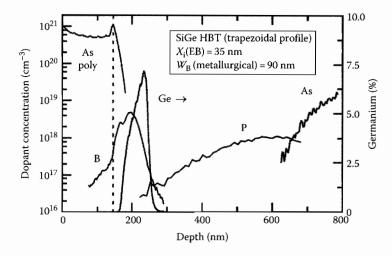

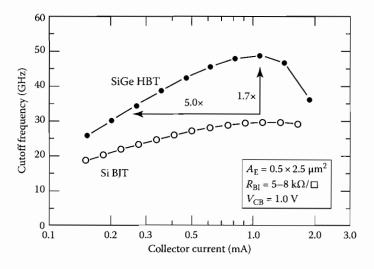

HBT is essentially a Si BJT with a SiGe base. Its operation and circuit level performance advantages can be illustrated with the energy band diagram in Figure 1.11 [13]. Here the Ge content is linearly graded from emitter toward collector to create a large accelerating electric field that speeds up minority carrier transport across the base, thus making transistor speed much faster and cutoff frequency much higher. Everything else being the same, the potential barrier for electron injection into the base is reduced, thus exponentially enhancing the collector current. The base current is the same for SiGe HBT and Si BJT, as the emitter is typically made the same. Beta is thus higher in SiGe HBT. Figure 1.12 confirms these expectations experimentally with data from a typical first-generation SiGe HBT technology. The measured doping and Ge profiles are shown in Figure 1.13. The metallurgical base width is only 90 nm, and the neutral base width is around 50 nm. Figure 1.14 shows experimental cutoff frequency  $f_{\rm T}$  improvement from using a graded SiGe base, which also directly translates into maximum oscillation frequency  $f_{\rm max}$  improvement.

FIGURE 1.13 Measured doping and Ge profiles of a modern SiGe HBT.

FIGURE 1.14 Experimental cutoff frequency versus collector current for SiGe HBT and Si BJT.

#### 1.1.8.1 Operation Principle and Performance Advantages over Si BJT

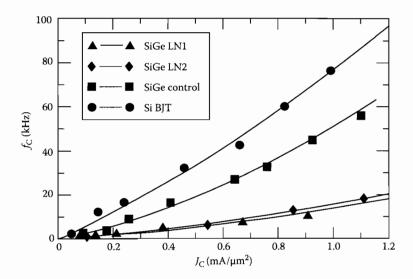

In modern transistors, particularly with the use of polysilicon emitter, beta may be sufficient. If so, the higher beta potential of SiGe HBT can then be traded for reduced base resistance, through the use of higher base doping. The unique ability of simultaneously achieving high beta, low base resistance, and high cutoff frequency makes SiGe HBT attractive for many RF circuits. Broadband noise is naturally reduced, as low base resistance reduces transistor input noise voltage, and high beta as well as high  $f_{\rm T}$  reduces transistor input noise current [13]. Experimentally, 1/f noise at the same base current was found to be approximately the same for SiGe HBT and Si BJT [14]. Consequently, 1/f noise is often naturally reduced in SiGe HBT circuits for the same biasing collector current, as base current is often smaller due to higher beta, as shown in Figure 1.15 using corner frequency as a figure-of-merit.

These, together with circuit-level optimization, can lead to excellent low-phase noise oscillators and frequency synthesizers suitable for both wireless and wire line communication circuits. Another less

**FIGURE 1.15** Experimentally measured corner frequency as a function of collector current density for three SiGe HBTs with different base SiGe designs, and a comparatively constructed Si BJT.

obvious advantage from grading Ge is the collector side of the neutral base has less impact on the collector current than the emitter side of the neutral base. Consequently, as collector voltage varies and the collector side of the neutral base is shifted toward the emitter due to increased CB junction depletion layer thickness, the collector current is increased to a much lesser extent than in a comparably constructed Si BJT, leading to a much higher output impedance or Early voltage. The  $\beta \times V_A$  product is thus much higher in SiGe HBT than in Si BJT.

#### 1.1.8.2 Industry Practice and Fabrication Technology

The standard industry practice today is to integrate SiGe HBT with CMOS, to form a SiGe BiCMOS technology. The ability to integrate with CMOS is also a significant advantage of SiGe HBT over III–V HBT. Modern SiGe BiCMOS combines the analog and RF performance advantages of the SiGe HBT, and the lower power logic, high integration level, and memory density of Si CMOS, into a single cost-effective system-on-chip (SoC) solution. Typically, SiGe HBTs with multiple breakdown voltages are offered through selective collector implantation, to provide more flexibility in circuit design.

The fabrication process of SiGe HBT and its integration with CMOS has been constantly evolving in the past two decades, and varies from company to company. Below are some common fabrication elements and modules shared by many if not all commercial first-generation (also most wide spread in manufacturing at present) SiGe technologies:

- 1. A starting  $N^+$  subcollector around 5  $\Omega/sq$  on a p-type substrate at  $5\times 10^{15}/cm^3$ , typically patterned to allow CMOS integration.

- 2. A high-temperature, lightly doped n-type collector, around 0.4–0.6  $\mu$ m thick at 5 × 10<sup>15</sup>/cm<sup>3</sup>.

- 3. Polysilicon-filled deep trenches for isolation from adjacent devices, typically 1  $\mu m$  wide and 7–10  $\mu m$  deep.

- 4. Oxide filled shallow trenches or LOCOS for local device isolation, typically 0.3-0.6 μm deep.

- 5. An implanted collector reach through to the subcollector, typically at 10-20  $\Omega \mu m^2$ .

- 6. A composite SiGe epi layer consisting of a 10–20 nm Si buffer, a 70–100 nm boron-doped SiGe active layer, with or without C doping to help suppress boron out diffusion, and a 10–30 nm Si cap. The integrated boron dose is typically  $1-3 \times 10^{13}/\text{cm}^2$ .

FIGURE 1.16 Structure of a modern SiGe HBT.

- 7. A variety of EB self-alignment scheme, depending on device structure and SiGe growth approach. All of them utilize some sort of spacer that is 100–300 nm wide.

- 8. Multiple self-aligned collector implantation to allow multiple breakdown voltages on the same chip.

- 9. Polysilicon extrinsic base, usually formed during SiGe growth over shallow trench oxide, and additional self-aligned extrinsic implantation to lower base resistance.

- 10. A silicided extrinsic base.

- 11. A 100–200 nm thick heavily doped ( $>5 \times 10^{20}/\text{cm}^3$ ) polysilicon emitter, either implanted or in situ doped.

- 12. A variety of multiple level back-end-of-line metallization schemes using Al or Cu, typically borrowed from parent CMOS process.

These technological elements can also be seen in the electronic image of a second-generation SiGe HBT shown in Figure 1.16.

#### References

- 1. J. J. Ebers and J. M. Moll, Large signal behavior of bipolar transistors. *Proceedings IRE* 42, 1761–1772, December 1954.

- H. K. Gummel and H. C. Poon, An integral charge-control model of bipolar transistors. Bell System Technical Journal 49, 827–852, May 1970.

- 3. L. W. Nagel and D. O. Pederson, SPICE (Simulation Program with Integrated Circuit Emphasis). University of California, Berkeley, ERL Memo No. ERL M382, April 1973.

- 4. P. Antognetti and G. Massobrio, Semiconductor Device Modeling with SPICE, McGraw-Hill, New York, 1988.

- 5. A. Vadimiresku, The SPICE Book, John Wiley & Sons, Hoboken, NJ, 1994.

- 6. A. S. Grove, Physics and Technology of Semiconductor Devices, John Wiley & Sons, Hoboken, NJ, 1967.

- 7. S. M. Sze, Physics of Semiconductor Devices, 2nd ed., John Wiley & Sons, Hoboken, NJ, 1981.

- 8. G. W. Neudeck, *The PN Junction Diode*, Vol II, Modular Series on Solid-State Devices, Addison-Wesley, Upper Saddle River, NJ, 1983.

- R. S. Muller and T. I. Kamins, Device Electronics for Integrated Circuits, 2nd ed., John Wiley & Sons, Hoboken, NJ, 1986.

- 10. E. S. Yang, Microelectronic Devices, McGraw-Hill, New York, 1988.

- 11. B. G. Streetman, Solid State Electronic Devices. 3rd ed., Prentice Hall, Upper Saddle River, NJ, 1990.

- 12. D. A. Neamen, Semiconductor Physics and Devices, Irwin, 1992.

- 13. J. D. Cressler and G. Niu, Silicon-Germanium Heterojunction Bipolar Transistor, Artech House, Norwood, MA, 2003.

- 14. G. Niu, Noise in SiGe HBT RF technology: Physics, modeling and circuit implications, *Proceedings of the IEEE*, pp. 1583–1597, September 2005.

#### 1.2 Metal-Oxide-Silicon Field Effect Transistor

John Choma, Jr.

#### 1.2.1 Introduction

Integrated electronic circuits realized in metal-oxide-silicon field effect transistor (MOSFET) technology are ubiquitous in both the commercial and military sectors of the technical community. To be sure, transistors manufactured in certain bipolar and III-V compound transistor technologies compete successfully with their MOSFET counterparts from such performance perspectives as switching speed, wideband frequency response, and insensitivity to electromagnetic interference and irradiated environments. Nevertheless, the MOSFET reigns supreme in the extant state of the electronics art for several reasons. The first of these reasons derives from the fact that the cross-section geometry of a MOSFET, when compared to that of most other solid-state transistors, is simpler. This simplicity affords a relative ease of foundry processing, which in turn promotes high device yield and therefore, cost-effective manufacturing. A second reason is that the surface area consumed on chip, or footprint, of a MOSFET is generally smaller than that of a comparably performing bipolar or III-V compound transistors. This feature allows increased packing density, which is particularly advantageous for digital signal processors that commonly require upwards of millions of transistors for system functionality. Third, MOSFETs can deliver acceptable circuit performance at low standby power levels, which is a laudable attribute in light of the aforementioned high device density digital architectures and the portability culture in which society is immersed presently. Finally, the native insulating oxide indigenous to the monolithic processing of silicon semiconductors renders MOSFET technologies amenable to the implementation of complex electronic systems on a single chip. No such native oxide prevails in III-V compound technologies, thereby rendering awkward the electrical isolation among the various components, subsystems, and subcircuits that comprise the overall electronic system.

The penchant toward adopting MOSFET technology for analog signal processing applications can also be rationalized. In particular, the nature of modern integrated systems is rarely exclusively digital or exclusively analog. Such systems are, in fact, "mixed signal" architectures that embody both digital and analog signal processing on the same chip. Because of the simplicity, packing density, and power dissipation attributes of MOSFETs, virtually 100% of digital architectures are realized in MOSFET technology. Prudence alone accordingly dictates a MOSFET technology realization of the analog cells implicit to a mixed signal framework if only to facilitate the electrical interface between the analog and digital units.

Aside from the operating flexibility and programmability advantages boasted by digital circuit schema, digital circuits in mixed signal architectures are often required to assure and sustain performance optimality of the analog signal flow paths in an electronic system. Unlike most digital networks, high-performance analog circuits are sensitive to specific values, or at least specific ranges of values, of several of the key physical and electrical parameters that effectively define the electrical properties of MOSFETs. Unfortunately, attaining the requisite accuracy in the numerical delineation of these parameters becomes

progressively more daunting as the performance metrics imposed on an analog network become more challenging and as device geometries scale to meet omnipresent quests for wider signal processing passbands. In these high-performance systems, digital subsystems are often deployed to sense the observable performance metrics of an analog signal flow path, compare said metrics to their respective optimal design goals, and then appropriately adjust the relevant electrical parameters or signal excitations implicit to the signal path. In effect, the combined digital controller and analog network behave as a seamless adaptive system that automatically corrects for manufacturing vagaries, increased device operating temperatures, and certain environmental effects.

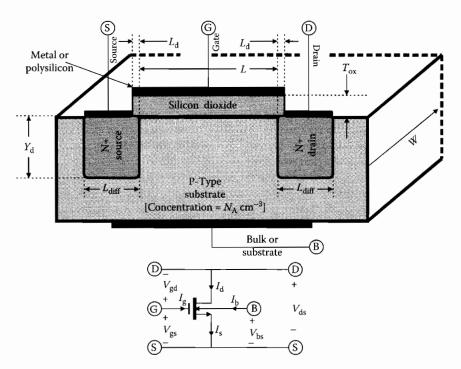

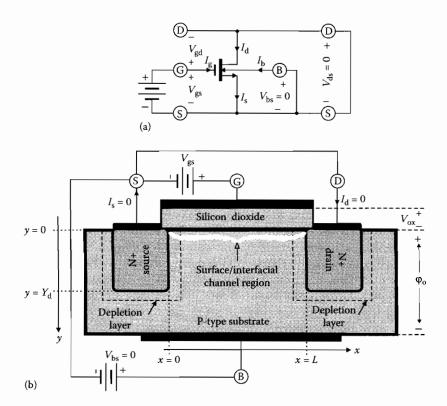

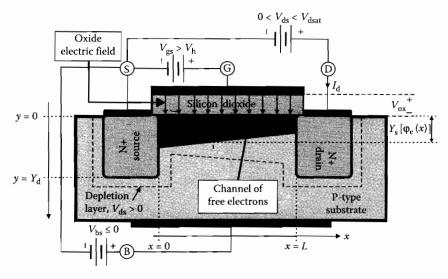

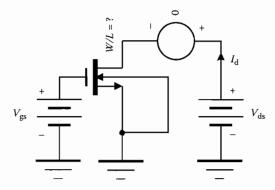

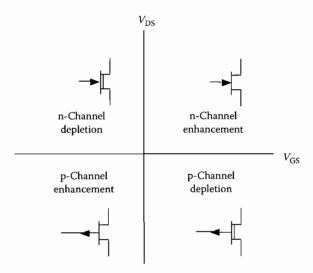

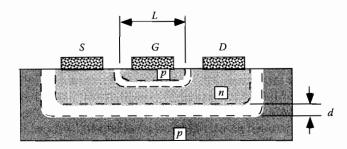

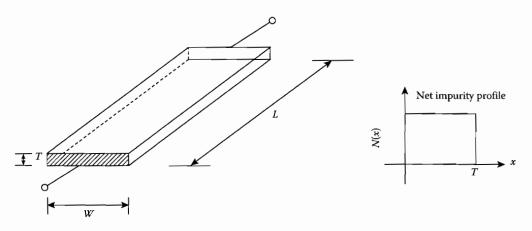

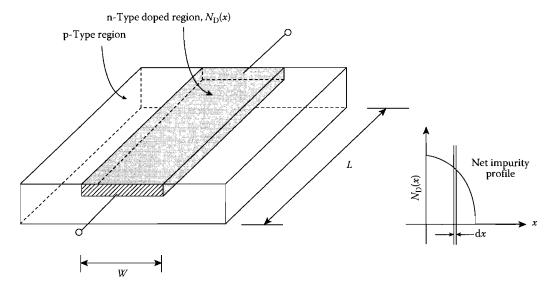

The most commonly utilized MOSFETs in modern electronic systems come in two flavors: the N-channel MOSFET (NMOS), diagrammed in Figure 1.17 and the P-channel MOSFET (PMOS) shown in Figure 1.18. In the NMOS device of Figure 1.17, the bulk substrate is P-type and is doped to an average acceptor impurity concentration of  $N_A$ , for which a representative range of values is  $5(10^{14})$ atoms/cm<sup>3</sup>  $< N_A < 10^{16}$  atoms/cm<sup>3</sup>. Its vertical depth, which is not expressly highlighted in the figure, is many times larger than the depth,  $Y_d$ , (of the order of a few tenths of microns) of either the source or drain diffusions or implants. These regions, whose widths are indicated as Ldiff and which are connected electrically to the source (S) and drain (D) terminals of the MOSFET, are very strongly doped in that their donor impurity concentrations are  $N_{\rm D} = 10^{20}$  atoms/cm<sup>3</sup> or larger. The width,  $L_{\rm diff}$  is typically twoor three-times the channel length, indicated as L in the diagram. The metallization contact that forms the electrical terminal of the semiconductor bulk (B) is generally connected to the most negative potential available in the circuit into which the subject transistor is embedded. Such a connection reverse biases the PN junctions formed between the bulk and source regions and between the bulk and drain regions. This reverse biasing ensures that for at least low signal frequencies, the source and drain regions are electrically isolated from each other and from the bulk substrate. In certain types of multiwell IC processes, bulksource and bulk-drain reverse biasing is assured simply by returning the bulk terminal directly to the source region contact.

FIGURE 1.17 A simplified three-dimensional depiction of an N-channel MOSFET (NMOS) and its corresponding electrical schematic symbol. The diagram is not drawn to scale.

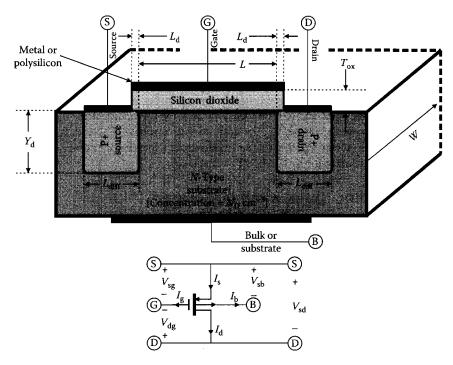

**FIGURE 1.18** A simplified three-dimensional depiction of an P-channel MOSFET (PMOS) and its corresponding electrical schematic symbol. The diagram is not drawn to scale.

Lying atop the P-type bulk substrate is an insulating silicon dioxide layer of thickness  $T_{\rm ox}$  that extends into the page as shown by a gate width, W. The oxide thickness in the extant state of the art is of the order of several tens of angstroms, where  $1~{\rm \AA}$  is  $10^{-8}$  cm. This oxide layer entirely covers the channel length, L, that separates the source region from the drain region, and it may overlap the source and drain regions by the amount,  $L_{\rm d}$ , indicated in the diagram. The overlap of the source and drain regions is undesirable in that it limits broadband frequency responses in certain types of MOSFET amplifiers. In processes boasting self-aligned gate capabilities,  $L_{\rm d}$  is ideally reduced to zero. But for state of the art processes delivering channel lengths as small as 65–130 nM, gate self-alignment focused on reducing  $L_{\rm d}$  to no more than 5% of L is a challenging undertaking. The gate width, W, can be no smaller than the minimum channel length that can be produced by the identified foundry process. Subject to this proviso, the gate aspect ratio, W/L, is a designable parameter selected in accordance with the operating requirements of the circuit application for which the considered MOSFET is utilized.

The gate terminal (G) is formed by a contact made of a metallic or a polycrystalline silicon layer deposited directly atop the gate oxide. The gate metal of choice is aluminum. If the MOSFET under consideration is used in high-temperature environments and/or in applications that exploit low power supply voltages, polycrystalline silicon, which is commonly referred to as polysilicon, supplants the aluminum gate.

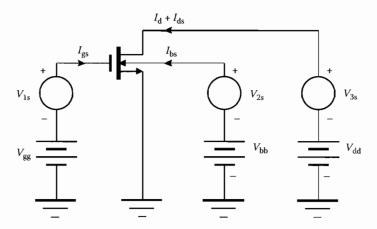

In addition to the simplified cross-section diagram of the N-channel MOSFET, Figure 1.17 inserts the electrical schematic symbol of the NMOS transistor. Of particular interest are the positive reference conventions adopted for four device currents and four device voltages. Specifically, positive drain current,  $I_{\rm d}$ , flows into the transistor, as do the gate current,  $I_{\rm g}$ , and the bulk, or substrate, current,  $I_{\rm b}$ , while positive source current,  $I_{\rm s}$ , flows out of the transistor. It follows from Kirchhoff's current law that

$$I_{\rm s} = I_{\rm d} + I_{\rm g} + I_{\rm b}.$$

(1.48)

However, since the gate contact is isolated from the semiconductor bulk by an insulating oxide layer,  $I_{\rm g}$  is zero at the low frequencies for which capacitive phenomena associated with the insulating gate dielectric are insignificant. Moreover, the bulk current,  $I_{\rm b}$ , is likewise almost zero at low signal frequencies, provided, as is usually the case, that care is taken to ensure reverse biasing of the bulk–drain and bulk–source PN junctions. Accordingly, the source and drain currents,  $I_{\rm s}$  and  $I_{\rm d}$ , respectively, are essentially identical when the frequencies of signals applied to the MOSFET are low. The pages that follow demonstrate that the static and low-frequency value of the drain, and hence the source, current is controlled by the gate-to-source voltage,  $V_{\rm gs}$ , the drain-to-source voltage,  $V_{\rm ds}$ , and, to a somewhat lesser extent, the bulk-to-source voltage  $V_{\rm bs}$ . Stipulating an additional dependence of drain current on gate-to-drain voltage  $V_{\rm gd}$  is superfluous, for by Kirchhoff's voltage law,

$$V_{\rm ds} = V_{\rm gs} - V_{\rm gd}. ag{1.49}$$

The P-channel MOSFET abstracted in Figure 1.18 is architecturally identical to its N-channel counterpart. The notable differences are that the bulk substrate in PMOS is N-type and the source and drain regions are heavily doped with P-type impurities. It follows that electrical isolation between the source region and the bulk, as well as between the drain region and the bulk, requires that the bulk substrate terminal of a PMOS device be connected either to the most positive of available circuit potentials or, if the process allows, to the source terminal. All of the geometrical parameters and their representative values remain the same as stipulated in conjunction with the NMOS unit. The PMOS electrical schematic symbol, which is also shown in the figure at hand, differs from the NMOS symbol in that the directions of the source terminal and bulk terminal arrows are reversed, as are the positive reference directions of all four transistor currents. While Equation 1.48 remains applicable, the analytical expression for the drain current,  $I_{\rm d}$ , which now flows out of the transistor, is more conveniently couched in terms of the source-to-gate voltage,  $V_{\rm sg}$ , the source-to-drain voltage,  $V_{\rm sd}$ , and the source-to-bulk voltage,  $V_{\rm sb}$ . The drain-to-gate voltage,  $V_{\rm dg}$ , derives from

$$V_{\rm sd} = V_{\rm sg} - V_{\rm dg}, \tag{1.50}$$

which mirrors Equation 1.49 subsequent to multiplying both sides of this equation by -1.

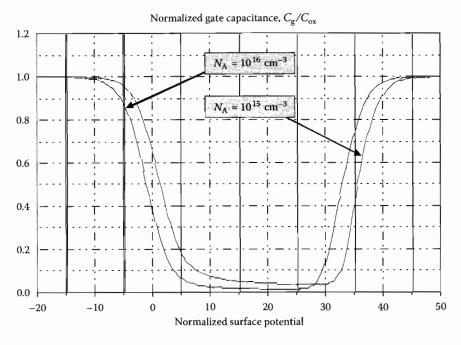

## 1.2.2 Channel Charge

A fundamental understanding of the physical charge storage and charge transport mechanisms that underpin the observable volt–ampere characteristics of considered transistors facilitates the reliable and reproducible design of high-performance analog networks in MOSFET technology. Aside from establishing a foundation upon which the static characteristic curves of a MOSFET can be constructed in a physically sound framework, these charge profiles also serve to define the voltage-dependent nature of the capacitance characteristics of a MOSFET. In effect, the subject charge profiles posture the MOSFET as a plausible varactor, which is useful in the monolithic design of voltage controlled oscillators, active filters, and other electronic networks.

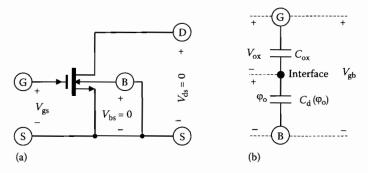

The profile of charge stored in the channel between the source and drain regions of a MOSFET is best examined in terms of the simple circuit given in Figure 1.19a. In this circuit, the drain terminal is short circuited to the source to pin the drain-source voltage,  $V_{\rm ds}$ , to zero. A zero bias is applied as indicated between the bulk and source, thereby establishing a charge depletion region about the PN junction formed between the substrate and source regions. Since the source and the drain are electrically connected to one another, the zero bias applied between bulk and source establishes an identical depletion zone about the bulk-drain PN junction. These depletion layers are delineated in the companion cross-section diagram of Figure 1.19b, as are the surface potential,  $\varphi_0$ , and the potential,  $V_{\rm ox}$ , dropped across the gate silicon dioxide layer. With  $V_{\rm ds}=0$ , Equation 1.49 ensures a gate-source voltage,  $V_{\rm gs}$ , that

1-25

**FIGURE 1.19** (a) NMOS transistor operated with  $V_{\rm ds}=0$  and  $V_{\rm bs}=0$ . Although the battery connected between the gate and the source ensures  $V_{\rm gs}>0$ ,  $V_{\rm gs}\le0$  is allowed in the discussion that references this circuit. (b) Cross-section diagram corresponding to the circuit in (a). Note that all applied voltages are referred to the source terminal. The diagram in (b) is not drawn to scale.

mirrors the gate-drain voltage,  $V_{\rm gd}$ , regardless of the voltage applied between gate and source or gate and bulk terminals. In the absence of drain, source, bulk, and gate currents,  $V_{\rm ds}=0$  also guarantees that surface potential  $\varphi_{\rm o}$ , measured from the oxide semiconductor interface-to-the neutral zone of the bulk substrate, is the same throughout the channel region extending from x=0-to-x=L in the subject diagram. The aforementioned voltage,  $V_{\rm ox}$  includes the effects of parasitic trapped charge in the gate oxide, but it does not include the ramifications of work function differences that unavoidably prevail between the gate contact and the oxide and at the oxide–semiconductor interface. Note then that the voltage,  $V_{\rm gb}$ , measured at the gate terminal with respect to the bulk terminal is, ignoring work function phenomena, simply

$$V_{\rm gb} = V_{\rm ox} + \varphi_{\rm o}. \tag{1.51}$$

#### 1.2.2.1 Surface Charge Density

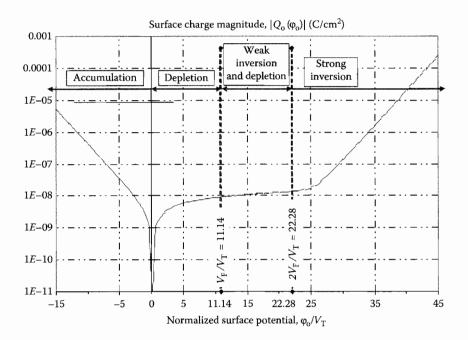

A pivotally important analytical tool serving to define the charge, capacitance, and static volt–ampere characteristics of a MOSFET, is the charge density,  $Q_o(\varphi_o)$ , in units of coulombs per unit area, established at the semiconductor surface as a function of the surface potential,  $\varphi_o$ . Several authors have identified this charge profile as [1–3]

$$Q_{\rm o}(\varphi_{\rm o}) = -\mathrm{sgn}(\varphi_{\rm o}) \left(\frac{\sqrt{2}\varepsilon_{\rm s} V_{\rm T}}{D_{\rm b}}\right) \sqrt{G(-\varphi_{\rm o}) + G(\varphi_{\rm o})e^{-2V_{\rm F}/V_{\rm T}}},\tag{1.52}$$

where  $\varepsilon_s = 1.037$  pF/cm denotes the dielectric constant of silicon, and

$$sgn(\phi_o) = \begin{cases} +1 & \text{for } \phi_o > 0 \\ -1 & \text{for } \phi_o < 0 \end{cases} \tag{1.53}$$

In Equation 1.52,

$$V_{\rm T} = kT/q \tag{1.54}$$

is the familiar semiconductor thermal voltage for which  $k = (1.38)(10^{-23})$  J/K is Boltzmann's constant,  $q = (1.60)(10^{-19})$  C is the magnitude of electron charge, and T is the absolute temperature of the semiconductor surface. The voltage,  $V_{\rm F}$ , in the radical on the right-hand side of Equation 1.52 is the Fermi potential, which is given by

$$V_{\rm F} \stackrel{\Delta}{=} V_{\rm T} \ln \left( \frac{N_{\rm A}}{N_{\rm i}} \right), \tag{1.55}$$

where  $N_A$  is the previously defined average acceptor impurity concentration of the bulk substrate in NMOS and  $N_i = (1.45)(10^{10})$  atoms/cm<sup>3</sup> is the intrinsic carrier concentration of silicon at  $T = 27^{\circ}$ C. The parameter,  $D_b$ , is known as the electron Debye length and is given by

$$D_{\rm b} \stackrel{\Delta}{=} \sqrt{\frac{\varepsilon_{\rm s} V_{\rm T}}{q N_{\rm A}}}.$$

(1.56)

Finally, the function,  $G(\varphi_0)$ , in Equation 1.52 is

$$G(\varphi_{\rm o}) = e^{\varphi_{\rm o}/V_{\rm T}} - 1 - \frac{\varphi_{\rm o}}{V_{\rm T}},$$

(1.57)

where it is understood that the surface potential,  $\varphi_0$ , measured with respect to the charge neutral zone in the bulk in Figure 1.19 is established in response to an applied gate-bulk voltage,  $V_{\rm gb}$ , or an applied gate-source voltage,  $V_{\rm gs}$ . Observe that  $G(\varphi_0) = G(-\varphi_0) = 0$  for  $\varphi_0 = 0$ , which delivers the expected result in Equation 1.52 of  $Q_0(0) = 0$ . It should be understood that Equation 1.52 is premised on Poisson's equation and the Boltzmann carrier relationship,

$$p(0) = N_{\rm A} e^{-\varphi_{\rm o}/V_{\rm T}},\tag{1.58}$$

where p(0) signifies the hole concentration at the surface if complete ionization of substrate dopant atoms is tacitly presumed. Since

$$p(0)n(0) = N_i^2, (1.59)$$

the corresponding concentration of free surface electrons, n(0), is

$$n(0) = \frac{N_i^2}{N_A} e^{\varphi_o/V_T} = N_A e^{(\varphi_o - 2V_F)/V_T},$$

(1.60)

where Equation 1.55 has been exploited.

Because  $G(\varphi_o)$  in Equation 1.57, as well as its companion relationship,  $G(-\varphi_o)$ , is a nonnegative number for all positive and negative values of the surface potential, the radical on the right-hand side of Equation 1.52 is a positive real number. Accordingly, Equation 1.53 forces  $Q_o(\varphi_o) > 0$  for  $\varphi_o < 0$  and  $Q_o(\varphi_o) < 0$  for  $\varphi_o > 0$ . The positive nature of the surface charge density for negative surface potentials is indicative of bulk substrate holes attracted to the semiconductor surface because of the force exerted by the surface electric field established in response to negative surface potential. From Gauss' law, this field, say  $E_o(\varphi_o)$  is simply

$$E_{\rm o}(\varphi_{\rm o}) = -\frac{Q_{\rm o}(\varphi_{\rm o})}{\varepsilon_{\rm s}} = {\rm sgn}(\varphi_{\rm o}) \left(\frac{\sqrt{2}V_{\rm T}}{D_{\rm b}}\right) \sqrt{G(-\varphi_{\rm o}) + G(\varphi_{\rm o})e^{-2V_{\rm F}/V_{\rm T}}}, \tag{1.61}$$

which is indeed negative for  $\phi_0$  < 0. Observe that Equation 1.58 supports the contention of an enhanced surface hole concentration when the potential established at the semiconductor surface is negative.

An equilibrium condition, which is more commonly referred to in the literature as the *flatband* operating condition, is reached when the applied gate-bulk or gate-source voltage produces a null surface potential, that is,  $\varphi_0 = 0$ . For  $\varphi_0 = 0$ , the net surface charge,  $Q_0(\varphi_0)$ , in Equation 1.52 is zero, as is the surface electric field,  $E_0(\varphi_0)$ , in Equation 1.61. Note further that by Equation 1.58,  $p(0) = N_A$ , which is the equilibrium hole concentration indicative of the NMOS bulk substrate for the transistor abstracted in Figure 1.17, assuming complete ionization of all substrate acceptor impurity atoms.

The negative surface charge prevailing for positive surface potentials, which gives rise to positive surface fields (field lines directed from the surface-to-the bulk substrate), reflects the surface charge depletion forged in response to holes repelled from the surface by  $\phi_o > 0$ . Once again, Equation 1.58 is supportive of the proffered rationale in that it confirms a diminished surface hole concentration for progressively larger  $\phi_o$ . Since departed holes leave in their wake a depletion zone of negative acceptor ions, the negative surface charge density resulting from positive surface potential is hardly surprising.

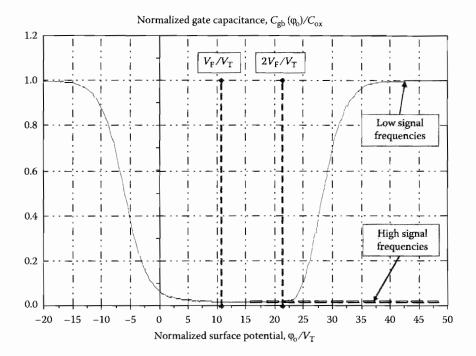

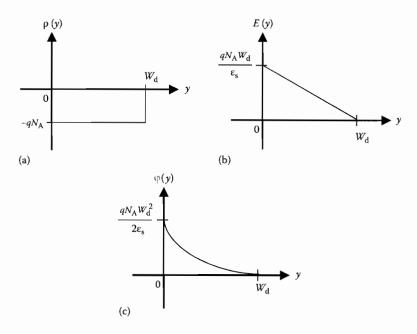

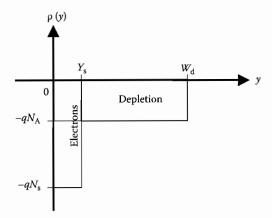

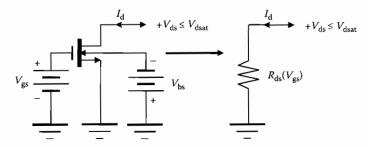

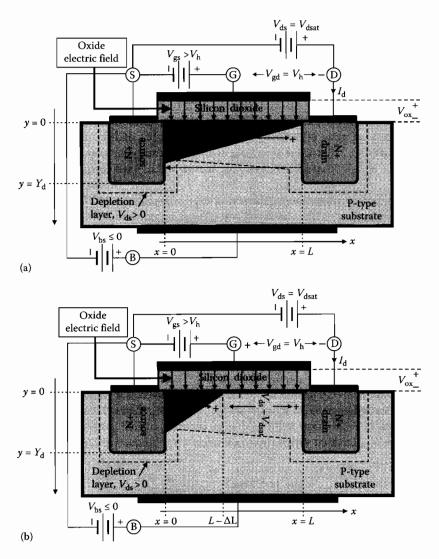

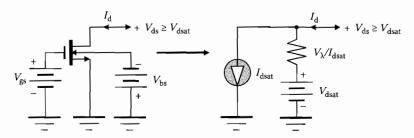

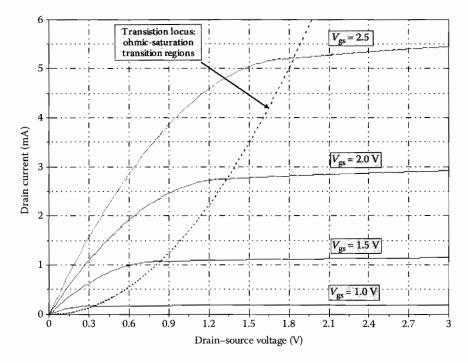

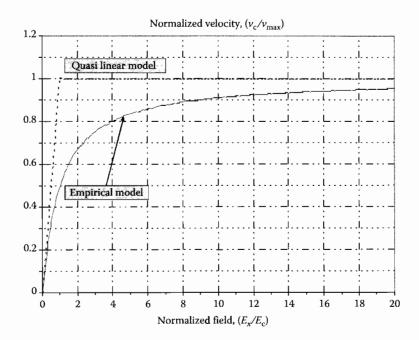

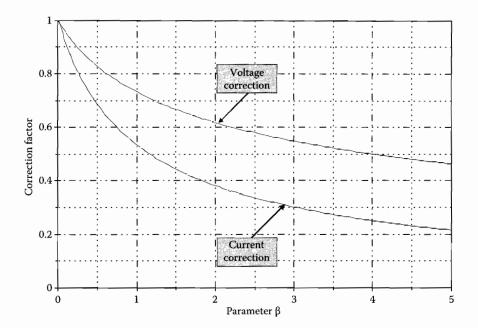

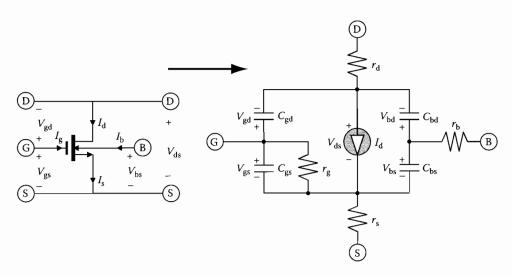

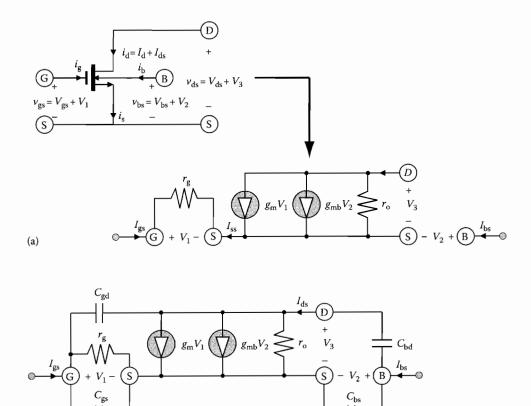

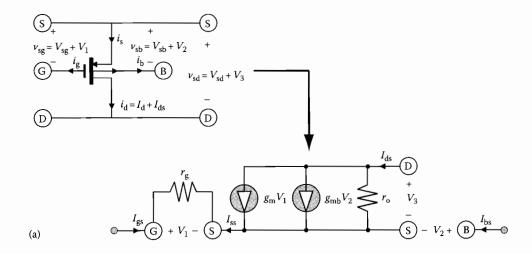

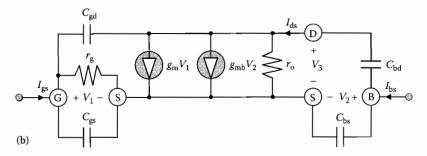

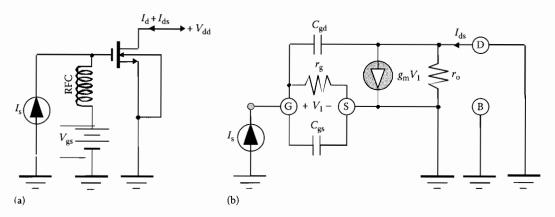

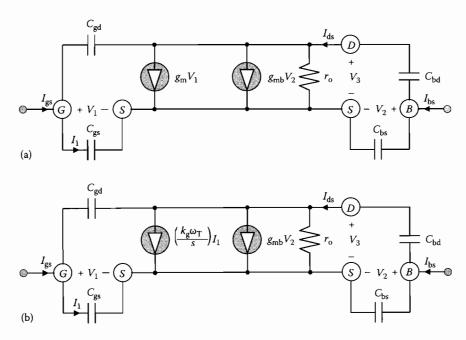

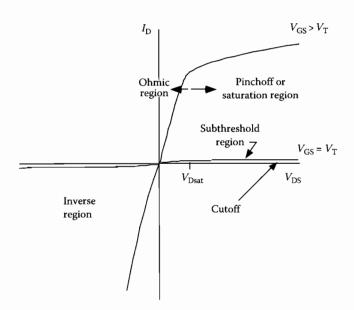

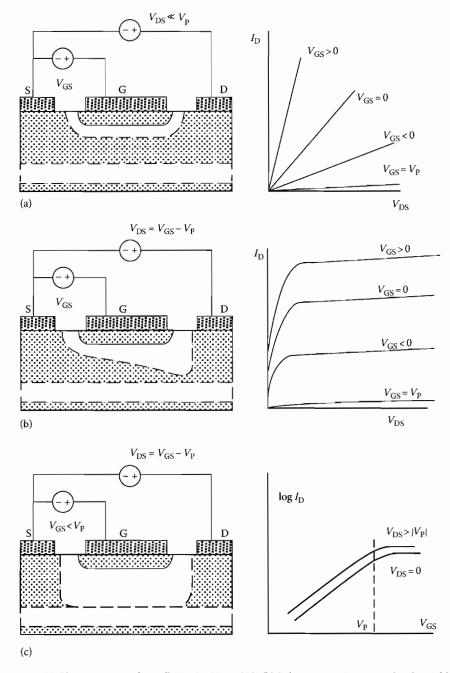

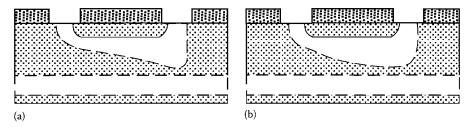

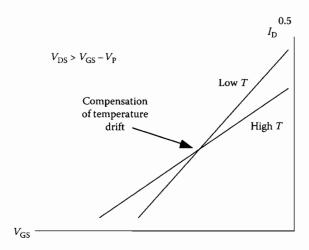

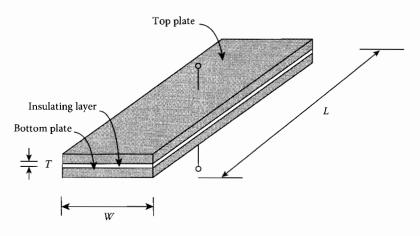

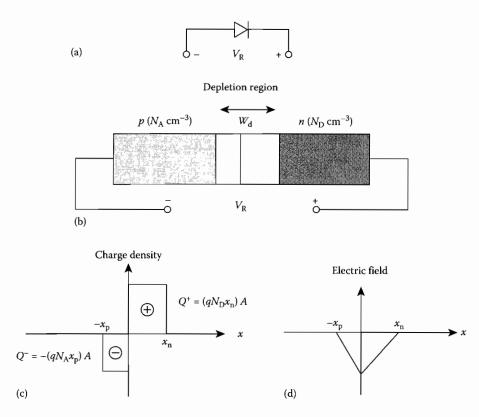

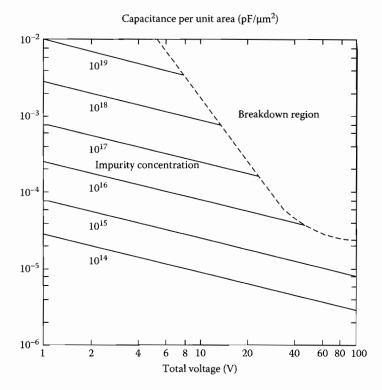

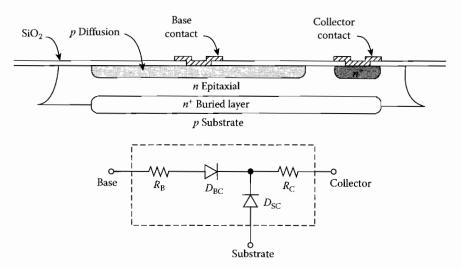

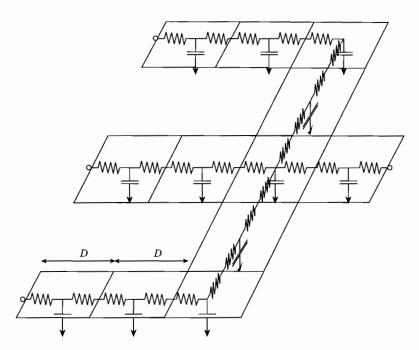

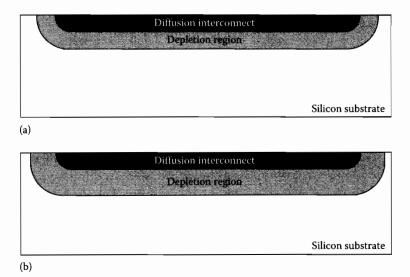

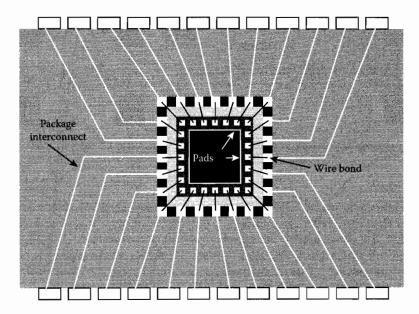

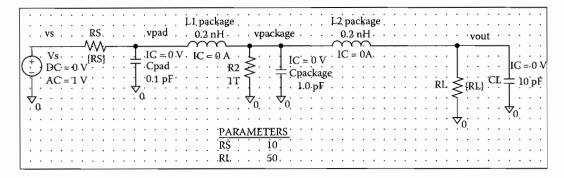

In addition to repelling holes from the semiconductor surface, Equation 1.60 indicates that the surface electron concentration increases as the surface potential,  $\varphi_o$ , rises above zero. Moreover, Equation 1.52 lends credence to this enhanced electron concentration claim since  $Q_o(\varphi_o)$  is seen as becoming monotonically more negative as surface potential  $\varphi_o$  rises above zero. Indeed, the impact of the positive electric field associated with  $\varphi_o > 0$  is to establish a force serving to attract the minority carriers (electrons) in the bulk substrate to the surface. For a surface potential in the range,  $0 < \varphi_o < V_F$ , the depletion charge contribution to the net surface charge continues to dominate over the charge associated with electrons cajoled to the surface, and the surface is said to operate in *depletion mode*. But as  $\varphi_o$  approaches and ultimately surpasses the Fermi potential,  $V_F$ , the impact on the nature of the surface charge becomes increasingly more interesting. For example, consider  $\varphi_o = V_F$ , for which Equations 1.58 and 1.60 yield  $p(0) \equiv n(0) = N_i$ , that is, the hole and electron concentrations at the surface are identically equal to the intrinsic carrier concentration. In effect, the surface region of the semiconductor changes from obviously P-type-to-intrinsic type, which is to say that the surface at  $\varphi_o = V_F$  is neither P-type nor N-type.