# A Gray-Code Current Mode ADC Structure

Bogdan M. Wilamowski

Dept. of Electrical and Computer Engineering

Auburn University

Alabama, 36849-5201, U.S.A

Mahmut Ersin Sinangil and Günhan Dündar Dept. of Electrical and Electronic Engineering Bogazici University Istanbul, TURKEY

Abstract— Analog to Digital Converters (ADC) are one of the most critical blocks in the area of electronics. This paper presents two new circuits for Gray-code current-mode analog to digital conversion which employs absolute value operation. The implementations of two different 5-bit converter circuits are discussed in this paper. 0.25µm CMOS technology with 5V power supply voltage is used for the circuits.

#### I. Introduction

Most processing is done in the digital domain whereas the signals in the world we live in are analog. Analog to Digital conversion which provides the link between these two domains is an extremely important research area. Moreover, Gray coding is a well known phenomenon with several advantages such as low power consumption, fewer glitches, and shorter transitions. Bringing these two concepts together, namely, building a Gray Coded ADC, is not a new idea. Such a circuit was discussed in [1] and a modified version is also given in [2, 3]. More recent research [4, 5] also discusses some important applications where Gray-code current-mode ADC can be used (e.g. image processing applications [5]). Gray-coding ADC's give better results regarding offset errors in circuit realizations as compared to their binary counterparts [6].

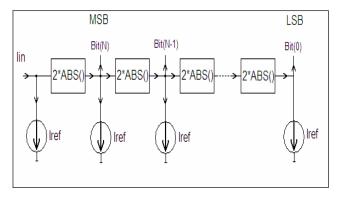

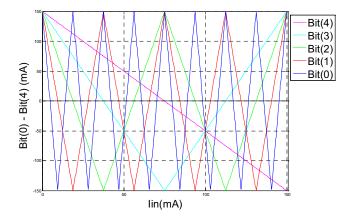

The Gray-code A/D conversion presented in this paper is based on the absolute value operation. The circuits presented are all current-mode and take  $I_{\rm IN}$  as their input. A fixed current,  $I_{\rm REF}$ , is subtracted from the input current in each stage and the remaining current is rectified and doubled in magnitude. By repeating this process as shown in Fig. 1, a Gray coding scheme can be realized. The first bit on the left is the Most Significant Bit and the last bit on the right is the Least Significant Bit. A demonstration of this concept is done in Matlab as shown in Fig. 2.  $I_{\rm REF}$  is taken as  $150\mu A$  and the input is swept from 0 to  $150\mu A$ . By looking at the sign of the current at various points, the Gray-coded form of the input can be generated.

For the implementation of this algorithm, an absolute value circuit with a wide operating range and very good precision is required. There are many proposed absolute value circuits in the open literature. The absolute value circuit is the most

crucial building block of this design. Its properties determine the operating range and precision of the overall circuit. Hence, a thorough simulation of the absolute value block is necessary to ensure correct operation of the overall circuit.

**Figure 1.** Block Diagram of the Gray Code Conversion Algorithm

**Figure 2.** The result of the gray code conversion algorithm simulated in Matlab

## II. ANALYSIS AND DESIGN OF THE ABSOLUTE VALUE CIRCUIT

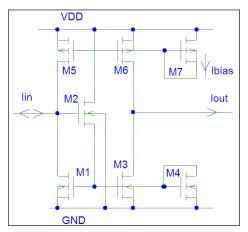

The circuit in Fig. 3 is a half wave rectifier and employs seven transistors. The branches on which transistors M2 and M4 are placed are the key elements in this design. When the input current  $I_{\rm IN}$  is positive, M2 is ON and the excess current on M1 due to the input current is mirrored to output over M3. When the input current is negative, M2 is off and hence M1 is in the resistive region. The output current is nearly zero because the current supplied by M6 is equal to the current pulled by M3. As a result, the circuit works as a half-wave rectifier.

Figure 3. Half-Wave Rectifier Circuit

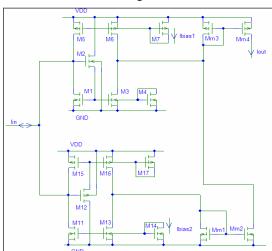

By using another circuit with the same logic, the other half of the signal can also be rectified. Hence, by subtracting the output currents of the two portions, a full-wave rectifier can be realized as shown in Fig. 4.

Figure 4. Absolute value circuit

For the circuit in Fig. 4, a power supply of 5V is used and the bias currents for the circuit are 0.5mA. A current mirror realized with NMOS transistors are used for the subtraction operation. Since the algorithm for Gray code conversion requires a 2\*ABS() operation, another current mirror realized with PMOS transistors are used to multiply the output current by two.

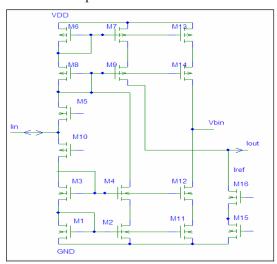

Another absolute value circuit is given in Fig. 5. This circuit employs sixteen transistors and again uses 5V power supply. Transistors M3, M4, M5, M8, M9, M10 and M19 constitute the rectifying operation whereas M11, M12, M13 and M14 are used for converting the current to a binary voltage. Transistors M15 and M16 are used to subtract the reference current from the output.

Figure 5 Absolute Value Circuit

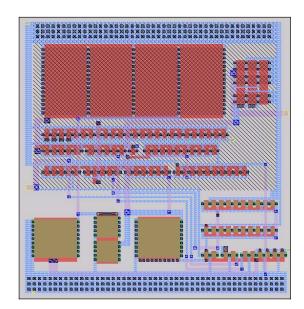

The layout of the circuit in Fig. 4 is given in Fig.6 and the extracted netlist is used for the simulations. The layout of the circuit in Fig. 5 which is simpler is not given in this paper due to space considerations.

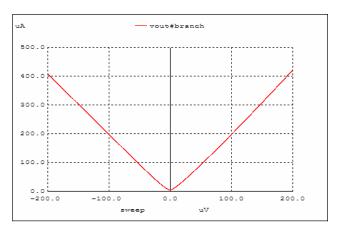

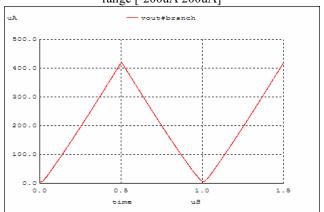

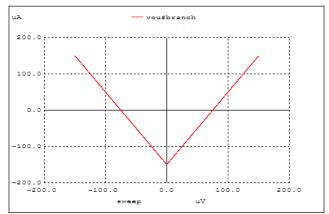

Transient analysis results for the absolute value circuit in Fig.4 show that this circuit can work in the range  $[0,200\mu A]$  with good linearity, up to a frequency of 1MHz. The DC analysis and transient analysis results of the same circuit are given in Figures 7 and 8, respectively to illustrate these results.

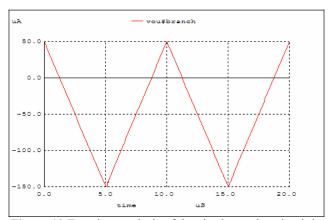

The transient analysis results of the circuit in Fig. 5 show that this circuit can work up to a few hundred kHz with good linearity in the range  $[0\ 150\mu A]$ . The simulation results for this circuit are given in Figures 9 and 10.

Figure 6. Layout of the absolute value circuit in Fig. 4

**Figure 7.** DC Analysis of the absolute value circuit for the range [-200uA 200uA]

**Figure 8.** Transient Analysis of the absolute value circuit in Fig.4 at 1MHz

Figure 9 DC Analysis of the absolute value circuit in Fig.5.

**Figure 10** Transient analysis of the absolute value circuit in Fig.5 at 100kHz.

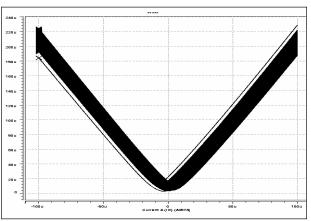

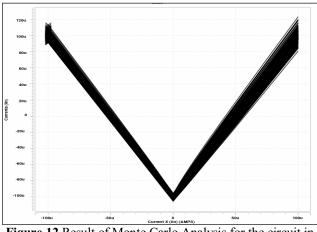

In order to depict the effects of parameter variations on the design, Monte Carlo Simulations are done by varying W, L and VTHO parameters of each transistor according to values supplied by the manufacturer. The Monte Carlo simulation results for the circuit of Fig.4 are given in Fig. 11 and results for the circuit in Fig 5 are given in Fig.12.

Figure 11. Result of Monte Carlo Analysis for the circuit in Fig. 4

**Figure 12** Result of Monte Carlo Analysis for the circuit in Fig. 5

## III. IMPLEMENTATION OF THE GRAY CODE CONVERTER CIRCUIT WITH THE ABSOLUTE VALUE OPERATION

After designing the absolute value circuits, 5-bit Graycode current-mode A/D converters are constructed by cascading these absolute value circuits as shown in Fig.1. NMOS current mirrors are used to subtract  $I_{REF}$  currents at various nodes in the design.

The conversion of the currents to digital words is not discussed in this paper but different approaches can be used to do this. Transistors M13, M14, M15 and M16 in Fig.5 are used for this purpose to illustrate the concept. An external circuit can also be used for each absolute value cell to convert the current signal to a digital bit as discussed in [4],

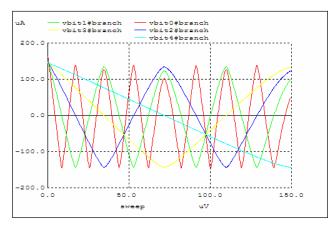

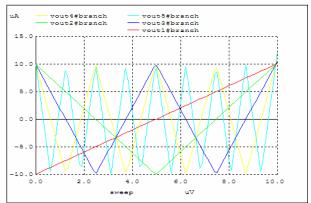

The output waveforms of the ADCs constructed with the absolute value circuits discussed above are given in Figures 13 and 14. The DC analysis is done for an input current in the range [0,150 $\mu$ A.] for the first circuit and [0, 10 $\mu$ A] for the second circuit.

**Figure 13.** DC Analysis for the 5-bit Converter Circuit realized with the absolute value circuit in Fig.4

Figure 14. DC Analysis for the 5-bit Converter Circuit realized with the absolute value circuit in Fig.5

#### V. CONCLUSION

The design presented in this paper is based on Gray-Coding A/D Conversion. Two different circuits operating for currents in the range [0,150µA] and [0, 10µA] are presented. The range of operation for both of these circuits is around 200µA. The highest frequency possible with the first circuit is around one megahertz whereas for the second circuit, it is a few hundred kilohertz. The first circuit is more complex and consumes more power than the second circuit presented in this paper. The properties of the circuits heavily depend on the characteristics of the absolute value circuit block so the realization of a linear rectifying circuit is very important. The absolute value circuits used in this work are by no means the only solution. By employing other absolute value circuits, different behavior can be observed. The reason for illustrating the behavior with two different absolute value circuits is to prove the operation of the general concept irrespective of the specific implementation.

Future work includes evaluation of different types of absolute value circuits to realize more reliable and less area consuming Gray-Code Current-Mode ADC's. Furthermore, these circuits will be implemented as chips. Finally, it is planned to use the Gray-Code Current-Mode ADC's in larger systems.

### REFERENCES

- F.D. Waldhauer, "Analog-to-Digital Converter", U.S. Patent number 3,187,325, June 1, 1965

- [2] J. Robinson, "Continuous Time Domain Analog-Digital Converter", U.S. Patent number 4,667,180, May 19, 1987

- [3] J. Robinson, "Analog-Digital Converter", U.S. Patent number 4,691,290, Sep. 1, 1987

- [4] L. Vesalainen, J. Poikonen, M. Pankaala, A. Paasio, "A Gray-Code Current-Mode ADC for Mixed-Mode Cellular Computer," *Proceedings of ISCAS'04*, Vol. 3, pp. 81-85, May 2004.

- [5] L. Vesalainen, J. Poikonen, M. Pankaala, A. Paasio, "First Measurement Results of a Gray-Code Current-Mode ADC," Proceedings of Norchip, pp 249-252, Nov 2004.

- [6] S. Signell, B. Jonsson, H. Stenstrom, N. Tan, "New A/D Converter Architectures based on Gray Coding", *Proceedings of ISCAS'97*, Vol. 1, pp. 413-416, June 1997,.