# A Low Voltage to High Voltage Level Shifter Circuit for MEMS Application

Dong Pan<sup>1, 3</sup>, Member, IEEE, Harry W. Li<sup>2</sup>, and Bogdan. M. Wilamowski<sup>3</sup>, Fellow, IEEE

<sup>1</sup> Micron Technology, Inc., Boise, ID 83716

Abstract— High voltage (>15V) drivers are integrated into the VLSI chip for MEMS application with the development of SOC technology. The pre-driver circuit, which generates the pull-up and pull-down signal, is mainly a voltage level shifter circuit. It converts the low voltage control signal to high voltage control signal. Conventional voltage level shifter circuit using high voltage NMOS and high voltage PMOS operates well on 0.8 um process. However, with the continuous process shrinking, conventional voltage level shifter circuit is not suitable for high voltage power supply due to the reduced breakdown voltage of the high voltage devices. Although stacked high voltage devices can be applied to solve this issue, the circuit will have DC leakage current and the internal high voltage swing problem.

This paper describes a new low voltage to high voltage converter circuit. By using all the low voltage devices, the DC leakage current and the high voltage swing node have been eliminated. This circuit is fabricated in 0.35 SOI process. Both simulation and test results validate its operations for controlling high voltage drivers.

## I. INTRODUCTION

High voltage (>15V) drivers are integrated into the VLSI chip for MEMS application with the development of SOC technology. The high voltage drivers usually apply high voltage NMOS (HVNMOS) and high voltage PMOS (HVPMOS) as the pull-up and the pull-down device. The pre-driver circuit, which generates the pull-up and pull-down control signal, is mainly a voltage level shifter circuit. It generates the HVNMOS control signal and converts the low voltage control signal to high voltage HVPMOS control signal. Reliability, and the low power consumption, especially the low DC current are major concerns for a practical pre-driver circuit.

Previous research of the voltage shifter circuit [1] using high voltage NMOS and high voltage PMOS operates well on 0.8 um process. However, with the continuous process shrinking, breakdown voltage of those high voltage devices, especially the P device, also reduces. In order to maintain the high operation voltage, stacked devices can be used in the pre-driver [2][3]. The voltage shifter circuit using stacked HV devices, on the other hand, will experience DC leakage current and further increase the overall power consumption. At the same time, the internal nodes of the conventional voltage shift circuit have large voltage swing (changes from GND to the power supply). This large voltage swing will increase the complexity of the layout. It may even affect the reliability of the circuit due to the high electric field.

This paper describes a new low voltage to high voltage converter circuit without DC leakage current. It also reduces the voltage swing of the internal nodes.

### II. HV DEVICE STRUCTURE AND THE DRIVER CIRCUIT

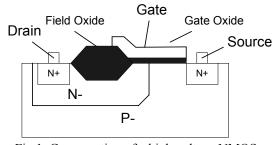

The high voltage devices can be manufactured using standard digital commercial process using special layout techniques [4]. Fig.1 shows the cross section of a high voltage device. The lightly doped N-well region (N-) creates a drift path. The breakdown voltage will be increased due to the reduced concentration level near the PN junction as shown in the follows [2]:

$$BV \cong \frac{\varepsilon_{si}(N_A + N_D)}{2qN_A N_D} E_{Max}^2 \tag{1}$$

Where  $\epsilon_{si}$  is the dielectric permittivity of silicon,  $N_A$  is the doping concentration of the acceptors of P-type material,  $N_D$  is the doping concentration of the donors in the N-type material, q is the charge of an electron (1.602E-19 coulombs), and  $E_{Max}$  is the critical electric field for silicon.

At the same time, the field oxide is applied in the HV device to protect the gate from the high electrical field.

Fig.1. Cross section of a high voltage NMOS.

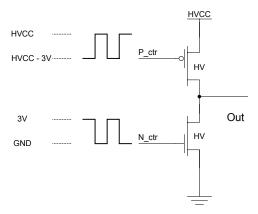

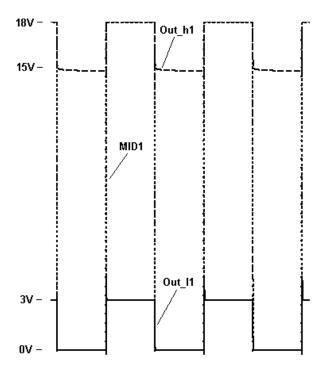

Fig.2 shows a high voltage driver circuit using a HVNMOS and a HVPMOS. The drain to source breakdown voltage ( $V_{ds}$ ) is very high for these devices while the gate to source breakdown voltage ( $V_{gs}$ ) is much lower. For the 0.35um process used in this research project, the  $V_{gs}$  breakdown voltage of HVNMOS is about 5V and the  $V_{ds}$  breakdown voltage is higher than 15V. Low voltage signal can be used to drive the HVNMOS directly. For the HVPMOS, the  $V_{sg}$  breakdown voltage of HVNMOS is also about 5V while the  $V_{sd}$  breakdown voltage is about 10V. In this project, the control signal for the HVNMOS varies from 0 and 3V. The control signal for HVPMOS should close to power supply (HVCC) to avoid high  $V_{sg}$  voltage. The control signal is design to vary from

<sup>&</sup>lt;sup>2</sup> University of Idaho, Electrical and Computer Engineering Department, Moscow, ID 83844 <sup>3</sup> University of Idaho, College of Engineering, 800 Park Blvd. Suite 200 Boise, ID 83712

Fig.2. A high voltage driver circuit and its control signals.

HVCC-3V to HVCC. Thus, special pre-driver circuit must be used to generate the control signals.

#### III. A CONVENTIONAL VOLTAGE LEVEL SHIFTER CIRCUIT

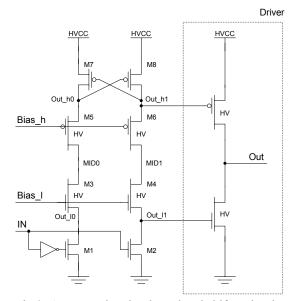

A conventional voltage shifter circuit is shown in Fig.3. It applies two HVNMOS and two HVPMOS devices. Two bias voltages are used to limit the voltage swing of the Out\_11 and Out\_h1 nodes. When the input is high, M2 turns on and pulls down the Out\_11 node to GND. The generated large  $V_{\rm gs}$  of M4 will turn on the M4 and pull the node MID1 to GND. M6 and Bias\_h will keep Out\_h1 lower than biash+|V\_{\rm thp}| (If Out\_h1 is higher than biash+|V\_{\rm thp}|, M6 will turn on and pull the node Out\_h1 down to biash+|V\_{\rm thp}|). The cross-coupled transistor M7 and M8 operate like a current sense circuit [5]. It will further pull down the voltage of out\_h1 node to about Bias\_h. On the contrary, when the input is low, the Out\_h1 output will be high and the Out\_11 will be low.

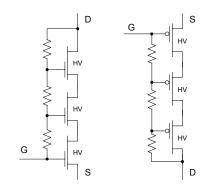

The maximum voltages across the drain and source of the HVPMOS and the HVNMOS in Fig.3 are close to HVCC. If HVCC is higher than the breakdown voltage, normal HV devices cannot be used. Fig.4 shows the alternative configuration of the HV device by stacking them together. The voltage across the source and drain of each transistor is about one third  $V_{ds}$  of the entire stacked device. Replacing the normal high voltage devices in Fig.3 by the stacked devices, the maximum operation voltage HVCC can be higher than the breakdown voltage of the signal HV device.

The stacked HV device, on the other hand, will have DC leakage current from gate to drain through the resistors. Depended on the circuit configuration, the leakage current varies from 10uA to 500uA. At the same time, the node MID1 and MID0 will experience high voltage swing form GND to HVCC as shown in Fig.5. These high voltage swing node will increase the complexity of the layout. It may even affect the reliability of the circuit due to the high electric field.

### IV. A NON HIGH VOLTAGE SWING LVHV CIRCUIT

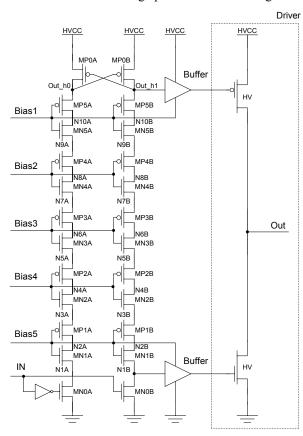

A proposed low to high voltage shifter circuit is shown in Fig.6. Five bias voltages are applied in this circuit. All the transistors used in this level shifter circuit are normal low

Fig.3. A conventional voltage level shifter circuit.

Fig.4. Stacked HVNMOS and Stacked HVPMOS.

Fig. 5. Output and internal nodes of the shifter circuit.

voltage devices. The operation of the new level shifter circuit is similar to the original circuit expect the drain connected PMOS and NMOS pairs. When input is high, transistor MN0B starts to conduct and voltage of node N1B will pull down to GND. Since  $V_{gs}$  of MN1B is larger than  $V_{th}$ , MN1B conducts and pulls node N2B to GND. If voltage of node N3B is larger than Vbias5 +  $|V_{thp}|$ , MP1B will conduct until the Voltage of node N3B is less than Vbias5 +  $|V_{thp}|$ . Similar to the operation of MN1B and MP1B pair, MN2B and MP2B, MN3B and MP3B, MN4B and MP4B, MN5B and MP5B transistor pairs will pull down the voltage of the node Out\_h1 to less than Vbias1 +  $|V_{thp}|$ . The cross-coupled PMOS pair MP0A & MP0B will further stabilized the voltage of the Out\_h0 and Out\_h1 to about HVCC and Vbias1. Similarly, when the input is low, the Out\_h1 will be HVCC and out \_11 will be around Vbias5.

The maximum  $V_{ds}$  across the transistor in the level shifter circuit is about the voltage difference between two bias voltages. In this project, 18V is chose for HVCC and 3V, 6V, 9V and 12V are picked for bias1, bias2, bias3, bias4 and bias5 respectively. Thus, the maximum  $V_{ds}$  of all the transistors is about 3V. At the same time, the maximum voltage swing for a particular node is reducing from 18V to about 6V.

#### V. SIMULATION RESULT AND CIRCUIT FABRICATION

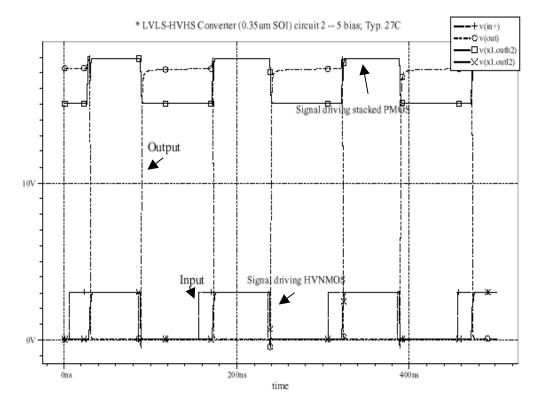

Simulation result of the proposed voltage level shifter circuit is shown in Fig.9. The low voltage input signal generates both the low voltage pull-down and the high voltage

Fig.6. A proposed voltage level shift circuit.

pull-up control signals through the voltage level shifter circuit. The pull-up and pull-down signals further generates the high voltage swing output signals through the final high voltage driver circuit.

The speed of the level shift circuit is limited by time need to charge and discharge the internal nodes such as M1A/M1B, M2A/M2B, etc. Simulation shows this circuit is able to operate under 1M Hz frequency.

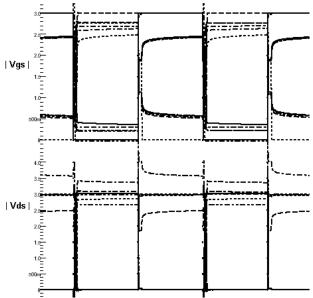

Since all the devices used in the voltage shifter circuit are low voltage devices, the  $|V_{ds}|$  and  $|V_{gs}|$  of all the devices must below the breakdown voltage (both are 5V for this project). Fig.7 shows the simulation results of the  $|V_{ds}|$  and  $|V_{gs}|$  for all devices. The maximum  $|V_{ds}|$  is about 3.5V while the maximum  $|V_{gs}|$  is about 4.5V. Both are lower than the breakdown voltage.

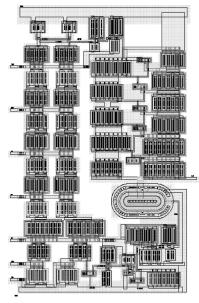

The circuit is implemented in 0.35um SOI process (Fig.8). The silicon test result matches our simulation result.

Fig.7. |Vgs| and |Vds| simulation results of all the devices.

Fig.8. Circuit implementation on 0.35um SOI process.

Fig.9. Simulation result of the proposed voltage level shifter circuit.

## VI. CONCLUSION

A low voltage to high voltage level shifter circuit for MEMS application is designed using normal low voltage devices. It features zero DC current consumption while reduces internal voltage swing.

The simulation result indicates that the magnitude of the  $V_{\rm gs}$  of all devices is less than 3.5V and the magnitude of the  $V_{\rm ds}$  of all devices is less than 4.5V. The circuit is fabricated in 0.35 SOI process. The test result matches the simulation test.

## VII. ACKNOWLEDGMENT

The authors gratefully acknowledge the contributions of the Idaho NASA EPSCoR program for its support.

#### REFERENCES

- [1] Harry W. Li, Jonathon C. Stiff, Kevin M. Buck, NASA EPSCoR Idaho Space Grant Consortium (ISGC): HV SOI Transistors for Power Management Circuitry for Systems on a Chip. June 1, 1999 to March 31, 2000.

- [2] Thomas Cougar Van Eaton, "Design and implementation of High-Volatge CMOS Devices in a 0.8um 5V CMOS Process", thesis, Washionton State University, Aug. 1998.

- [3] Herbert L. Hess, Russel J. Baker, "Transformerless Capacitive Coupling of Gate Signals for series Operation of the Power MOS Devices", *IEEE Transaction on Power Electronics*, Vol. 15, No. 5, pp. 923-930, Sep. 2000.

- [4] A.Koroncai, etc. "A 60V CMOS DC/DC Converter for ISDN Applications," *IEEE Journal of Solid-State Circuits*, Vol. 23, No. 3, pp. 824-829, June, 1988.

- [5] Joonbae Park, Jeongho Lee, and Wonchan Kim,"Current Sensing Differential Logic: A CMOS Logic for High Reliability and Flexibility," *IEEE Journal of Solid-State Circuits*, Vol. 23, No. 3, pp. 824-829, June, 1988.