# CMOS Implementation of a Pulse-Coupled Neuron Cell

Bogdan M. Wilamowski, Richard C. Jaeger, Mary Lou Padgett wilam@eng.auburn.edu jaeger@eng.auburn.edu mpadgett@eng.auburn.edu

Department of Electrical Enginering

Lawrence J. Myers

myerslj@vetmedauburn.edu

Institute for Biological Detection Systems

Auburn University, AL 36849-5201

#### ABSTRACT

Recent applications of pulse-coupled neural networks have demonstrated the need for a simple pulse-coupled neuron circuit which can easily be implemented in CMOS technology. The proposed cell uses a positive feedback circuit with two capacitors. One capacitor corresponds to the external sodium ion potential, and the other to the internal potassium ion potential. This cell body circuit is also used as a neural segment in an artificial axon. When linked by large resistors, these neural segments display many properties expected in a biological axon. SPICE simulations verify proposed circuit operation.

### 1. Introduction

Due to their capabilities with regard to image smoothing, image segmentation and feature extraction, pulse-coupled neural networks are gaining attention [1-5]. Many different models of pulse-coupled neural networks have been proposed. Most of those electronic models are based on voltage or current controlled oscillators. Other models use spike generators which include a step function generator with negative feedback [6-12]. A good review of electronic models of pulse-coupled neural networks is given in [13,14]. In the present work, a new simple circuit implementation of a pulse type neural cell is proposed. This cell uses the concept of two capacitors with two different time constants. One capacitor is used to integrate incoming signals, and the second is responsible for the refractory period and threshold change after the pulse is generated.

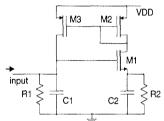

Fig. 1 Concept diagram of the neural cell

### 2. Concept of the cell

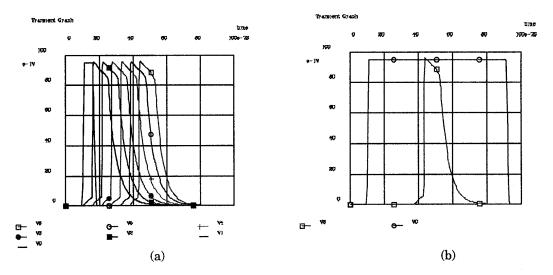

The concept diagram of the neuron cell is shown in Fig. 1. The circuit has two capacitors, C1 and C2. The stored charge on capacitor C1 corresponds to the charge of sodium ions accumulated on the external side of the neuron membrane, and the charge stored on capacitor C2 corresponds to the potassium ions stored inside of the neuron cell. The potential due to sodium ions changes faster than the potential due to potassium ions. Therefore the time constant of the C1 circuit is smaller then the time constant of the C2 circuit. If the potential on C1 exceeds the potential on C2 by the threshold value of transistor M1, then transistor M1 will activate transistors M2 and M3, leading to the rapid increase of the potentials on both capacitors. This positive feedback through transistors M1, M2 and M3 will be quickly terminated once capacitor C2 is fully charged and all transistors are turned off. During the recovery process, capacitor C2 is slowly discharged by resistor R2 and the neuron cell does not respond to incoming excitations. The transient response of the circuit of Fig 1 for a shifted sinusoidal excitation is shown in Fig 2. During this refractory period the input threshold slowly decreases to the initial value.

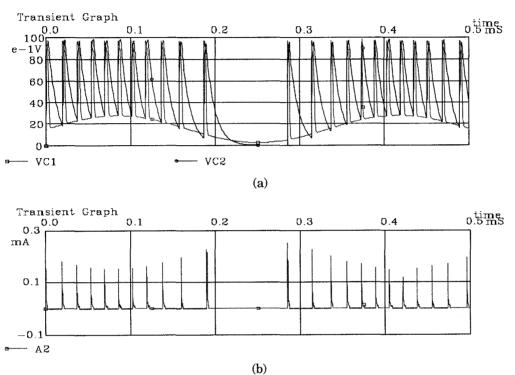

In an actual CMOS implementation, resistors should not be used. In order to limit maximum input excitation and to generate a nonlinear input to frequency conversion, an additional transistor M4 is connected in diode mode as in Fig. 3. They are replaced by transistors as shown in Fig. 3. In this circuit, the both positive and negative current pulse outputs are generated. Each output may have a different weight adjusted by the L/W ratio of output transistors. An example of the output current generated by the circuit of Fig. 3 with an input similar to Fig. 2 is shown in Fig. 4(a), while Fig. 4(b) shows the response for a ramp generator at the input. One can observe an almost constant frequency for high input excitation.

Fig. 2. Responses of the circuit from Fig. 1 excited with a shifted sinusoidal input, (a) voltages on C1 and C2, (b) current of transistor M3

Fig. 3. Actual circuit of neural cell in CMOS implementation.

## 3. Distributed cells - pulse shaping action in axons

While neural cells in nervous systems are small, their axons for transmitting pulse trains may be very long. Those axons may be coated with a myelin sheath, which takes the form of a series of nodes. These nodes of Ranvier create a segmented effect, allowing passage of sodium and potassium ions. Without the pulse shaping action, traveling pulses could be seriously attenuated and dispersed.

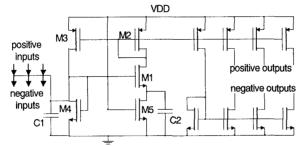

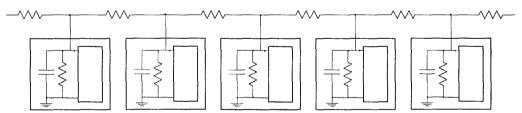

Therefore axons which have similar membrane structures should be able to regenerate the shape of transmitting pulses. It is interesting that the proposed neural circuit can be also used for creation of an axon. The inputs of a series of neural cells can be connected in a chain by simple coupling resistors as shown in Fig. 5.

Fig. 4. Outputs of the circuits of Fig. 3 (a) with shifted sinusoidal excitation, (b) with ramp current excitation.

Fig. 5. Neural segments connected in a chain to form an axon.

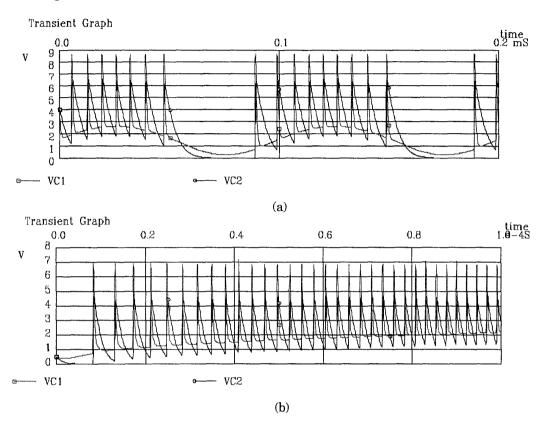

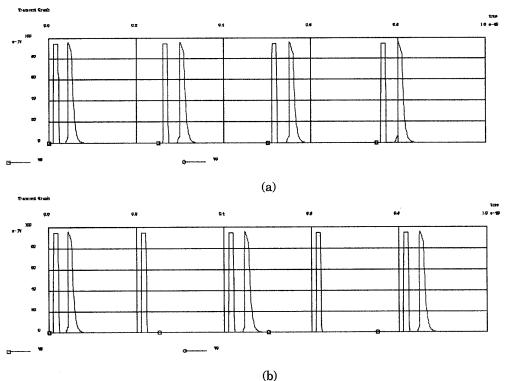

Such a diagram has very interesting property. The incoming pulses are shaped as they move along the axon. Fig. 6 demonstrates the pulse shaping action for both narrow and wide pulses. When a pulse is too narrow it will be annihilated. On other hand, if the pulse is very wide it can generate a series of two or more pulses. The time interval between pulses will be shortened as the magnitude of the input excitation increases.

When the axon circuit is excited with a series of pulses, then those pulses can be transmitted through the axon if pulses are widely separated, as shown in Fig. 7 (a). Alternatively, only every second pulse can be transmitted when the time interval between pulses is small, as shown in Fig. 7 (b). Note, that this circuit has full symmetry and the pulse shaping action can be observed for both directions.

Also, if two pulses travel from opposite directions they will annihilate each other. Such antidromic collision is also observed in real axons.

Fig. 6. Pulse shaping action for (a) narrow pulse (voltages on all nodes shown) and (b) wide pulse (only the input pulse and the last node shown).

Fig. 7. Axon response for the series of pulses (a) with large time interval between pulses all pulses are transmitted through axon, (b) with smaller interval between pulses only every second pulse is transmitted.

#### 4. Conclusion

A pulse-coupled neuron circuit is proposed. This circuit uses a positive feedback circuit with two capacitors. One corresponds to the sodium ion potential and the other corresponds to the potassium ion potential. The proposed cell can be easily implemented in CMOS technology. The circuit behaves like a real neuron, generating a pulse train in which the frequency increases with an increase of input excitation. The circuit threshold increases after pulse generation and then gradually returns to the initial level. When neural segments are coupled by large resistors in a chain, an electronic axon is formed, in which most of the properties of biological axons can be observed. Operation of the proposed circuit was verified with SPICE simulations.

# 5. Bibliography

- [1] H.J. Ranganath, G. Kuntimad, J.L.Johnson, "Pulse Coupled Neural Networks for Image Processing", *PCNN International Workshop*, Huntsville, Alabama, April 5, 1995.

- [2] J. Donald, L. Akers, "An Adaptive Neural Processing Node," *IEEE Trans. on Neural Networks*, vol. 4, no. 3, pp. 413-426, May 1993.

- [3] R. Eckhorn, H.J. Reitboeck, M.Arndt, P.Dicke, "Feature Linking via Stimulus-Evoked Oscillations: Experimental results from Cat Visual Cortex and Functional Implications from a Network Model," *Proc. Int JCNN*, Washington D.C. Vol. 1, 723-730, 1989.

- [4] R. Eckhorn, H.J. Reitboeck, M.Arndt, P.Dicke, "Feature Linking via Synchronization among Distributed Assemblies: Simulation Results from Cat Visual Cortex," Neural Computation 2, 293-307 1990

- [5] J.L. Johnson" Waves in Pulse Coupled Neural Networks, "Proc. of the World Congress on Neural Networks, Vol. 4, INNS Press, 1993.

- [6] A.F. Murray, "Pulse Arithmetic in VLSI Neural Networks," IEEE Micro Magazine, pp. 64-74, Dec. 1989.

- [7] J.E. Tomberg, K.K. Kasaki, "Pulse-Density Modulation Technique in VLSI Implementations of Neural Network Algorithms," *IEEE Journal of Solid-State Circuits*, vol. 25, no. 5, pp. 1277-1286, Oct. 1990.

- [8] A. F. Murray, D. D. Corso, L. Tarassenko, "Pulse Stream VLSI Neural Networks Mixing Analog and Digital Techniques," *IEEE Trans. Neural Networks*, Vol. 2, No2, pp. 193-204, March 1991.

- [9] A. Hamilton, A. F. Murray, D. J. Baxter, S. Chuecher, H. M. Reekie, L. Tarassenko, "Integrated Pulse Stream Neural Network: Results, Issues, and Pointers," *IEEE Trans. Neural Networks*, Vol. 3. No. 3, pp. 385-393, May 1992.

- [10] J. L. Meador, A. Wu, C. Cole, N. Nintunze, P. Chintrakulchai, "Programmable Impulse Neural Circuits," *IEEE Trans. Neural Networks*, Vol. 2, No. 1, pp. 101-109, January, 1991.

- [11] G. Moon, M. E. Zaghloul, R. W. Newcomb, "VLSI implementation of Synaptic Weighting and Summing in Pulse Coded Neural-Type Cells," *IEEE Trans. Neural Neetworks*, Vol. 3, No. 3, 394-403, May 1992.

- [12] T. G. Clarkson, C. K. Ng, Y. Guan, "The pRAM: An Adaptive VLSI Chip," *IEEE Trans. Neural Networks*, Vol. 4, No.3, pp. 408-412, May 1993.

- [13] M. E. Zaghloul, J. L. Meador, R. W. Newcomb, Silicon implementation of pulse coded neural networks, Kluwer, Boston 1994.

- [14] A. F. Murray and L. Tarassenko, Analogue Neural VLSI: Pulse Stream Approach, Chapman & Hall, London, UK, 1994.