## SRC TOPICAL RESEARCH CONFERENCE "DEVICES AND STRUCTURES", San Diego, CA June 15. 1984

# NOVEL BIPOLAR TRANSISTOR STRUCTURES AND LOADS

B.M. WILAMOWSKI, R.H. MATTSON, Z.J. STASZAK,

R. CRAIGIN, A. MUSALLAM, J.N. FORDEMWALT

PRESENTED BY R.H. MATTSON

UNIVERSITY OF ARIZONA

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

TUCSON, AZ 85721

#### OUTLINE

- 1. INTRODUCTION

- 1.1 BACKGROUND

- 1.2 RISEARCH GOALS

- 2. SATURATION PROTECTED BIPOLAR TRANSISTORS

- 2.1 THE SIT SATURATION PROTECTED BIPOLAR TRANSISTOR

- 2.2 THE PNP SATURATION PROTECTED BIPOLAR TRANSISTOR

- 2.3 CONCLUSIONS

- 2.4 DEVICE FABRICATION

- 3. Punch-Through Space-Charge-Limted Loads

- 3.1 DEVICE SIMULATION

- 3.2 DEVICE FABRICATION

- 4. SUMMARY AND CONCLUSIONS

- 26. B. M. Wilamowski, R. H. Mattson, Z. J. Staszak, R. Craigin, A. Musallam, J. N. Fordemwalt, "Novel bipolar transistor structures and loads", <u>SRC Topical Research Conference</u>, June 15, 1984, San Diego, USA.

# SRC TOPICAL RESEARCH CONFERENCE "DEVICES AND STRUCTURES", San Diego, CA June 15, 1984

# NOVEL BIPOLAR TRANSISTOR STRUCTURES AND LOADS

B.M. WILAMOWSKI, R.H. MATTSON, Z.J. STASZAK, R. CRAIGIN, A. MUSALLAM, J.N. FORDEMWALT

PRESENTED BY R.H. MATTSON

UNIVERSITY OF ARIZONA

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

TUCSON, AZ 85721

#### OUTLINE

- 1. INTRODUCTION

- 1.1 BACKGROUND

- 1.2 RISEARCH GOALS

- 2. SATURATION PROTECTED BIPOLAR TRANSISTORS

- 2.1 THE SIT SATURATION PROTECTED BIPOLAR TRANSISTOR

- 2.2 THE PNP SATURATION PROTECTED BIPOLAR TRANSISTOR

- 2.3 CONCLUSIONS

- 2.4 DEVICE FABRICATION

- 3. PUNCH-THROUGH SPACE-CHARGE-LIMTED LOADS

- 3.1 DEVICE SIMULATION

- 3.2 DEVICE FABRICATION

- 4. SUMMARY AND CONCLUSIONS

#### 1. INTRODUCTION

#### 1.1 BACKGROUND

BIPOLAR INTEGRATED CIRCUITS RETAIN SUPERIORITY FOR HIGH

SPEED APPLICATIONS AS DIMENSIONS ARE SCALED DOWN BUT

REQUIRE RELATIVELY COMPLICATED PROCESSING, INCLUDING

THIN EPITAXIAL LAYERS AND BURIED SUBCOLLECTORS

#### 1.2 RESEARCH GOALS

• TO INVESTIGATE AND DEVELOP NEW HIGH SPEED VLSI SIMPLIFIED BIPOLAR INTEGRATED STRUCTURES USING PROCESSING SIMILAR TO MOS TECHNOLOGY

#### 2. SATURATION PROTECTED BIPOLAR TRANSISTORS

- A NOVEL CONCEPT FOR TRANSISTOR FABRICATION

- PROTECTION AGAINST SATURATION BY USING A STATIC INDUCTION

TRANSISTOR (SIT) OR A PNP SUBSTRATE TRANSISTOR AS A CLAMP

- FUNCTION OF THE SATURATION PROTECTION: TO PREVENT THE SWITCHING TRANSISTOR FROM ENTERING INTO A DEEP SATURATION MODE BY LIMITING THE CHARGE STORED IN THE COLLECTOR

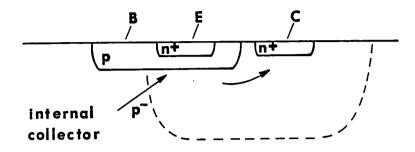

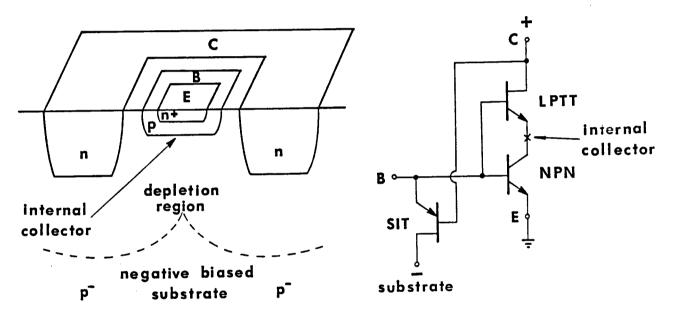

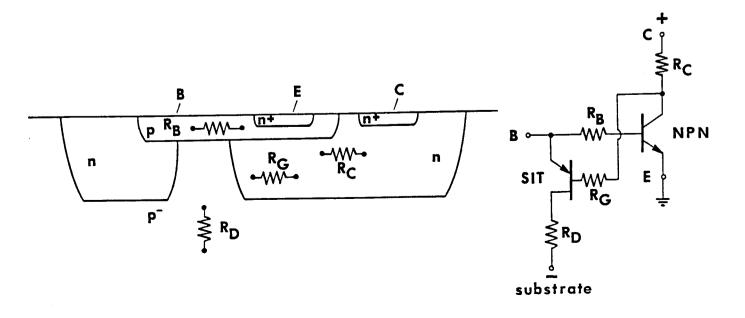

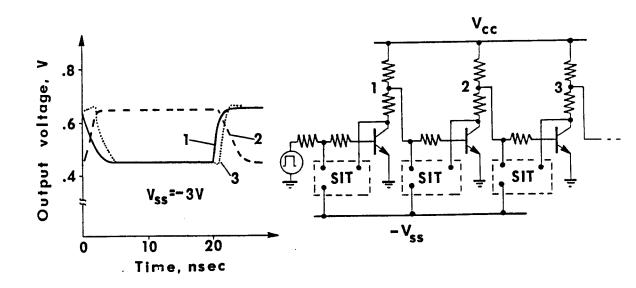

## 2.1 THE SIT SATURATION PROTECTED BIPOLAR TRANSISTOR (SPT/SIT)

- OPERATING PRINCIPLES

- \* A SIMPLIFIED BIPOLAR STRUCTURE FOR VLSI

\* A MODIFIED BIPOLAR STRUCTURE FOR VLSI

A TRIPLE DIFFUSED NPN BIPOLAR TRANSISTOR WITH SIT PROTECTION

- SIMULATION RESULTS

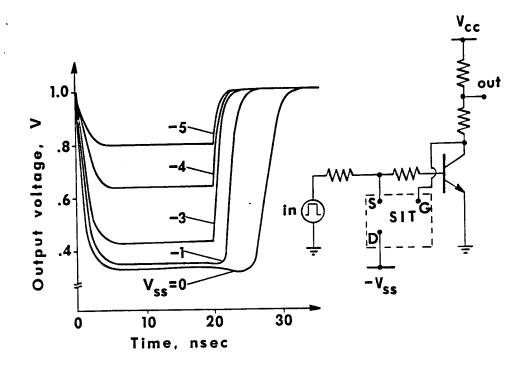

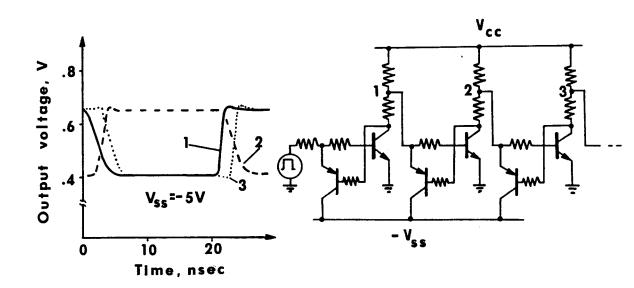

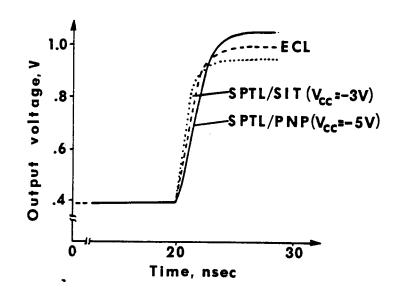

- \* OUTPUT WAVEFORMS FOR A SINGLE STAGE UNLOADED INVERTER WITH AN SIT PROTECTED BIPOLAR TRANSISTOR

\* OUTPUT WAVEFORMS FOR A CHAIN OF INVERTERS WITH SIT PROTECTED BIPOLAR TRANSISTORS

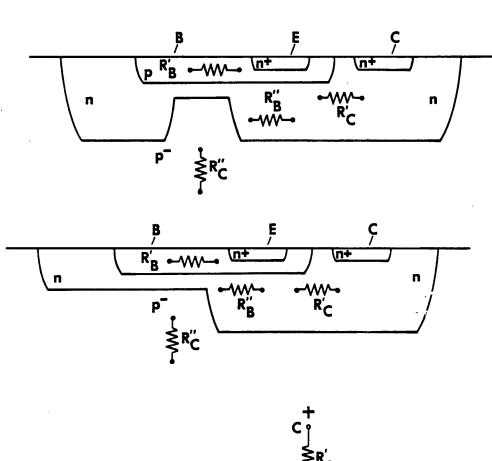

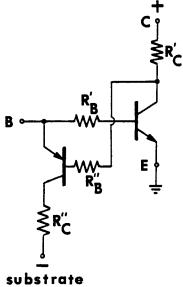

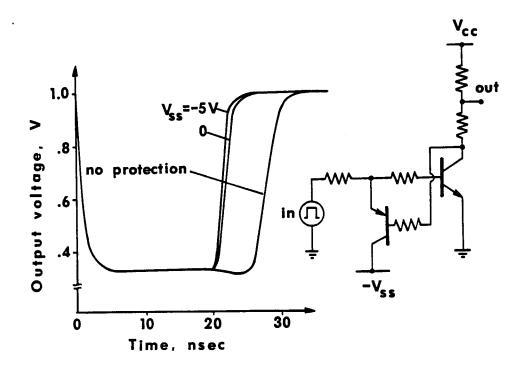

### 2.2 THE PNP SATURATION PROTECTED BIPOLAR TRANSISTOR (SPT/PNP)

- AN ALTERNATIVE APPROACH

- QUADRUPLE DIFFUSED NPN BIPOLAR TRANSISTOR STRUCTURES WITH PNP PROTECTION

- SIMULATION RESULTS

- \* OUTPUT WAVEFORMS FOR A SINGLE-STAGE UNLOADED

INVERTER WITH A PNP PROTECTED BIPOLAR TRANSISTOR

\* OUTPUT WAVEFORMS FOR A CHAIN OF INVERTERS WITH PNP PROTECTED BIPOLAR TRANSISTORS

#### 2.3 CONCLUSIONS

- IMPROVED SWITCHING TIMES FOR SPT/SIT AND SPT/PNP GATES WHEN COMPARED TO SIMILAR GATES WITHOUT PRO-TECTION; CHARGE-STORAGE ELIMINATED

- SPT/SIT: SENSITIVE TO SUBSTRATE BIASING WHICH EFFECTS VOLTAGE SWING AND DELAY TIME

- SPT/PNP: SOMEWHAT INFERIOR TO SPT/SIT IN SPEED

BUT CAN OPERATE WITH ZERO BIAS; PRACTICALLY INSENSITIVE TO SUBSTRATE BIASING

- RTL GATES: PROTECTED BY SIT OR PNP, OPERATE WITH

SPEED OF ECL GATES, BUT WITH SMALLER POWER CONSUMPTION

#### 2.4 DEVICE FABRICATION

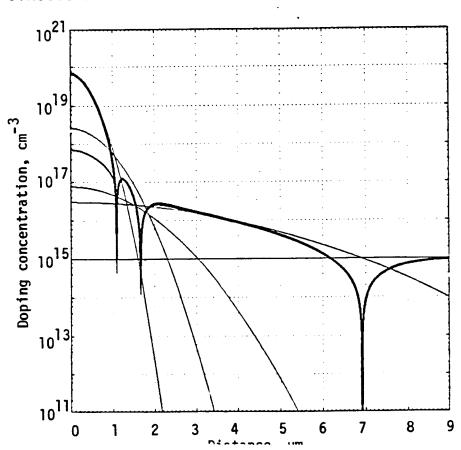

- BITRAS (BIPOLAR TRANSISTOR SIMULATOR);

- \* DEVELOPED TO SUPPORT TECHNOLOGICAL IMPLEMENTATION OF TRIPLE/QUADRUPLE DIFFUSED STRUCTURES;

- \* ALLOWS A PROCESS DESIGNER TO ACCURATELY SIMULATE SILICON FABRICATION TECHNOLOGIES;

- \* COMBINES TECHNOLOGICAL AND ELECTRICAL PARAMETERS OF DEVICES;

- \* PROGRAM INPUT: FABRICATION PARAMETERS SUCH AS TIMES, TEMPERATURES AND DOSES;

- \* PROGRAM OUTPUT: SIMULATED ONE DIMENSIONAL IMPURITY

PROFILE PLOTS, AND DEVICE TECHNOLOGICAL AND ELECTRICAL

PARAMETERS;

- \* EXAMPLE DOPING PROFILES OF A QUADRUPLE DIFFUSED STRUCTURE

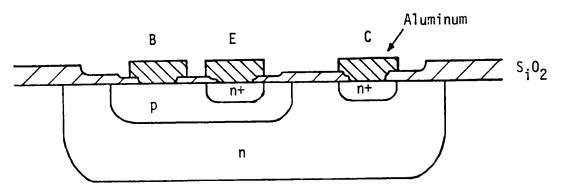

#### THIN BASE TRANSISTORS

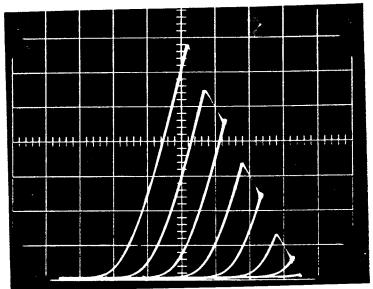

THIN BASE NPN

TRANSISTOR FABRICATED IN 4 µM

TO 6 µM N-WELLS

(WHICH PROVIDE

ISOLATION)

VERT.:

.2MA/DIV

HORIZ.:

1V/DIV

0.001MA/STEP

I-V CHARACTERIS-TICS FOR A TYPI-CAL DEVICE WITH 0.6 µM BASE-EMITTER AND 0.9 µM BASE-COLLECTOR JUNCTIONS

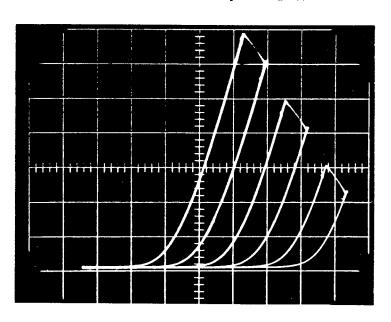

VERT.: 1MA/DIV HORIZ.: 2V/DIV .1MA/STEP I-V CHARACTERISTICS FOR A

SIMILAR DEVICE

(WITH N-TYPE SUBSTRATE INSTEAD

OF N-WELL) PROCESSED WITH A

PHOSPHORUS DOPED

POLISILICON

EMITTER

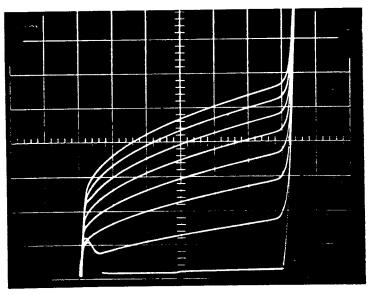

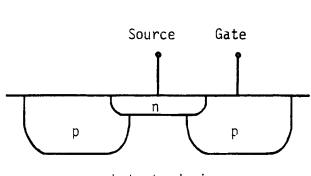

### STATIC INDUCTION TRANSISTOR

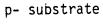

#### \* P-SUBSTRATE

VERT. .2MA/DIV., HORIZ. 1V/DIV 1 MA/STEP, 6  $\mu$ M WINDOW, R = 1  $\kappa\Omega$

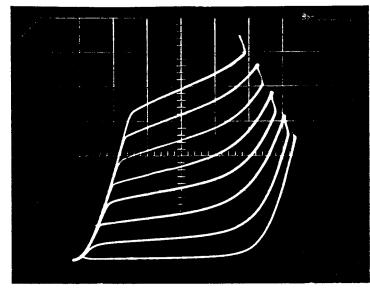

#### \* N-SUBSTRATE

n- substrate drain

VERT. .1MA/DIV., HORIZ. 0.5V/DIV 0.5 MA/STEP, 6  $\mu$ M WINDOW, R = 1  $\kappa\Omega$

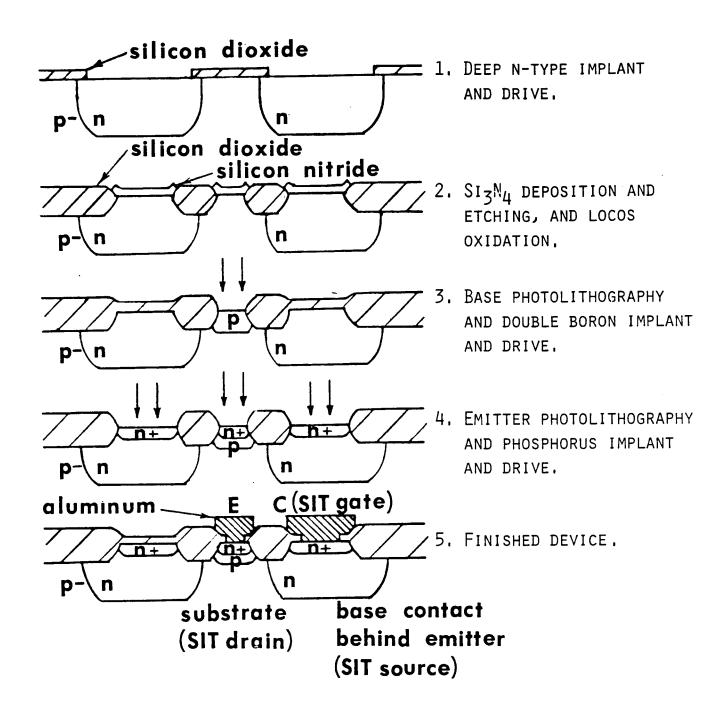

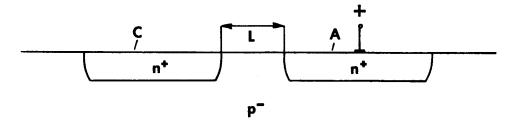

ISOPLANAR PROCESS FOR NPN-BIPOLAR TRANSISTOR WITH S.I.T. PROTECTION AGAINST SATURATION

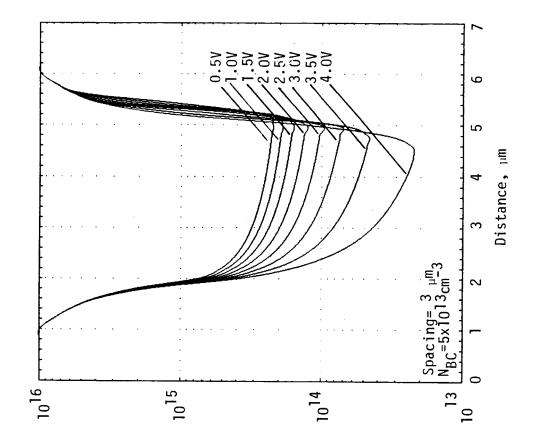

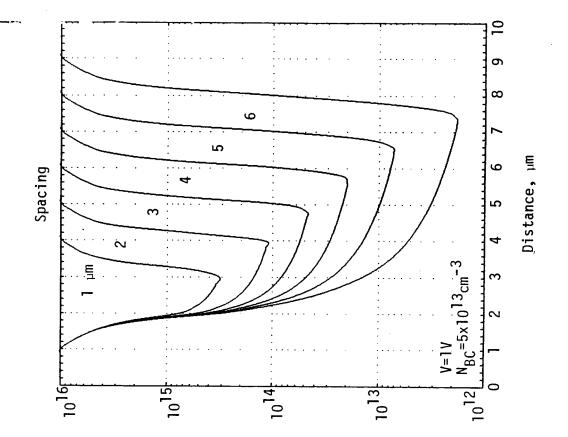

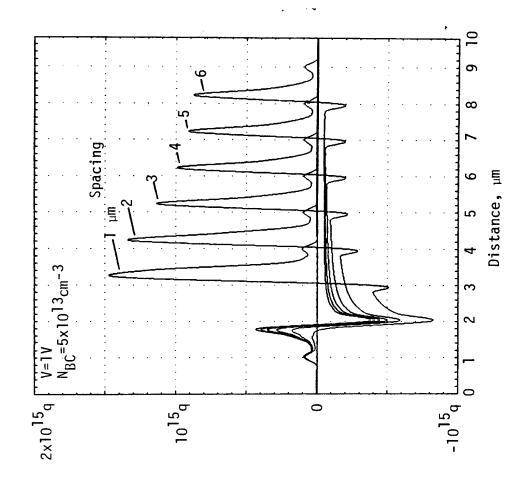

- PUNCH-THROUGH SPACE-CHARGE LIMITED LOADS

- PUNCH-THROUGH AND SPACE-CHARGE PHENOMENA: COMPLICATED IN NATURE, A COMPUTER SIMULATION NECESSARY TO FULLY INVESTIGATE AND UNDERSTAND. THUS A GENERAL ONE-DIMENSIONAL DEVICE PERFORMANCE SIMULATION PROGRAM (GESIM1) WAS DEVELOPED

- \* No simplifying assumptions

- \* SIMULATES STATIC AND DYNAMIC PERFORMANCE

- \* INPUT DATA: IMPURITY CONCENTRATION DISTRIBUTION AND APPLIED TERMINAL VOLTAGE

- \* PROVIDES INFORMATION ABOUT INTERNAL DETAILED TRANSIENT

BEHAVIOR OF SIMULATED DEVICES (POTENTIAL, ELECTRIC

FIELD, CHARGE, HOLES, ELECTRONS, HOLE CURRENT, ELECTRON

CURRENT, RECOMBINATION CURRENT, FERMI POTENTIALS)

- OPERATING PRINCIPLES

- \* A PUNCH-THROUGH SPACE-CHARGE-LIMITED STRUCTURE

Punch-through space-charge limited structures as a REPLACEMENT FOR DIFFUSED RESISTORS

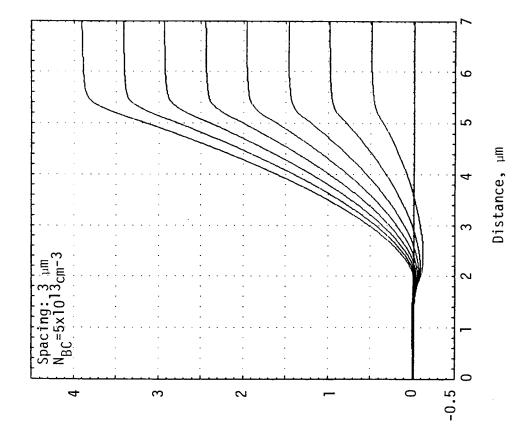

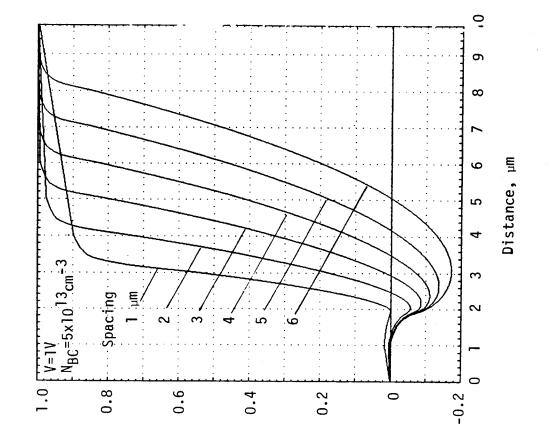

### 3.1 DEVICE SIMULATION

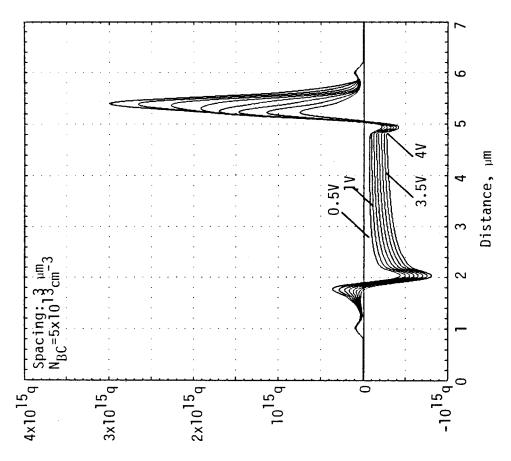

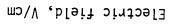

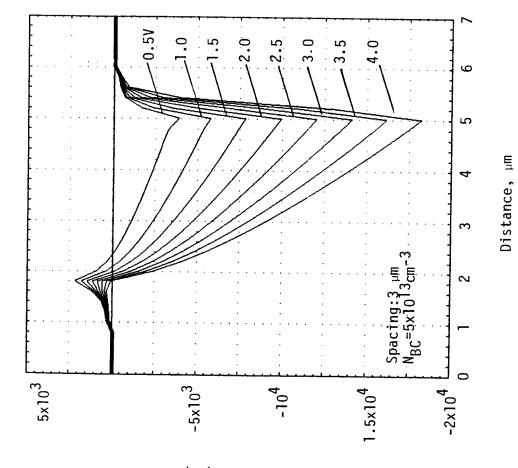

$\epsilon$ -mo , carriers, carriers, concentration of majority

Charge, cm-3

Charge, cm-3

Electric field, V/cm

Potential, V

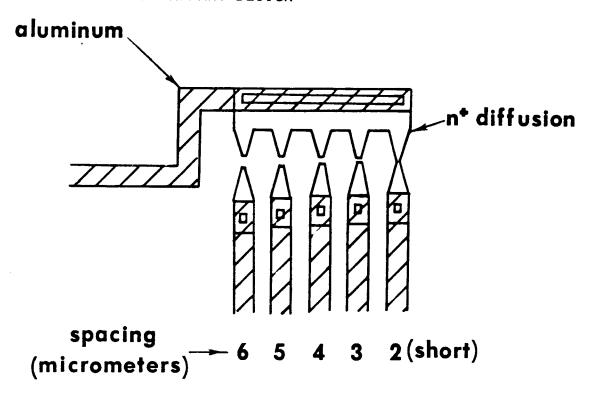

### 3.2 DEVICE FABRICATION

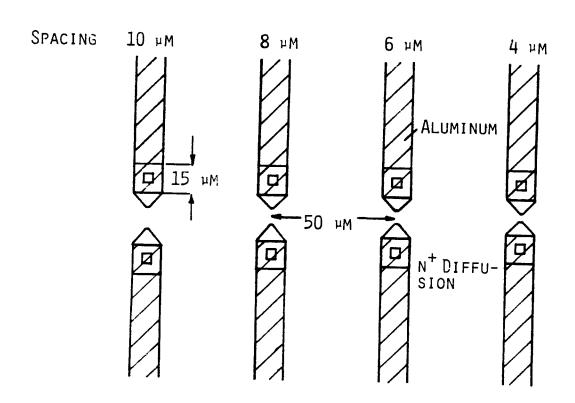

- SPACE-CHARGE LIMITED LOAD TEST STRUCTURES

- \* PRELIMINARY DESIGN

~33 KΩ

HORIZ.: 10V/DIV

VERT.:.5 MA/DIV

6 им

$$N_{\rm BC}$$

=5x10 $^{13}$ cm $^{-3}$

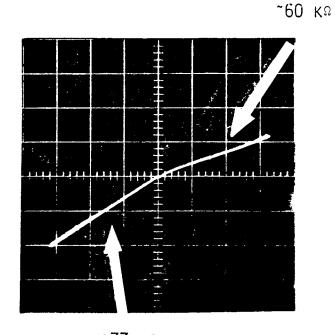

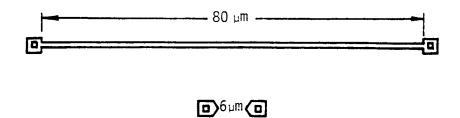

## SPACE-CHARGE LIMITED LOAD TEST STRUCTURES

\* REVISED DESIGN

**4** μM

$N_{\rm BC}^{=6.5 \times 10^{13} \rm cm^{-3}}$

HORIZ.: 5V/DIV

VERT.: .1MA/DIV

R ~105 κΩ

**EXAMPLE**

| SPACE-CHARGE LIMITED | RESISTANCE VALUE |

|----------------------|------------------|

| LOAD SPACING (µM)    | ( <b>Κ</b> υ)    |

| 10                   | ~140             |

| 8                    | ~125             |

| 6                    | ~120             |

| 4                    | ~105             |

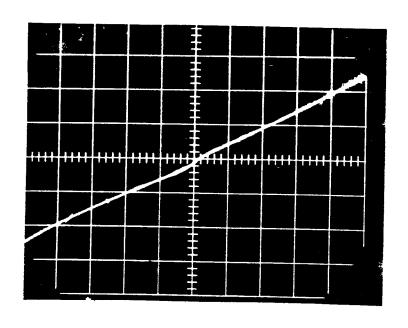

COMPARISON OF A 120.K $\Omega$  SPACE-CHARGE LIMITED LOAD WITH A 120.K $\Omega$  Dogbone resistor using 1  $\mu$ M geometries. An 80. $\Omega$ / $\square$  (EMITTER) PHOSPHORUS DOPED REGION DEFINES THE SCLL. A 1.5  $K\Omega$ / $\square$  (Base) Boron Doped Region Defines the Dogbone Resistor. The substrate sheet resistance is 4. $K\Omega$ / $\square$  (6.5x10 $^{13}$ c $^{3}$  impurity concentration). Besides reduced thip area, the SCLL also has LESS SIDEWALL CAPACITANCE.

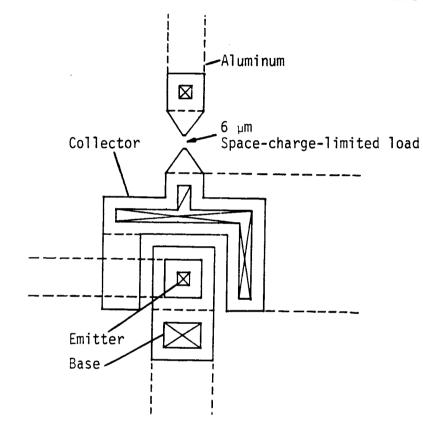

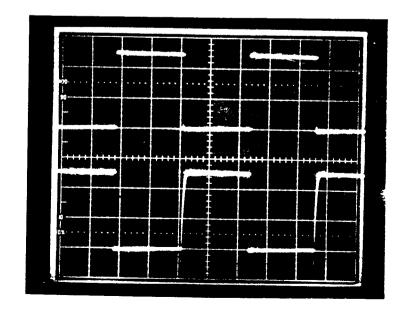

A SIMPLE INVERTER UTILIZING A SPACE-CHARGE-LIMITED LOAD WAS FABRICATED WITH THE LAYOUT SHOWN IN FIGURE A ON A P-TYPE SUBSTRATE (WITH 6.5x10<sup>13</sup>cm<sup>-3</sup> impurity concentration). Figure B shows the input 1.kHz square wave (upper trace) and the inverted output (lower trace) with no protection against saturation of the transistor. There were no adverse effects noted from the substitution of the space-charge-limited load in place of a conventional resistive load.

VERT.: 2.V/DIV

HORIZ:: .2MSEC/DIV

В

Α

#### 4. SUMMARY AND CONCLUSIONS

- A NOVEL CONCEPT FOR TRANSISTOR FABRICATION WAS INVENTED, INTRODUCING AN IDEA FOR PROTECTION AGAINST SATURATION. IT INVOLVES THE USE OF A STATIC INDUCTION TRANSISTOR OR A PNP SUBSTRATE TRANSISTOR AND WAS DEVELOPED BASED ON TRANSISTORS DESIGNED FOR A TRIPLE/QUADRUPLE DIFFUSION FABRICATION TECHNIQUE. SIMULATION SHOWED FASTER SWITCHING TIMES WHEN COMPARED TO SIMILAR GATES WITHOUT PROTECTION AND OPERATION COMPARABLE TO SPEED OF ECL GATES BUT WITH SMALLER POWER CONSUMPTION. FABRICATION OF SIT AND PNP SATURATION PROTECTED NPN BIPOLAR TRANSISTORS IS IN PROGRESS.

- PUNCH-THROUGH SPACE-CHARGE-LIMITED LOADS HAVE BEEN INVESTIGATED AND FABRICATED. RESISTANCES UP TO 150 KΩ ON THE AREA LIMITED PRIMARILY BY THE CONTACTS WERE OBTAINED.

- Two computer programs as research tools were developed:

- A GENERAL ONE-DIMENSIONAL SEMICONDUCTOR DEVICE

PERFORMANCE SIMULATION PROGRAM

- BIPOLAR TRANSISTOR SIMULATOR PROGRAM