## INTERNATIONAL WORKSHOP ON THE PHYSICS OF SEMICONDUCTOR DEVICES

(November 23 - 28, 1981)

ABSTRACTS

SOLID STATE PHYSICS LABORATORY DELHI—110007, INDIA.

Lateral base transistor logic for I<sup>2</sup>L.

## B M WILAMOWSKI and D LEWANDOWSKI

Institute of Electronic Technology, Technical University of Gdańsk, 80-952 Gdańsk, POLAND.

Up to now the best TxP product in I2L family has been obtained in SIT Logic technique. The published results using standard 5 µm photolitography process is 0.002 pJ /1/ /2/. The structure of SITL gate is presented in fig. 1. In this logic the carriers are injected through the potential barrier which is induced in the epi-layer between two p-regions by built-in field of the p-n junction. SITL gates can operate only if separation of the p - type region is below 3 µm and impurity doping level of the epi--layer is below 10<sup>14</sup>cm<sup>-3</sup>. This paper shows that similar results can be obtained using the lateral base transistor /LBT/ /3/ logic fig 2. In this case high gain of the npn transistor is possible due to very low doping level in the lateral diffused base and because the built-in field in the base region. which hampers the carrier flow, practically does not exist. The LBT logic can operate both with low and high doping levels of epi-layer.

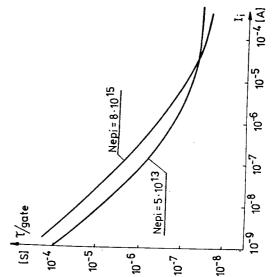

For preparation of the sample, standard bipolar technology was used. Only the doping level of the epi-layer was varried. In case of N  $_{\rm epi}$  =5·10<sup>13</sup>cm<sup>-3</sup>, th TxP product of 0.090 pJ for I  $_{\rm D}<$ 0.1  $\mu{\rm A}$  was obtained and T  $_{\rm min}$  for I  $_{\rm D}$ =250  $\mu{\rm A}$  was 25 ns. This logic could operate even if the doping level of the epi-layer was changed to the value of 8·10<sup>15</sup>cm<sup>-3</sup>. In this case TxP=0.15 pJ for I  $_{\rm D}<$ 1.0  $\mu{\rm A}$  and T  $_{\rm min}$ =20 ns. The results are presented in fig 3. In conclusion one can find that the results in LBT logic are almost as good as in SIT logic with the technological process relatively simple.

## References

- 1. Nishizawa J, Wilamowski B., Int Conf. Solid State Devices Tokyo, Japan, 1976, Jap. J. Applied Physics vol 16.1, pp. 151-154.

- 2. Nishizawa J, Wilamowski B., Int. Solid State Circui Conf. Philadelphia, USA, 1977, pp. 222-223.

- Lewandowski D. Wilamowski B., 2-nd Int.Conf. on Michroelectronics. Toruń, Poland, 1980, pp. 159-16

n+

N+

Fig. 2 LBT Logic gate

a function of injector curren

214

Logic gate