# Test and Diagnosis of Analog Circuits using Moment Generating Functions

Suraj Sindia\*, Vishwani D. Agrawal<sup>†</sup>

Department of Electrical and Computer Engineering

Auburn University, Alabama, AL 36849, USA

\*Email: szs0063@auburn.edu, vagrawal@eng.auburn.edu

Virendra Singh Supercomputer Education and Research Centre Indian Institute of Science, Bangalore 560012, India Email: viren@serc.iisc.ernet.in

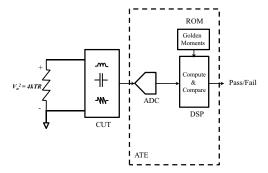

Abstract—The function of a circuit under test (CUT) is represented as a transformation on the probability density function of its input excitation, which is a continuous random variable (RV) with Gaussian probability distribution. Probability moments of the output, now a transformed RV, are used as metrics for testing catastrophic and parametric faults in circuit components. The proposed use of probability moments as test metrics with white noise excitation as input addresses three important problems of analog circuit test, namely, it 1) reduces complexity of input signal design, 2) increases resolution of fault detection, and 3) reduces production test cost as it has no area overhead and may even marginally reduce the test time. We also propose a method to diagnose circuit elements with catastrophic faults based on unique relationships between specific moments of the output and circuit elements. We present a theoretical framework, test and diagnosis procedures and SPICE simulation results for a benchmark elliptic filter and a low noise amplifier. We are able to detect all catastrophic faults and single components that deviate from their nominal values by just over 10%. We diagnose all catastrophic faults in the example circuits.

#### I. INTRODUCTION

Defects in analog integrated circuits can be classified into two important categories, namely, catastrophic faults (open or shorted components) and parametric faults (fractional deviations of circuit components from their nominal values). While extensive literature [1], [2], [3], [4], [5], [6], [7], [8] exists on test schemes for detecting catastrophic (open/short) faults, testing of parametric faults has not received similar attention [9], [10], [11], [12]. The main reason for this disparity is that catastrophic faults tend to upset the supply current drawn by the circuit or the output voltage by a reasonably large factor and any test scheme based on their observation can conveniently uncover them. Some parametric faults have little impact on supply current and are easily masked by measurement noise or general insensitivity of the output to circuit parameter unless they are tested by careful designed input signal targeting their excitation [13]. Different methods have been proposed to test parametric faults in analog circuits including the use of neural networks [14], [15], [16], [17], [18], spectral analysis [19], [20], transfer function coefficient based testing [21] or, more recently, polynomial coefficient based testing [22], [23]. IDDQ measurement needs a sizable deviation in a circuit component value from its nominal value to be useful [24]. Some test methods require extra die area for testing or call for specific input signal excitation and increased test time [25] (as is the case in neural networks based test methods). While some of these problems are addressed in polynomial based test [22], [23], it is still in its early stages and the correct choices of order and frequency of test points are critical for good fault coverage

Thus, we have a need for a production test, that has little additional hardware, reduced test application time and minimized complexity of input signal design. To respond

to the last question we ask, 'What is the easiest available signal that needs little or no design effort?' Without doubt, it is white noise, always available as random voltage fluctuations across an R  $\Omega$  resistor due to thermally agitated electrons. Power spectral density of this white noise is given by  $|S_N(f)| = 4kTR |\operatorname{volt}^2/\operatorname{Hz}|$ , where k is the Boltzmann constant and T is temperature in Kelvin. Previously [26] white noise has been used as an excitation signal for testing circuits, and the output Fourier spectrum is used for ensuring the circuit conforms to specification. However, in this work, to leverage a random signal like white noise which is characterized only by its statistics such as mean, variance, third and higher order moments, we compute probability moments at the output to be able to derive information on deviation in circuit parameters. Reference [27] proposes the use of a pseudo random noise source as the input and higher order statistics with Volterra kernel at the output as a signature for characterizing the CUT as good or faulty. Work presented in this paper is different on three counts from previous work, 1) we use a truly random noise source as input, namely, thermal noise from a resistor; though pseudo random noise source will work equally well, 2) higher order moments with an exponentially sensitive random variable transformation is used at the output instead of Volterra kernel. Such a transformation gives better fault resolution for parametric faults than Volterra kernel as shown by our simulation of the elliptic filter example, those results are not included here, 3) we demonstrate fault diagnosis in addition to testing while the earlier work discussed only testing. We view the circuit as a communication channel [28], [29], [30] that transforms the probability density function of the input signal as it propagates through the channel (circuit). The output, which is now the transformed random variable (RV) has its signature moments that are used for testing the CUT for both catastrophic and parametric faults. We show in this paper that probability moments can be made exponentially sensitive [31], [32] to circuit parameters, so that parametric faults of 10% and over result in sufficient excursions of the output probability moments to uncover these faults. In the sequel, we describe our scheme on a cascaded amplifier and a low pass filter. We then evaluate the performance of probability moments in conjunction with an exponential RV transformation to enhance sensitivity for fault detection on a benchmark elliptic filter.

In this paper, Section II develops the background on moment theory and random variable transformation, and defines a minimum size detectable fault. The problem at hand and our approach is described with examples in Section III. In Section IV, we generalize the method to arbitrarily large circuits. We report experimental results on benchmark elliptic filter in Section V. Section VI introduces fault diagnosis procedure that leverages on unique relationships between moments and

circuit components, and Section VII reports results of a fault diagnosis experiment using moments of output of a low noise amplifier. We conclude in Section VIII.

#### II. BACKGROUND

We briefly review the moment method to characterize a random variable (RV) (refer [33] for more details). We then give a transformation of RV to increase the sensitivity of moments to circuit parameters.

#### A. Moment Generating Functions

The  $j^{th}$  moment  $\forall j=2\cdots N$  of a continuous time RV  $X\left(t\right)$ , sampled at time instants t=kT, and denoted by  $X_{k}$ where  $k = 0, 1 \cdots \infty$  is given by

$$\mu_j = \sum_{k=0}^{\infty} (X_k - \mu_1)^j p(X_k)$$

(1)

Moment generating function M(s) of such a discrete RV  $X_k$ , serves as a convenient expression from which different orders of moments  $\mu_i$  may be computed using the following relation:

$$\mu_j = \left. \frac{d^j M(s)}{ds^j} \right|_{s=0} \tag{2}$$

where

$$M(s)$$

is given by

$$M(s) = E\left(e^{sX_k}\right) = \sum_{k=0}^{\infty} e^{sX_k} p\left(X_k\right) \tag{3}$$

## B. Random Variable Transformation

We require an RV transformation [34] that can narrowly track small changes. We look for a transformation with following properties:

- 1) It increases the sensitivity of output function for small changes in the input.

- 2) It increases absolute values of the first and higher order moments of the output.

Let X be a RV whose domain is  $\mathbb{R}$ . We define a transformation f(X) mapping X from  $\mathbb{R} \Longrightarrow \mathbb{R}$  as follows:

$$f(X) = Xe^{\alpha X - \frac{\beta}{X}} \tag{4}$$

where  $\alpha$ ,  $\beta \ge 0$  are parameters of the transformation. It can be shown that transformation f(X) always gives second and higher order moments which are such that

$$\log_e |\mu_j|_{f(X)} \ge \log_e |\mu_j| \, \forall j = 2, 3, \cdots N$$

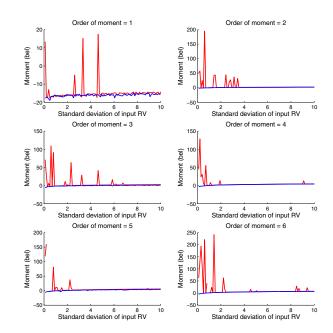

We plot the first six moments of the transformed RV, with  $\alpha = 0.01, \beta = 0.001$  against standard deviation of input RV in 1, which shows that the moments of the transformed RV is always greater than that of the RV without transformation. At a few input standard deviations, transformed RV can have significantly higher moments compared to moments without transformation (Notice that the Y-axis in the plots are in the logarithmic scale). This makes the transformation defined in equation 4 very amenable for use as a post processing RV transformation at the output of the CUT. Even for small changes in the input, the resulting moments can be significantly different. The sensitivity of the transformed RV to the input RV is given by

$$S_X^f = \frac{X}{f} \frac{\partial f}{\partial X} = 1 + \alpha X + \frac{\beta}{X} \tag{5}$$

By appropriate choice of  $\alpha$  and  $\beta$ , based on dynamic range of X, we can increase the sensitivity of f(X) for both small and large variations of X.

Moments of different orders as functions of input noise power (standard deviation of input RV) with (in red/dashed) and without (in blue/solid) RV transformation for first order RC filter. See Figure 2.

### C. Minimum Size Detectable Fault

Definition: Minimum size detectable fault (MSDF) of a circuit parameter is defined as the minimum fractional deviation in the circuit parameter from its nominal value for it to be detectable with all other circuit parameters held at their nominal values. The fractional deviation  $\rho$  can be positive or negative and is named upside-MSDF (UMSDF) or downside-MSDF (DMSDF) accordingly. This definition of minimum size detectable fault is general, regardless of the test technique used to uncover faults. In the context of the test technique described in this paper, we define MSDF based on moments of the probability density function of the circuit output. Suppose  $p_i$ , where  $i = 1 \cdots K$  is the nominal value of ith circuit parameter with a fault free tolerance range of  $p_i(1 \pm \gamma)$ , and  $\overline{\mu_j}$ , where  $j = 1 \cdots N$  is the  $j^{th}$ fault-free probability moment of the circuit output. Then the UMSDF (DMSDF),  $\hat{\rho}_i$  ( $\check{\rho}_i$ ) of circuit parameter  $p_i$  is given by a minimum value x, such that  $p_i(1 \pm x)$  puts at least one of the moments  $\overline{\mu_j}$  outside the fault free hypersphere  $|\overline{\mu_j} - \mu_j| \le \mu_0$ , where  $\mu_0$  is the permitted deviation in moments when the circuit parameters are allowed excursions within their tolerance range. As specified earlier, this range is characterized by a tolerance factor  $\gamma$ .

#### III. PROBLEM AND APPROACH

We first illustrate with an example the calculation of limits of the probability moments of a first order low pass filter. We follow this up with calculation of MSDF values of the circuit parameters. We then consider a two stage cascade amplifier.

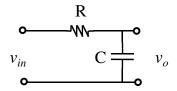

Example 1. First order RC filter: With white noise as the input, the discrete values are sampled Gaussian RV of zero mean and variance,  $\sigma_{in}^2 = \frac{N_o}{2}$ . The fault-free filtered response has a variance (also the second order moment)  $\overline{\mu}_2 = \frac{N_o \pi}{4RC}$ . Details of this calculation are shown in the appendix. However, if there is a presentation fault of size  $\pi$  in the size of the second order. if there is a parametric fault of size x in the circuit parameter R, then the new output variance is given by  $\mu_2 = \frac{N_o \pi}{4R(1+x)C}$ .

Fig. 2. First-order RC filter.

Fig. 3. A cascade amplifier.

If the circuit specifications can tolerate a moment deviation of  $\mu_0$ , then the MSDF of R is given by the minimum value of x that violates  $\overline{\mu}_2 - \mu_2 \leq \mu_0$ . For the example in question, since we consider only the second order moment, the MSDF in R, denoted by  $\rho_R$  is given by

$$\rho_R = \frac{4\mu_0 CR}{N_o \pi - 4\mu_0 CR} \tag{6}$$

Similarly MSDF of capacitor C,  $\rho_C$  can be found and by symmetry it is equal to  $\rho_R$ .

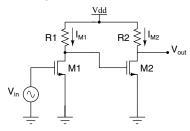

Example 2. Two stage amplifier: Consider the cascade amplifier shown in Figure 3. The output voltage  $V_{out}$  in terms of input voltage results in a fourth degree polynomial:

$$v_{out} = a_0 + a_1 v_{in} + a_2 v_{in}^2 + a_3 v_{in}^3 + a_4 v_{in}^4$$

(7)

where constants  $a_0, a_1, a_2, a_3$  are defined symbolically in (8) for transistors M1 and M2 operating in the saturation region.

$$a_{0}\left(R_{1},R_{2}\right) = V_{DD} - R_{2}K\left(\frac{W}{L}\right)_{2} \left\{ \begin{array}{l} \left(V_{DD} - V_{T}\right)^{2} + \\ R_{1}^{2}K^{2}\left(\frac{W}{L}\right)_{1}^{2}V_{1}^{4} - \\ 2\left(V_{DD} - V_{T}\right)R_{1}\left(\frac{W}{L}\right)_{1}V_{T}^{2} \end{array} \right\}$$

$$a_{1}\left(R_{1},R_{2}\right) = R_{2}K\left(\frac{W}{L}\right)_{2} \left\{ \begin{array}{l} 4R_{1}^{2}K^{2}\left(\frac{W}{L}\right)_{1}^{2}V_{T}^{3} \\ +2\left(V_{DD} - V_{T}\right)R_{1}K\left(\frac{W}{L}\right)_{1}V_{T} \end{array} \right\}$$

$$a_{2}\left(R_{1},R_{2}\right) = R_{2}K\left(\frac{W}{L}\right)_{2} \left\{ \begin{array}{l} 2\left(V_{DD} - V_{T}\right)R_{1}K\left(\frac{W}{L}\right)_{1}V_{T} \\ -6R_{1}^{2}K^{2}\left(\frac{W}{L}\right)_{1}^{2}V_{T}^{2} \end{array} \right\}$$

$$a_{3}\left(R_{1},R_{2}\right) = 4V_{T}K^{3}\left(\frac{W}{L}\right)_{1}^{2}\left(\frac{W}{L}\right)_{2}^{2}R_{1}^{2}R_{2}$$

$$a_{4}\left(R_{1},R_{2}\right) = -K^{3}\left(\frac{W}{L}\right)_{1}^{2}\left(\frac{W}{L}\right)_{2}^{2}R_{1}^{2}R_{2}$$

$$\left(R_{1},R_{2}\right) = -K^{3}\left(\frac{W}{L}\right)_{1}^{2}\left(\frac{W}{L}\right)_{2}^{2}R_{1}^{2}R_{2}$$

If the cascade amplifier is excited with white noise at its input, the fault free output can be a estimated as a random variable with its first order moment, namely, mean  $\overline{\mu_1}$  given by

$$\overline{\mu_1} = E\left\{a_0 + a_1 v_{in} + a_2 v_{in}^2 + a_3 v_{in}^3 + a_4 v_{in}^4\right\}$$

(9)

$$= a_0 + a_1 \mu_{1,in} + a_2 \mu_{2,in} + a_3 \mu_{3,in} + a_4 \mu_{4,in}$$

(10)

To find MSDF in  $R_1$ , let us assume we have a fractional deviation x in  $R_1$  and the other circuit parameters are at their fault free values. If  $\mu_0$  is the tolerable fractional deviation in the first order moment at the output, the minimum value of x that satisfies the following inequality is the MSDF of parameter  $R_1$ :

TABLE I MSDF for cascade amplifier of Figure 3 with  $\mu_0=0.05$ .

| Circuit parameter       | %upside<br>MSDF | %downside<br>MSDF |

|-------------------------|-----------------|-------------------|

| Resistor R <sub>1</sub> | 7               | 8                 |

| Resistor R <sub>2</sub> | 10.5            | 7.5               |

$$\left\{

\begin{array}{l}

a_{0}\left(R_{1}\left(1+x\right), R_{2}\right) \\

+a_{1}\left(R_{1}\left(1+x\right), R_{2}\right) \mu_{1,in} \\

+a_{2}\left(R_{1}\left(1+x\right), R_{2}\right) \mu_{2,in} \\

+a_{3}\left(R_{1}\left(1+x\right), R_{2}\right) \mu_{3,in} \\

+a_{4}\left(R_{1}\left(1+x\right), R_{2}\right) \mu_{4,in}

\end{array}\right\} - \overline{\mu_{1}} \geq \mu_{0} \tag{11}$$

Maximizing x, while meeting the constraint in equation 11 gives MSDF of  $R_1$  as

$$\rho_{R_1} = \frac{\mu_0}{a_0 + a_1 \mu_{1,in} + a_2 \mu_{2,in} + a_3 \mu_{3,in} + a_4 \mu_{4,in}}$$

(12)

Similarly MSDF of  $R_2$  can be evaluated. Table I gives the MSDF for  $R_1$  and  $R_2$  based on the above calculation. Nominal values of  $V_{DD}=1.2V,\ V_T=400mV,\ \left(\frac{W}{L}\right)_1=\frac{1}{2}\left(\frac{W}{L}\right)_2=20,$  and  $K=100\mu A/V^2$  are used for this example.

#### IV. GENERALIZATION

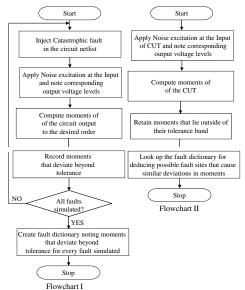

The computation of MSDF in the previous section is too complex for large circuits. As shown in Figure 4 a complex circuit having more than 20 components is supplied the input noise voltage (derived from a resistor maintained at desired temperature). The output of the circuit is then passed through a suitable RV transformation function like the one given by equation 4. Probability density function (PDF) of the output of this RV transformation is estimated using the histogram spread of the output voltage values. Next,  $N^{th}$  order moments (orders up to N=6 are sufficient for most analog circuits having component count of  $\leq 40$ ) are found using the moment generating function defined in equation 3. The  $j^{th}$  derivatives w.r.t. s required for  $j^{th}$  order moments are found as finite differences about s=0. Once the fault free values of all N moments are available, single parametric faults are injected into the circuit and the corresponding deviation in one or more moments are noted. Based on the moment deviations that can be tolerated, the fault size injected is steadily increased. The minimum fault size of any circuit parameter that causes at least one of the moments to just fall outside of its tolerance band (also called the fault-free hypersphere) gives the MSDF of that circuit parameter. In Figure 5, Flowchart I summarizes the process of numerically finding the probability moments and their bounds and Flowchart II in Figure 5 outlines a procedure to test CUT using the PDF moments. The bounds on moments of fault free circuit are found a priori in Flowchart I.

## V. FAULT DETECTION IN ELLIPTIC FILTER

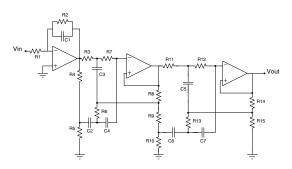

We simulated an elliptic filter shown in Figure 6 according to the test scheme of Figure 5. The circuit parameter values are as in the benchmark maintained by Stroud et al. [35]. Thermal noise from resistors  $R=40G\Omega,60G\Omega,80G\Omega,100G\Omega$  was used at T=300K. On application of RV transformation, signal levels (and so are moments) significantly better resolved as compared to that without RV transformation. For example, the six fault free moments of the elliptic filter before transformation (for  $R=40G\Omega)$  are as follows:  $\overline{\mu_1}=4.53453,$   $\overline{\mu_2}=0.03234,$   $\overline{\mu_3}=0.02345,$   $\overline{\mu_4}=0.01125,$   $\overline{\mu_5}=0.009325,$   $\overline{\mu_6}=0.00623125.$  After RV transformation, the fault free

Fig. 4. Block diagram of a system with CUT using white noise excitation.

Fig. 5. Fault simulation process and bounding of moments (Flowchart I), and the complete test procedure (Flowchart II).

moments are given by  $\overline{\mu_1}=338.6453,\ \overline{\mu_2}=1.8234,\ \overline{\mu_3}=0.9254,\ \overline{\mu_4}=0.8812,\ \overline{\mu_5}=0.6365,\ \overline{\mu_6}=0.1638125.$  Combinations of parameter values leading to limits on the coefficients are as shown in Tables II and III. Results on pass/fail detectability of few injected faults are tabulated in Table IV.

Fig. 6. Elliptic filter.

TABLE II PARAMETER COMBINATIONS LEADING TO MAXIMUM VALUES OF MOMENTS WITH DEVICE TOLERANCE  $\gamma=0.05$  in elliptic filter.

| Circuit          |         |         |         |         | 1       |         |

|------------------|---------|---------|---------|---------|---------|---------|

|                  | $\mu_1$ | $\mu_2$ | $\mu_3$ | $\mu_4$ | $\mu_5$ | $\mu_6$ |

| Parameter        |         |         |         |         |         |         |

| $(\Omega, nF)$   |         |         |         |         |         |         |

| $R_1 = 19.6k$    | 19.6k   | 20.58k  | 19.6k   | 20.58k  | 20.58k  | 18.62k  |

| $R_2 = 196k$     | 186.2k  | 205.8k  | 205.8k  | 205.8k  | 186.2k  | 186.2k  |

| $R_3 = 147k$     | 139.65k | 147k    | 139.65k | 139.65k | 154.35k | 147k    |

| $R_4 = 1k$       | 1050    | 1050    | 950     | 1000    | 1050    | 950     |

| $R_5 = 71.5$     | 75.075  | 67.925  | 75.075  | 71.5    | 75.075  | 67.925  |

| $R_6 = 37.4k$    | 37.4k   | 37.4k   | 37.4k   | 39.27k  | 39.27k  | 37.4k   |

| $R_7 = 154k$     | 154k    | 154k    | 154k    | 146.3k  | 154k    | 154k    |

| $R_8 = 260$      | 260     | 260     | 260     | 260     | 273     | 273     |

| $R_9 = 740$      | 703     | 777     | 777     | 703     | 777     | 777     |

| $R_{10} = 500$   | 500     | 500     | 475     | 475     | 525     | 500     |

| $R_{11} = 110k$  | 115.5k  | 104.5k  | 104.5k  | 104.5k  | 104.5k  | 110k    |

| $R_{12} = 110k$  | 115.5k  | 104.5k  | 104.5k  | 110k    | 110k    | 115.5k  |

| $R_{13} = 27.4k$ | 28.77k  | 26.03k  | 26.03k  | 26.03k  | 27.4k   | 26.03k  |

| $R_{14} = 40$    | 40      | 40      | 38      | 40      | 40      | 40      |

| $R_{15} = 960$   | 912     | 1008    | 912     | 960     | 912     | 960     |

| $C_1 = 2.67$     | 2.8035  | 2.5365  | 2.67    | 2.67    | 2.67    | 2.5365  |

| $C_2 = 2.67$     | 2.8035  | 2.67    | 2.8035  | 2.8035  | 2.5365  | 2.67    |

| $C_3 = 2.67$     | 2.8035  | 2.8035  | 2.67    | 2.5365  | 2.5365  | 2.5365  |

| $C_4 = 2.67$     | 2.8035  | 2.67    | 2.5365  | 2.67    | 2.5365  | 2.67    |

| $C_5 = 2.67$     | 2.8035  | 2.67    | 2.8035  | 2.5365  | 2.5365  | 2.67    |

| $C_6 = 2.67$     | 2.8035  | 2.5365  | 2.8035  | 2.5365  | 2.67    | 2.8035  |

| $C_7 = 2.67$     | 2.67    | 2.5365  | 2.8035  | 2.8035  | 2.67    | 2.5365  |

#### VI. FAULT DIAGNOSIS

Flowchart I in Figure 7 describes fault simulation and creation of a fault dictionary. Every probability moment of the output is a function of one or more circuit elements. Conversely, we can find one or more moments that are functions of a particular circuit element. By simulating all catastrophic faults in the circuit, we can find those moments that are displaced out of their fault-free ranges for each of the fault and create a fault dictionary. The fault dictionary consists of a list of all catastrophic faults and the corresponding moments that are displaced. Next, using the single catastrophic fault assumption we can compute all the moments of the CUT. Depending on moments that lie outside their fault-free range an estimation of the circuit parameter that has a catastrophic fault is found. Now based on the moments that are displaced from their fault-free value, we can locate the fault in the CUT. Flowchart II in Figure 7 gives the diagnosis procedure.

TABLE III PARAMETER COMBINATIONS LEADING TO MINIMUM VALUES OF MOMENTS WITH DEVICE TOLERANCE  $\gamma=0.05$  in elliptic filter.

| Circuit          | $\mu_1$ | $\mu_2$ | $\mu_3$ | $\mu_4$ | $\mu_5$ | $\mu_6$ |

|------------------|---------|---------|---------|---------|---------|---------|

| Parameter        | $\mu_1$ | μ2      | μ3      | $\mu_4$ | $\mu_5$ | $\mu_0$ |

| $(\Omega, nF)$   |         |         |         |         |         |         |

|                  | 10.61   | 10.631  | 10.0    | 10.61   | 10.61   | 20.501  |

| $R_1 = 19.6k$    | 19.6k   | 18.62k  | 19.6k   | 19.6k   | 19.6k   | 20.58k  |

| $R_2 = 196k$     | 205.8k  | 205.8k  | 205.8k  | 196k    | 186.2k  | 205.8k  |

| $R_3 = 147k$     | 147k    | 154.35k | 154.35k | 139.65k | 154.35k | 154.35k |

| $R_4 = 1k$       | 950     | 1000    | 1050    | 950     | 1050    | 950     |

| $R_5 = 71.5$     | 67.925  | 71.5    | 75.075  | 75.075  | 67.925  | 71.5    |

| $R_6 = 37.4k$    | 39.27k  | 37.4k   | 35.53k  | 39.27k  | 35.53k  | 35.53k  |

| $R_7 = 154k$     | 146.3k  | 161.7k  | 154k    | 161.7k  | 154k    | 154k    |

| $R_8 = 260$      | 247     | 273     | 247     | 273     | 260     | 247     |

| $R_9 = 740$      | 703     | 777     | 740     | 777     | 777     | 740     |

| $R_{10} = 500$   | 500     | 500     | 475     | 475     | 525     | 475     |

| $R_{11} = 110k$  | 104.5k  | 115.5k  | 115.5k  | 115.5k  | 110k    | 110k    |

| $R_{12} = 110k$  | 115.5k  | 110k    | 115.5k  | 110k    | 104.5k  | 115.5k  |

| $R_{13} = 27.4k$ | 27.4k   | 26.03k  | 27.4k   | 28.77k  | 28.77k  | 26.03k  |

| $R_{14} = 40$    | 42      | 40      | 40      | 38      | 40      | 38      |

| $R_{15} = 960$   | 1008    | 960     | 1008    | 1008    | 912     | 960     |

| $C_1 = 2.67$     | 2.67    | 2.5365  | 2.5365  | 2.67    | 2.5365  | 2.67    |

| $C_2 = 2.67$     | 2.67    | 2.67    | 2.67    | 2.67    | 2.67    | 2.8035  |

| $C_3 = 2.67$     | 2.8035  | 2.8035  | 2.8035  | 2.8035  | 2.5365  | 2.8035  |

| $C_4 = 2.67$     | 2.8035  | 2.8035  | 2.8035  | 2.8035  | 2.8035  | 2.67    |

| $C_5 = 2.67$     | 2.67    | 2.8035  | 2.67    | 2.8035  | 2.8035  | 2.67    |

| $C_6 = 2.67$     | 2.8035  | 2.5365  | 2.8035  | 2.5365  | 2.67    | 2.8035  |

| $C_7 = 2.67$     | 2.67    | 2.5365  | 2.8035  | 2.67    | 2.67    | 2.8035  |

TABLE IV FAULT DETECTION OF SOME INJECTED FAULTS IN ELLIPTIC FILTER.

| Circuit Parameter        | Out of bound moment | Fault detected? |

|--------------------------|---------------------|-----------------|

| R <sub>1</sub> down 12%  | $\mu_3, \ \mu_1$    | Yes             |

| R <sub>2</sub> down 10%  | $\mu_4$             | Yes             |

| R <sub>3</sub> up 12%    | $\mu_1, \; \mu_2$   | Yes             |

| R <sub>4</sub> down 10%  | $\mu_2$             | Yes             |

| R <sub>5</sub> up 10%    | $\mu_4$             | Yes             |

| R <sub>7</sub> up 15%    | $\mu_5, \ \mu_6$    | Yes             |

| R <sub>11</sub> up 15%   | $\mu_3$             | Yes             |

| R <sub>12</sub> down 15% | $\mu_2, \ \mu_6$    | Yes             |

| C <sub>1</sub> up 11%    | $\mu_1, \; \mu_2$   | Yes             |

| C <sub>4</sub> up 12%    | $\mu_4$             | Yes             |

| C <sub>5</sub> down 15%  | $\mu_1, \; \mu_6$   | Yes             |

Fig. 7. Fault simulation and Fault diagnosis procedures summarized.

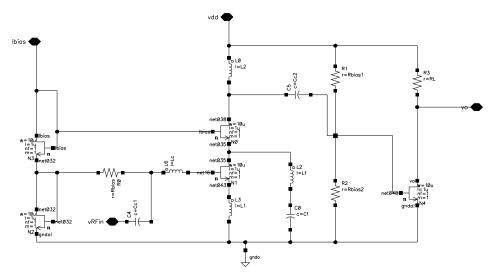

# VII. FAULT DIAGNOSIS IN LOW NOISE AMPLIFIER

We used the low noise amplifier of Figure 8 to evaluate our test procedure. The circuit has 16 components. Thus, there are 32 single catastrophic faults corresponding to opens and shorts of the passive R, L and C elements. For an open fault the element was replaced by a  $1G\Omega$  resistance. For a short fault the element was replaced by a 0V voltage source. For an MOS transistor, the drain and source terminals were short circuited for a short and were left open for an open fault. For these 32 faults to be uniquely identified, we need at least 5 moments. Each fault causes one or more moments to lie outside its tolerance band. The total number of uniquely identifiable fault cases with N moments =  $\sum_{n=1}^{N} \binom{N}{n} = 2^N - 1$ . If two faults displacing the same set of moments will cause a diagnostic ambiguity. Evaluating higher order moments, however, gives better diagnostic resolution, which comes at a price of additional computation. Table V lists faults and the corresponding moments displaced by each fault. We use up to the  $6^{th}$  order moment and observe that out of the 32 faults, only 5 are *not* uniquely diagnosed because they affect identical sets of moments. The number in the last column identifies number of faults displacing the same set of moments. For example, two faults (indicated in the last column) R<sub>bias</sub>-short and  $L_c$ -short displace same set of moments  $\mu_2 - \mu_6$ .

TABLE V

| FAULT DICTIONARY FOR CATASTROPHIC FAULTS IN LINA AMPLIFIER. |          |          |               |          |          |               |          |          |

|-------------------------------------------------------------|----------|----------|---------------|----------|----------|---------------|----------|----------|

| Component                                                   | Nature   | $\mu_1$  | $\mu_2$       | $\mu_3$  | $\mu_4$  | $\mu_5$       | $\mu_6$  | Uniq-    |

|                                                             |          |          |               |          |          |               |          | uely     |

| (ohm, nH, fF)                                               | of fault |          |               |          |          |               |          | Diagn-   |

|                                                             |          |          |               |          |          |               |          | osable ? |

| $R_{bias} = 10$                                             | short    |          | <b>√</b>      | <b>√</b> | <b>√</b> | <b>√</b>      | <b>~</b> | No (2)   |

| $L_C = 1$                                                   | short    |          | <b>√</b>      | <b>√</b> | <b>√</b> | <b>√</b>      | <b>✓</b> | No (2)   |

| $L_1 = 1.5$                                                 | short    | <b>√</b> | $\overline{}$ | <b>√</b> | <b>~</b> | $\overline{}$ | <b>√</b> | Yes      |

| $L_2 = 1.5$                                                 | short    | <b>~</b> |               | <b>√</b> |          | <b>√</b>      | <b>√</b> | Yes      |

| $L_f = 1$                                                   | short    | <b>√</b> | <b>√</b>      | <b>√</b> | <b>√</b> | <b>√</b>      | <b>√</b> | No (3)   |

| $C_{\rm f} = 100$                                           | short    | <b>~</b> | $\overline{}$ |          |          |               | <b>√</b> | Yes      |

| $C_{C2} = 100$                                              | short    | <b>√</b> | <b>√</b>      |          | <b>√</b> | <b>√</b>      | <b>√</b> | Yes      |

| $R_{bias1} = 100k$                                          | short    | <b>√</b> | <b>√</b>      |          | <b>√</b> |               |          | Yes      |

| $R_{\rm bias2} = 100 k$                                     | short    | <b>√</b> |               |          |          |               | <b>√</b> | Yes      |

| $R_{L} = 100k$                                              | short    |          | <b>√</b>      | <b>√</b> |          |               | <b>✓</b> | No (3)   |

| $N_0(D-S)$                                                  | short    | <b>√</b> |               |          |          |               | <b>√</b> | Yes      |

| $N_1(D-S)$                                                  | short    |          | <b>√</b>      |          | <b>√</b> |               |          | Yes      |

| $N_2(D-S)$                                                  | short    | <b>√</b> | <b>√</b>      | <b>√</b> | <b>√</b> | <b>√</b>      |          | Yes      |

| $N_3(D-S)$                                                  | short    | <b>√</b> |               | <b>√</b> | <b>√</b> | <b>√</b>      | <b>√</b> | Yes      |

| $N_4(D-S)$                                                  | short    |          |               |          |          | <b>√</b>      | <b>√</b> | Yes      |

| $R_{bias} = 10$                                             | open     | <b>√</b> | <b>√</b>      | <b>√</b> |          |               |          | Yes      |

| $L_C = 1$                                                   | open     | <b>V</b> | <b>√</b>      |          |          |               |          | Yes      |

| $L_1 = 1.5$                                                 | open     |          |               | <b>√</b> |          | <b>√</b>      | ~        | Yes      |

| $L_2 = 1.5$                                                 | open     | <b>✓</b> | $\overline{}$ |          | <b>√</b> |               | <b>✓</b> | Yes      |

| $L_f = 1$                                                   | open     | <b>~</b> |               | <b>√</b> |          |               | <b>√</b> | Yes      |

| $C_{\rm f} = 100$                                           | open     | V        |               |          |          | <b>✓</b>      | ~        | Yes      |

| $C_{C2} = 100$                                              | open     |          |               |          |          |               | <b>√</b> | Yes      |

| $R_{bias1} = 100k$                                          | open     |          | <b>√</b>      | <b>√</b> |          | <b>√</b>      |          | Yes      |

| $R_{bias2} = 100k$                                          | open     |          | $\overline{}$ | <b>√</b> | <b>√</b> |               | <b>✓</b> | Yes      |

| $R_{\rm L} = 100 {\rm k}$                                   | open     | <b>~</b> | <b>√</b>      | <b>√</b> | <b>√</b> | <b>√</b>      | <b>√</b> | No (3)   |

| $N_0(D-S)$                                                  | open     | <b>√</b> |               | ✓        |          |               | <b>√</b> | Yes      |

| $N_1(D-S)$                                                  | open     | <b>√</b> |               | <b>√</b> | <b>√</b> |               | <b>✓</b> | Yes      |

| $N_2(D-S)$                                                  | open     |          |               |          |          | <b>√</b>      |          | Yes      |

| $N_3(D-S)$                                                  | open     | <b>√</b> |               |          |          | <b>√</b>      | <b>√</b> | Yes      |

| $N_4(D-S)$                                                  | open     | <b>√</b> |               |          |          |               | <b>✓</b> | Yes      |

#### VIII. CONCLUSION

A new approach for test and diagnosis of non-linear circuits based on probability density moments of the output was presented. We also showed the effective use of RV transformation to sensitize the output moments to circuit parameters. The minimum sizes of detectable faults in some of the circuit parameters are as low as 10% for an elliptic filter, which implies impressive fault coverage can be achieved with moments as a test metric. Further, the prudent choice of RV transformations can enhance the fault detection resolution. We also proposed a method for localizing catastrophic faults and showed that good diagnostic coverages can be obtained by choosing expansions of moments of the order o(ln(N)) for N faults.

# APPENDIX

Output Variance of RC Filter. We use the frequency domain approach to find the transformed RV for Gaussian noise input excitation of a first order RC filter of Figure 2. The transfer function of that filter is given by

$$H(s) = \frac{V_o(s)}{V_i(s)} = \frac{1}{sRC + 1} \implies |H(j\omega)|^2 = \frac{1}{(\omega RC)^2 + 1}$$

(13)

With white noise as the input, the discrete values are sampled Gaussian RV of zero mean and variance  $=\frac{N_o}{2}$ . The output of this filter which is the filtered response is given by  $v_o$  and its frequency domain expression is given by

$$\left|V_o(j\omega)\right|^2 = \frac{1}{\left(\omega RC\right)^2 + 1} \left|V_i(j\omega)\right|^2 \tag{14}$$

To compute the effective second order moment we integrate this output over all frequencies, i.e.,  $\omega = (0, \infty)$ .

$$\overline{\mu_2} = \int_0^\infty \left( \frac{d\omega}{(\omega RC)^2 + 1} \right) \frac{N_o}{2}$$

$$= \frac{1}{RC} \frac{N_o}{2} \arctan(\omega RC) \Big|_0^\infty = \frac{N_o \pi}{4RC}$$

(15)

Fig. 8. Schematic of low noise amplifier.

#### REFERENCES

- [1] E. Acar and S. Ozev, "Defect-Based RF Testing Using a New Catas-

- E. Acar and S. Ozev, "Defect-Based RF Testing Using a New Catastrophic Fault Model," in *Proc. International Test Conf.*, 2005. F. Azais, Y. Bertrand, M. Renovell, A. Ivanov, and S. Tabatabaei, "An All-Digital DFT Scheme for Testing Catastrophic Faults in PLLs," *IEEE Design & Test of Computers*, vol. 20, no. 1, pp. 60–67, 2003. S. Bracho, M. Martinez, and J. Arguelles, "Current Test Methods in Mixed Signal Circuits," in *Proc. 38th Midwest Symp. Circuits and Systems*, vol. 2, 1995, pp. 1162–1167. K. R. Eckersall, P. L. Wrighton, I. M. Bell, B. R. Bannister, and G. E. Taylor, "Testing Mixed Signal ASICs Through the Use of Supply Current Monitoring," in *Proc. Third European Test Conf.*, 1993, pp. 385–391.

- [5] D. D. Gaitonde and D. M. H. Walker, "Hierarchical Mapping of Spot Defects to Catastrophic Faults-Design and Applications," *IEEE Transactions on Semiconductor Manufacturing*, vol. 8, no. 2, pp. 167–

- W. M. Lindermeir, H. E. Graeb, and K. J. Antreich, "Analog Testing by Characteristic Observation Inference," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 18, no. 9, pp. 1353-1368, 1999.

- L. Milor and V. Visvanathan, "Detection of Catastrophic Faults in

- L. Milor and V. Visvanathan, "Detection of Catastrophic Faults in Analog Integrated Circuits," *IEEE Trans. Comp. Aided Design*, vol. 8, no. 6, pp. 114–130, Jun. 1989.

M. Tadeusiewicz and S. Halgas, "An Efficient Method for Simulation of Multiple Catastrophic Faults," in *Proc. 15th IEEE Int. Conf. Electronics, Circuits and Systems*, 2008, pp. 356–359.

M. L. Bushnell and V. D. Agrawal, *Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits*. Boston: Springer, 2000.

- [10] J. Figueras, "Possibilities and Limitations of IDDQ Testing in Submicron CMOS," in Proc. Innovative Systems in Silicon Conf., Oct. 1997, pp. 174-185

- [11] Z. Guo, X. M. Zhang, J. Savir, and Y.-Q. Shi, "On Test and Characterization of Analog Linear Time-Invariant Circuits Using Neural Networks," in *Proc. 10th Asian Test Symp.*, 2001, pp. 338–343. Y. Xing, "Defect-Oriented Testing of Mixed-Signal ICs: Some Industrial

- [12] I. Anig, Detect-Oriented testing of winked-Signal Ics. Sofile Industrial Experience," in *Proc. Int. Test Conference*, Oct. 1998, pp. 678–687.

[13] J. Savir and Z. Guo, "Test Limitations of Parametric Faults in Analog Circuits," in *Proc. 11th Asian Test Symp.*, 2002, pp. 39–44.

[14] M. Aminian and F. Aminian, "A Comprehensive Examination of Neural Network Architectures for Analog Fault Diagnosis," in *Proc. Int. Joint Conf. Neural Network*, pp. 32001, pp. 3204–3206.

- Network Architectures for Analog Fault Diagnosis," in *Proc. Int. Joint Conf. Neural Networks*, vol. 3, 2001, pp. 2304–2309.

[15] S. Chakrabarty, V. Rajan, J. Ying, M. Mansjur, K. Pattipati, and S. Deb, "A Virtual Test-Bench for Analog Circuit Testability Analysis and Fault Diagnosis," in *Proc. IEEE AUTOTESTCON*, 1998, pp. 337–352.

[16] Y. Deng, Y. He, and Y. Sun, "Fault Diagnosis of Analog Circuits with Tolerances Using Artificial Neural Networks," in *Proc. IEEE Asia-Pacific Conf. Circuits and Systems*, 2000, pp. 292–295.

[17] R. Spina and S. Upadhyaya, "Fault Diagnosis of Analog Circuits Using Artificial Neural Networks as Signature Analyzers," in *Proc. Fifth Annual IEEE Int. ASIC Conf. and Exhibit*, 1992, pp. 355–358.

[18] J. C. Sutton-III. "Identification of Electronic Component Faults Using

- J. C. Sutton-III, "Identification of Electronic Component Faults Using Neural Networks and Fuzzy Systems," in *Proc. Int. Industrial Electron*-

- ics. Control. Instrumentation, and Automation Power Electronics and

- W. P. M. Allen, D. G. Bailey, S. N. Demidenko, and V. Piuri, "Analysis and Application of Digital Spectral Warping in Analog and Mixed-Signal IEEE Transactions on Reliability, vol. 52, no. 4, pp. 444–457, Testing," II Dec. 2003.

- V. Zagursky, N. Semyonova, and M. Sirovatkina, "A Histogram Method for Analog-Digital Converters Testing in Time and Spectral Domain," in *Proc. European Design and Test Conference*, Mar. 1995, p. 607.

Z. Guo and J. Savir, "Analog Circuit Test Using Transfer Function Coefficient Estimates," in *Proc. Int. Test Conf.*, Oct. 2003, pp. 1155–

- 1103.

S. Sindia, V. Singh, and V. D. Agrawal, "Multi-Tone Testing of Linear and Nonlinear Analog Circuits Using Polynomial Coefficients," in *Proc. Asian Test Symposium*, Nov. 2009, pp. 63–68.

——, "Polynomial Coefficient Based DC Testing of Non-Linear Analog Circuit," in Proc. 2008.

- —, Polynomial Coefficient Based DC Testing of Non-Linear Analog Circuits," in *Proc. 19th ACM Great Lakes Symp. on VLSI*, May 2009, pp. 69–74.

R. Rajsuman, *IDDQ Testing for CMOS VLSI*. Artech House, 1995.

W. M. Lindermeir, T. J. Vogels, and H. E. Graeb, "Analog Test

- Design with IDD Measurements for the Detection of Parametric and Catastrophic Faults," in *Proc. Design, Automation and Test in Europe*, 1998, pp. 822–827.

[26] P. Kabisatpathy, A. Barua, and S. Sinha, "A Pseudo-Random Testing

- Scheme for Analog Integrated Circuits Using Artificial Neural Network Model-Based Observers," in *Proc. 45th Midwest Symp. on Circuits and*

- Systems, vol. 2, 2002.

[27] J. Park, H. Shin, and J. Abraham, "Pseudorandom Test for Nonlinear Circuits Based on a Simplified Volterra Series Model," in 8th International Symposium on Quality Electronic Design, Mar 2007, pp. 495

- -500.

V. D. Agrawal, "An Information Theoretic Approach to Digital Fault Testing," *IEEE Trans. Comput.*, vol. 30, pp. 582-587, Aug. 1981. [Online]. Available: http://portal.acm.org/citation.cfm?id=1311096.1311688

N. Shanbhag, K. Soumyanath, and S. Martin, "Reliable Low-Power Design in the Presence of Deep Submicron Noise," in *Proc. Int. Symp. Low Power Electronics and Design*, 2000, pp. 295-302.

N. R. Shanbhag, "A Fundamental Basis for Power-Reduction in VLSI Circuits," in *Proc. IEEE Int. Symp. Circuits and Systems*, vol. 4, 1996.

- Circuits," in Proc. IEEE Int. Symp. Circuits and Systems, vol. 4, 1996,

- pp. 9–12.

S. Sindia, V. Singh, and V. D. Agrawal, "V-Transform: An Enhanced Polynomial Coefficient Based DC Test for Non-Linear Analog Circuits," in *Proc. of 8th IEEE East West Design & Test Symposium*, Sep. 2009,

- pp. 283–286. S. Sindia, V. D. Agrawal, and V. Singh, "Non-linear Analog Circuit Test and Diagnosis under Process Variation using V-Transform Coefficients,"

- and Diagnosis under Process variation using v-Transform Coefficients, in 29th VLSI Test Symposium, May 2011, pp. 64–69.

S. Sindia, V. Agrawal, and V. Singh, "Testing Linear and Non-linear Analog Circuits using Moment Gnerating Functions," in 12th Latin American Test Workshop (LATW), Mar. 2011, pp. 1–6.

A. Papoulis, Probability, Random Variables, and Stochastic Processes.

- McGraw-Hill, 1965.

- R. Kondagunturi, E. Bradley, K. Maggard, and C. Stroud, "Benchmark Circuits for Analog and Mixed-Signal Testing," in *Proc. 20th Int. Conf. on Microelectronics*, Mar. 1999, pp. 217–220.