| Table 19.9. QUIDTEST results. |         |         |                  |                        |        |                  |                        |

|-------------------------------|---------|---------|------------------|------------------------|--------|------------------|------------------------|

|                               | # of    | # of    | %                | Leakage                | # of   | %                | Weak                   |

| Ckt.                          | tran-   | leakage | $_{ m selected}$ | $\operatorname{fault}$ | weak   | $_{ m selected}$ | $\operatorname{fault}$ |

|                               | sistors | faults  | vectors          | coverage               | faults | vectors          | coverage               |

| 1                             | 7584    | 39295   | 0.50 %           | 94.84 %                | 1923   | 0.35~%           | 85.30 %                |

| 2                             | 42373   | 220571  | 0.99 %           | 90.50~%                | 1497   | 0.21 %           | 87.64 %                |

Table 13.3: QUIETEST results.

Meyer floating pin technique [350, 712] or circuits in the tester power supply [176]. Off-chip  $I_{DDQ}$  measurements are degraded by the pulse width of the CMOS IC transient current, impedance loading of the tester probe (from 20 to 200 pF), and current leakages into/out of the tester. Also, the high noise of the tester load board [176, 283] is caused by impedances on probes that vary with the probe voltage. This can be eliminated if output pins are disconnected or put in high impedance mode during the  $I_{DDQ}$  test. Many testers let one multiplex one probe between two chip pins, but this increases tester noise, and requires a slower  $I_{DDQ}$  testing rate.

## 13.3.4 Current Limit Setting

Production  $I_{DDQ}$  current testing needs a pass/fail value for the current limit, and it is difficult to pick a correct value. One should evaluate test data from representative circuits and characterize  $I_{DDQ}$  current using every vector from a functional vector set and a slow, precision measurement unit on a tester [283].

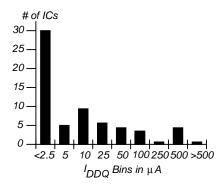

Figure 13.14 [617] shows the relative  $I_{DDQ}$  scatter for various vectors. Most devices have low  $I_{DDQ}$  current (they are good), but there is a distribution of high-current devices due to gate oxide shorts. There may be a multi-modal distribution with enough separation between the peaks to indicate an appropriate limit for  $I_{DDQ}$  current. One should drive the  $I_{DDQ}$  limit to  $< 1~\mu A$ . The  $I_{DDQ}$  data expose many undetected defects [282, 450, 451, 519, 520]. It is common in production testing to have  $1~\mu A \leq I_{DDQ} \ limit \leq 20~\mu A$ . A 0.5 to 1~mA limit for  $I_{DDQ}$  current on a few vectors can find defects not caught by scan-based stuck-fault voltage testing with 99.6% stuck-at fault coverage [520].

Figure 13.14:  $I_{DDQ}$  current histogram for a 32-bit microprocessor.