Problems 251

8.10 Prove that a fault that is untestable in the stand-alone combinational logic is also untestable in the sequential circuit.

- 8.11 Prove that a fault in the combinational logic of a synchronous sequential circuit is untestable if no combinational test vector can be justified using fault-free time-frames. *Hint*: See the paper by Agrawal and Chakradhar [30].

- 8.12 Pseudo-combinational circuit. Derive a combinational circuit by replacing all flip-flops by shorting wires in the circuit of Figure 8.9. This is known as the pseudo-combinational transformation, which can be applied to any cycle-free clocked sequential circuit [463]. Derive a test for the fault D s-a-0 in the pseudo-combinational circuit. Verify that the vector sequence obtained by repeatedly applying this vector four times will detect the D s-a-0 fault in the original sequential circuit. Note that the number of repetitions equals sequential depth + 1.

- 8.13 Prove that if a combinational test vector can be obtained for a fault in the pseudo-combinational circuit, then that vector repeated as many times as sequential depth + 1 will always detect the corresponding fault in the sequential circuit. Hint: See the paper by Min and Rogers [468]

- 8.14 Prove that a synchronous sequential circuit that is not initializable, must be cyclic.

- 8.15 Cyclic circuits. Redefine the s-graph by including PIs and POs as additional vertices. Levelize the graph starting from PI vertices using the minimum distance rule. Draw the new types of levelized s-graphs for circuits of Figures 8.9 and 8.13. What do the depths of these graphs represent in terms of the length of test sequences?

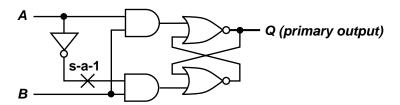

- 8.16 Race fault in asynchronous circuit. Derive a test for the s-a-1 fault at the output of the NOT gate in the circuit of Figure 8.27. Is this a race fault?

Figure 8.27: Circuit for Problem 8.16.

8.17 Oscillation fault. The asynchronous circuit of Figure 8.28 is designed to have no memory state. Derive a test for the s-a-1 fault on the C input of the NAND gate and show that it is an oscillation fault. Redesign the fault-free function as a combinational circuit.