## TABLE OF CONTENTS

|    | 10.9 | Summary                                                             | 382 |

|----|------|---------------------------------------------------------------------|-----|

| 11 | -    | DEL-BASED ANALOG AND MIXED-SIGNAL TEST                              | 385 |

|    |      | Analog Testing Difficulties                                         |     |

|    |      | Analog Fault Models                                                 |     |

|    |      | Levels of Abstraction                                               |     |

|    |      | Types of Analog Testing                                             |     |

|    | 11.5 | Analog Fault Simulation                                             |     |

|    |      | 11.5.1 Motivation                                                   |     |

|    |      | 11.5.2 DC Fault Simulation of Nonlinear Circuits                    |     |

|    |      | 11.5.3 Linear Analog Circuit AC Fault Simulation                    |     |

|    |      | 11.5.4 Monte-Carlo Simulation                                       |     |

|    | 11.6 | Analog Automatic Test-Pattern Generation                            |     |

|    |      | 11.6.1 ATPG Using Sensitivities                                     |     |

|    |      | 11.6.2 ATPG Using Signal Flow Graphs                                |     |

|    |      | 11.6.3 Additional Methods                                           |     |

|    | 11.7 | Summary                                                             | 413 |

| 12 | DEL  | AY TEST                                                             | 417 |

|    | 12.1 | Delay Test Problem                                                  | 417 |

|    | 12.2 | Path-Delay Test                                                     | 420 |

|    |      | 12.2.1 Test Generation for Combinational Circuits                   | 424 |

|    |      | 12.2.2 Number of Paths in a Circuit                                 |     |

|    |      | Transition Faults                                                   |     |

|    | 12.4 | Delay Test Methodologies                                            |     |

|    |      | 12.4.1 Slow-Clock Combinational Test                                |     |

|    |      | 12.4.2 Enhanced-Scan Test                                           |     |

|    |      | 12.4.3 Normal-Scan Sequential Test                                  |     |

|    |      | 12.4.4 Variable-Clock Non-Scan Sequential Test                      |     |

|    |      | 12.4.5 Rated-Clock Non-Scan Sequential Test                         |     |

|    | 12.5 | Practical Considerations in Delay Testing                           |     |

|    |      | 12.5.1 At-Speed Testing                                             |     |

|    | 12.6 | Summary                                                             | 436 |

| 13 | IDDO | Q TEST                                                              | 439 |

|    | 13.1 | Motivation                                                          | 439 |

|    | 13.2 | Faults Detected by $I_{DDQ}$ Tests                                  | 441 |

|    |      | $I_{DDQ}$ Testing Methods                                           | 446 |

|    |      | 13.3.1 $I_{DDQ}$ Fault Coverage Metrics                             | 446 |

|    |      | 13.3.2 $I_{DDQ}$ Test Vector Selection from Stuck-Fault Vector Sets | 448 |

|    |      | 13.3.3 Instrumentation Problems                                     | 451 |

|    |      | 13.3.4 Current Limit Setting                                        | 452 |

|    | 13.4 | Surveys of $I_{DDQ}$ Testing Effectiveness                          |     |

|    |      | Limitations of $I_{DDQ}$ Testing                                    |     |

|    |      | Delta $I_{DDQ}$ Testing                                             |     |

|    |      |                                                                     |     |

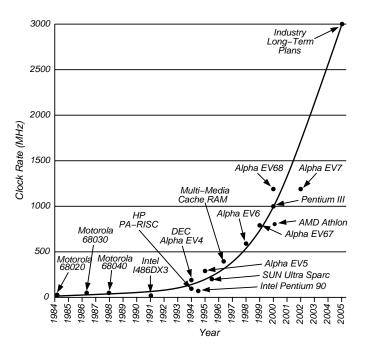

Figure 1.4: Microprocessor clock rates.

We compute the yearly running cost of the ATE by assuming a linear depreciation over five years, and an annual maintenance cost of 2% of the purchase price. The operating cost of the building, facilities, auxiliary equipment (wafer and chip handlers, fixtures, etc.), and personnel is estimated to be 0.5M. Thus:

$$\begin{aligned} Running \ cost &= Depreciation + Maintenance + Operating \ cost \\ &= \$0.854M + \$0.085M + \$0.5M = \$1.439M/year \end{aligned}$$

The tester is used in three eight-hour shifts per day and on all days of the year. Therefore:

Testing

$$cost = \frac{\$1.439M}{365 \times 24 \times 3,600} = 4.56 \ cents/second$$

The test time for a digital ASIC (application specific integrated circuit) is 6 seconds. That gives the test cost as 27.36 cents. Since the bad chips are not sold, their test cost must be recovered from the sale of good chips. If the yield is 65%, then the test component in the sale price of a good chip is 27.36/0.65  $\approx$  42 cents.

The test time of a chip depends on the types of tests conducted. These may include parametric tests (leakage, contact, voltage levels, etc.) applied at a slow speed, and vector tests (also called "functional tests" in the ATE environment) applied at high speed. The time of parametric tests is proportional