## Post-Synthesis Simulation

VITAL Models, SDF Files, Timing Simulation

#### Post-synthesis simulation

- Purpose:

- Verify correctness of synthesized circuit

- Verify synthesis tool delay/timing estimates

- Synthesis tool generates:

- ▶ Gate-level netlist in Verilog (and/or VHDL\*\*)

- Standard Delay Format (SDF) file of estimated delays

- ▶ IBM\_CMOS8HP technology directory:

- /verilog gate-level Verilog models

- ▶ /fvhdl gate-level functional VHDL models\*\*

- ▶ /vital VITAL-compliant VHDL models\*\*

- Drive with same "do" file/testbench as for behavioral model

\*\* VHDL models omitted from recent CMOS8HP package

#### Timing simulation of HDL netlists

- Synthesized netlists comprise cells from a library (CMOS8HP library, for example)

- Each library cell has been *characterized* to determine delays, constraints, pin capacitance, area, etc.

- Cell libraries represent timing information using the VITAL standard

- VITAL = VHDL Initiative Toward ASIC Libraries (IEEE Standard 1076.4)

- Verilog models can also be made VITAL-compatible

- Synthesis tools create a Standard Delay Format (SDF) file of estimated timing data for each cell in the design, for use with VITAL-compatible models

- ▶ SDF = IEEE Standard 1497

- Designed for "back-annotation" of netlists with delay data

#### Example

- The modulo 6 counter was synthesized using the CMOS8HP standard cell library

- The next slides show VITAL-compatible Verilog model of an XOR gate and a D flip flop from the library.

- Subsequent slides show a partial SDF file with the timing parameters extracted for one instance each of an XOR gate and D flip flop in the synthesized counter

# Verilog netlist for cell <u>modulo6</u> produced by Synopsys DC from CMOS8HP Cell Library

```

module modulo6 (CLEARbar, L Cbar, CLK, I, Q);

input [2:0] I;

output [2:0] Q;

input CLEARbar, L Cbar, CLK;

wire n8, n9, n10, n11, n12, n13, n14, n15, n16;

DFFS B Q reg 0 (.D(n10), .CLK(CLK), .S(n11), .Q(n16), .QBAR(Q[0]));

DFFS B Q reg 2 (.D(n9), .CLK(CLK), .S(n11), .QBAR(Q[2]));

DFFS_B Q_reg_I_ ( .D(n8), .CLK(CLK), .S(n11), .QBAR(Q[1]) );

AOI21_A U14 ( .AI(Q[2]), .A2(Q[0]), .B(L_Cbar), .Z(n15) );

XOR2 \ A \ UI5 \ (.A(Q[0]), .B(Q[1]), .Z(n13));

INVERT_B U16 ( .A(CLEARbar), .Z(n11) );

INVERT B U17 (.A(L Cbar), .Z(n12));

AOI22_A UI8 ( .AI(L_Cbar), .A2(I[0]), .BI(nI6), .B2(nI2), .Z(nI0) );

AO122 A U19 (.AI(L Cbar), .A2(I[I]), .BI(nI5), .B2(nI3), .Z(n8));

AO21 B U20 ( .AI(Q[0]), .A2(Q[1]), .B(Q[2]), .Z(nI4) );

AOI22_A U21 (.AI(L_Cbar), .A2(I[2]), .BI(nI5), .B2(nI4), .Z(n9));

endmodule

```

### Using the standard cell HDL library

- The CMOS8HP digital design kit contains HDL models for each of the standard cells:

- /verilog gate-level Verilog models

- The Verilog models have been compiled into library CMOS8HP.

- Add CMOS8HP to your Modelsim Library list:

- ▶ In Modelsim select: File > New > Library

- Select: Create a map to an existing library

- **▶** Enter Name: CMOS8HP

- In box "Library Maps to", enter, or use the Browse button to select, /class/ELEC6250/cmos8hp/std\_cell/v.20130404/Verilog/CMOS8HP

- Click OK

- If starting simulation from the menu, select CMOS8HP on the Libraries tab of the Start Simulation pane.

- If starting simulation with vsim command, use the -L switch:

```

vsim modulo6_1.v -L CMOS8HP

```

```

`timescale 1ns/1ps

XOR2_A.v

`celldefine

module XOR2 A (Z, A, B);

VITAL-compatible

output Z;

Verilog model

input A;

input B;

xor U0 (Z, B, A); //logic function (Verilog primitive)

specify

specparam

tdelay_A_Z_01_0=0.01,

tdelay_A_Z_10_0=0.01,

Propagation delay parameters

tdelay_A_Z_01_1=0.01,

(with defaults)

tdelay_A_Z_10_1=0.01;

tdelay_B_Z_01_0=0.01,

tdelay_B_Z_10_0=0.01,

Values to come from SDF file

tdelay_B_Z_01_1=0.01,

tdelay_B_Z_10_1=0.01;

(A -=> Z) = (tdelay_A_Z_01_0, tdelay_A_Z_10_0);

(B -=> Z) = (tdelay_B_Z_01_0, tdelay_B_Z_10_0);

Rise time

Fall time

endspecify

endmodule

`endcelldefine

```

# DFFS\_B.v VITAL-Compatible Model

```

Logic and timing section of model:

DFFS i0 (Q,QBAR,CLK_dly,D_dly,S_dly,notifier); \\logic function

specify

//timing information

(posedge CLK => (Q +: CLK)) = (0.01:0.01:0.01, 0.01:0.01:0.01);

(posedge S => (Q +: S)) = (0.01:0.01:0.01, 0.01:0.01:0.01);

(posedge CLK => (QBAR +: CLK)) = (0.01:0.01:0.01, 0.01:0.01:0.01);

(posedge S = > (QBAR -: S)) = (0.01:0.01:0.01, 0.01:0.01:0.01);

$setuphold (posedge CLK &&& ~S_dly,posedge D,0.01,0.01,notifier, ,

constraints

,CLK_dly,D_dly);

$setuphold (posedge CLK &&& ~S_dly,negedge D,0.01,0.01,notifier, ,

,CLK_dly,D_dly);

$recrem (negedge S,posedge CLK,0.01,0.01,notifier, , ,S_dly,CLK_dly);

$width (negedge CLK &&& ~S_dly,0.01,0,notifier);

$width (posedge CLK &&& ~S_dly,0.01,0,notifier);

$width (posedge S,0.01,0,notifier);

endspecify

```

### Standard Delay Format (SDF) File

- Produced by synthesis tool (Leonardo)

- ▶ Contains VITAL parameter values for all cells in the netlist

- Example (for synthesized counter and CMOS8HP library):

```

SDF Header – common to all cells in this synthesized netlist (DELAYFILE

```

#### Extracted SDF data for XOR instance U15

-- path delays only (no constraints)

These will replace default values of delay parameters in XOR2\_A.v

```

tdelay_A_Z_01_0 tdelay_A_Z_10_0 tdelay_B_Z_01_0 tdelay_B_Z_10_0

```

### SDF data for DFFS\_B instance Q\_reg\_1\_

```

(CELL

(CELLTYPE "DFFS_B")

Select Min/Typ/Max

(INSTANCE Q_reg_1_)

(Min: Typ: Max) at simulation setup

(DELAY

(ABSOLUTE

(IOPATH CLK Q (0.132:0.132:0.132) (0.083:0.083:0.083))

(IOPATH S Q (0.142:0.143:0.143) () s cannot force Q low

(IOPATH CLK QBAR (0.069:0.073:0.073) (0.100:0.107:0.107))

(IOPATH S QBAR () (0.118:0.124:0.124)) ))

S cannot force QBAR high

(TIMINGCHECK

(WIDTH (posedge CLK) (0.041:0.041:0.041))

constraints

(WIDTH (negedge CLK) (0.072:0.072:0.072))

(SETUP D (posedge CLK) (0.098:0.109:0.109))

(HOLD D (posedge CLK) (-0.073: -0.019: -0.019))

(RECOVERY S (posedge CLK) (0.008:0.012:0.012))

(HOLD S (posedge CLK) (0.001: -0.003: -0.003))

(WIDTH (posedge S) (0.086:0.086:0.086))

```

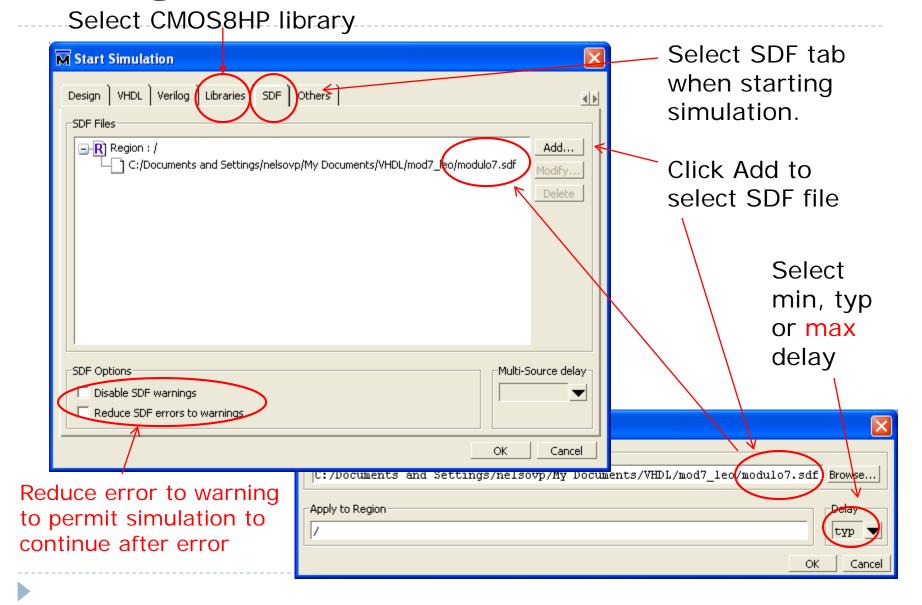

## Timing simulation in Modelsim

# Simulating with SDF & do file

vsim modulo6 —sdfmax modulo6\_I.sdf -sdfnoerror -L CMOS8HP —t ps

#### Compile options

-sdfmax modulo6 | I.sdf | path to SDF file

Apply delays only to modulo6 netlist.

Can also use -sdfmin or -sdftyp.

- -sdfnoerror Reduce SDF errors to warnings to enable simulation with missing hold times, etc.

- -L CMOS8HP Library of gate-level Verilog models.

- -t ps Timing resolution consistent with SDF.

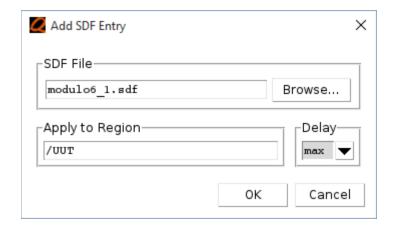

## Simulating with SDF & testbench

vsim -sdfmax /UUT=modulo6\_I.sdf -sdfnoerror -L CMOS8HP -t ps modulo6\_bench

#### Compile options

-sdfmax /UUT=modulo6\_I.sdf

Apply delays only to design (UUT) within the testbech. Can also use -sdfmin or -sdftyp.

- -sdfnoerror Reduce SDF errors to warnings to enable simulation with missing hold times, etc.

- -L CMOS8HP Library of gate-level Verilog models.

- -t ps Timing resolution consistent with SDF.

## Testbench: modulo6\_bench.v

```

timescale 1 ns / 10 ps

module modulo6_bench ();

//no top-level inputs

reg clk, clearbar, load_countbar;

//counter control inputs

//counter parallel inputs

reg [2:0] Din;

//expected counter outputs

reg [2:0] Qint;

wire [2:0] Qout;

//outputs driven by counter

integer i;

// instantiate the modulo6 counter

modulo6 UUT (.CLEARbar(clearbar), .L_Cbar(load_countbar), .CLK(clk), .I(Din), .Q(Qout));

// produce 20 ns period clock

initial clk <= 0:

//initial state 0

always #10 \text{ clk} <= \sim \text{clk};

//toggle every 10ns

// produce other inputs

initial begin

Din = 3'b101:

//inputs for load test

clearbar = 1'b1:

//clearbar inactive initially

load_countbar = 1'b1;

//select load function initially

//activate clearbar at time 5

#5 clearbar <= 1'b0;

#10 clearbar <= 1'b1:

//deactivate clearbar at time 15

if (Qout !== 3'b000) $display("ERROR Qout %b did not reset to 0\n",Qout);

#20:

//wait for load of 101

if (Qout !== Din) $display("ERROR Qout %b did not load %b \n",Qout,Din);

Din = 3'b010;

//load changing all 3 ffs

//wait for load of 010

#20:

Continued on next slide

```

## Testbench: modulo6\_bench.v

#### (Continued)

```

if (Qout !== Din) $display("ERROR Qout %b did not load %b \n",Qout,Din);

Din = 3'b101:

//load changing all 3 ffs

#20:

//wait for load of 101

if (Qout !== Din) $display("ERROR Qout %b didnot load %b \n",Qout,Din);

#5 clearbar <= 1'b0:

//activate clearbar at time 5 to reset bits 2 and 0

#15 clearbar <= 1'b1;

//deactivate clearbar at time 15

if (Qout !== 3'b000) $display("ERROR Qout %b did not reset to 0\n",Qout);

Din = 3'b010:

//load 010

#20:

//wait for load of 010

if (Qout !== Din) $display("ERROR Qout %b didnot load %b \n",Qout,Din);

#5 clearbar <= 1'b0;

//activate clearbar at time 5 to reset bit 1

//deactivate clearbar at time 15

#15 clearbar <= 1'b1;

if (Qout !== 3'b000) $display("ERROR Qout %b did not reset to 0\n",Qout);

Qint <= Qout:

//start count from current state

#20 load countbar <= 1'b0;

//disable load & enable count

for (i=0; i<12; i=i+1) begin

//do two complete count cycles

Qint = (Qint + 1) \% 6;

//expected modulo-6 count

//wait until after count

#20:

if (Qint !== Qout) $display("ERROR Qout %b count not %b \n",Qout,Qint);

end

end

endmodule

```

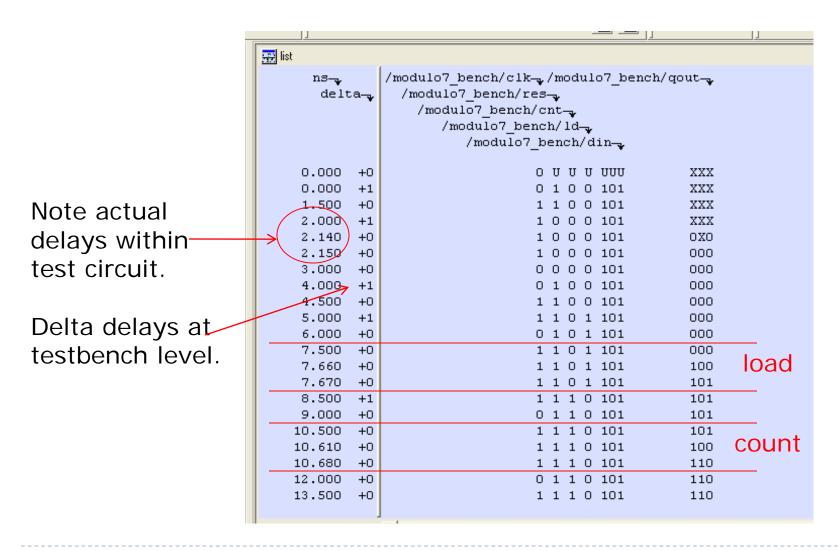

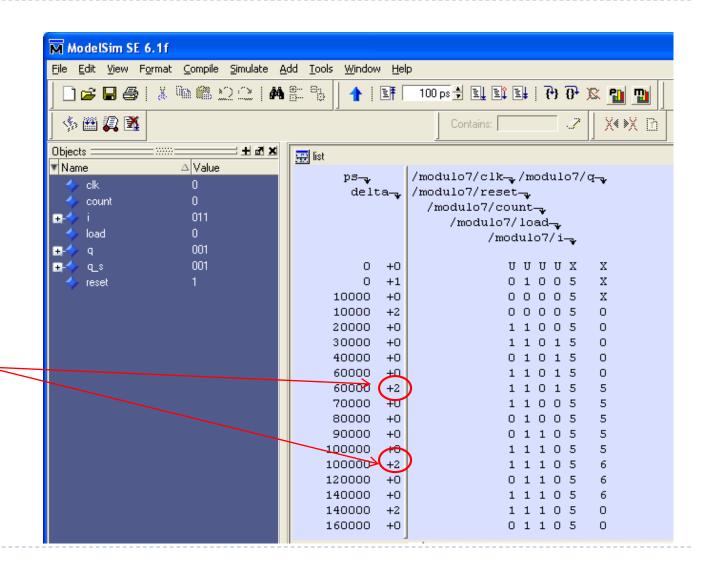

#### Simulation without SDF

Note "delta" delays for behavioral model.

### Simulation using SDF file