# Automated Synthesis from HDL models

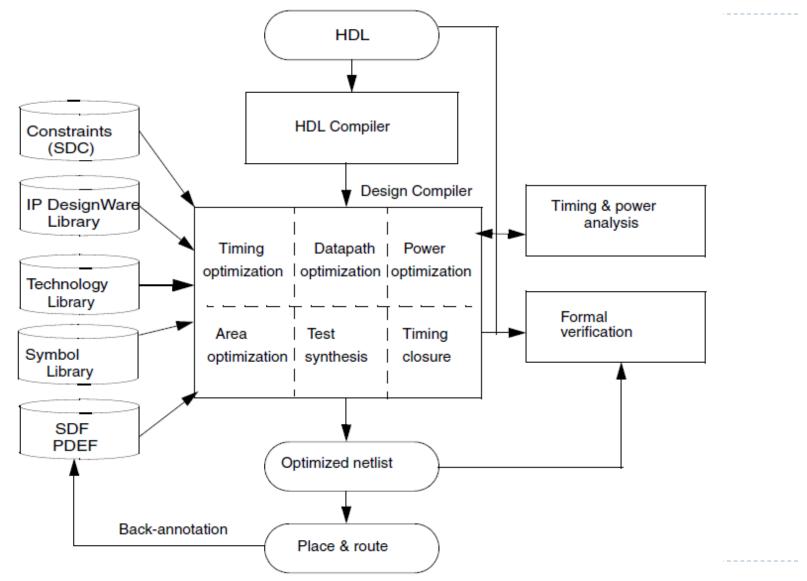

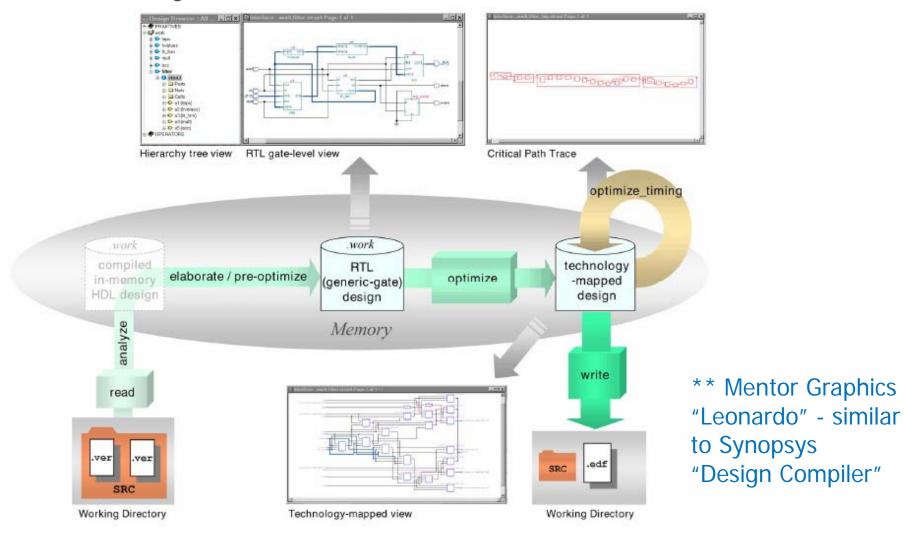

**Design Compiler** (Synopsys)

Leonardo (Mentor Graphics)

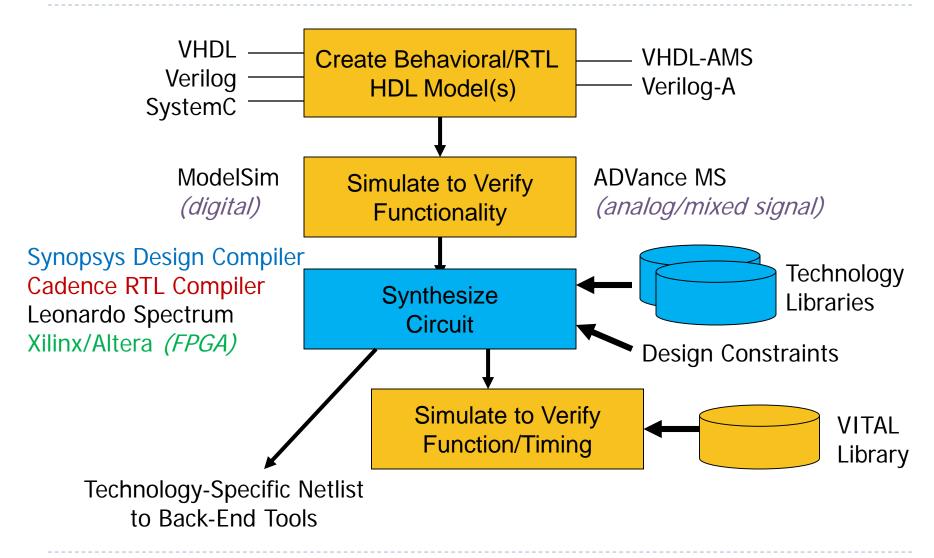

## Front-End Design & Verification

### Automated synthesis

### Synopsys Design Compiler Documents

## Documents (pdf) located on Linux server in

/class/ELEC6250/Synopsys\_Docs/

- DC User Guide

- DC Command Line

- DC Synthesis Quickref

- DC Ref Constraints and Timing

- DC Ref Timing Optimization

- DesignVision Tutorial

- DesignVision User Guide

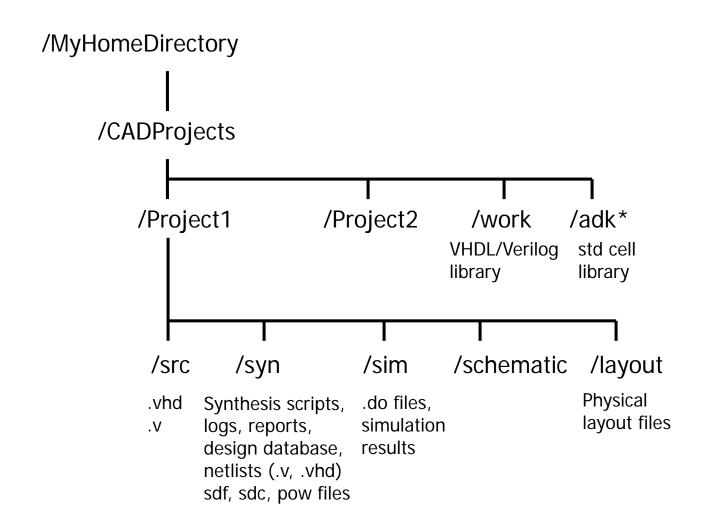

#### Project directory structure

### Invoking Design Compiler

- Interactive shell version:

- dc\_shell —f scriptFile

- Most efficient and common usage is to put TCL commands into scriptFile, including "quit" at the end

- ▶ TCL = Tool Command Language

- ▶ Edit and rerun scriptFile as needed

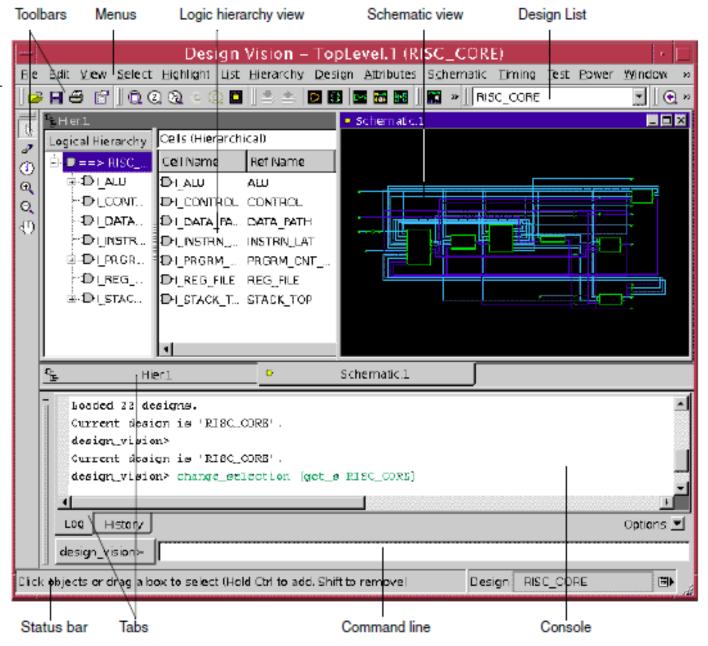

- GUI version (Design Vision)

- design\_vision

- From dc\_shell: gui\_start

- Main advantage over dc\_shell is to view the synthesized schematic

## and commands

write

Save the design database

report constraint

report timing

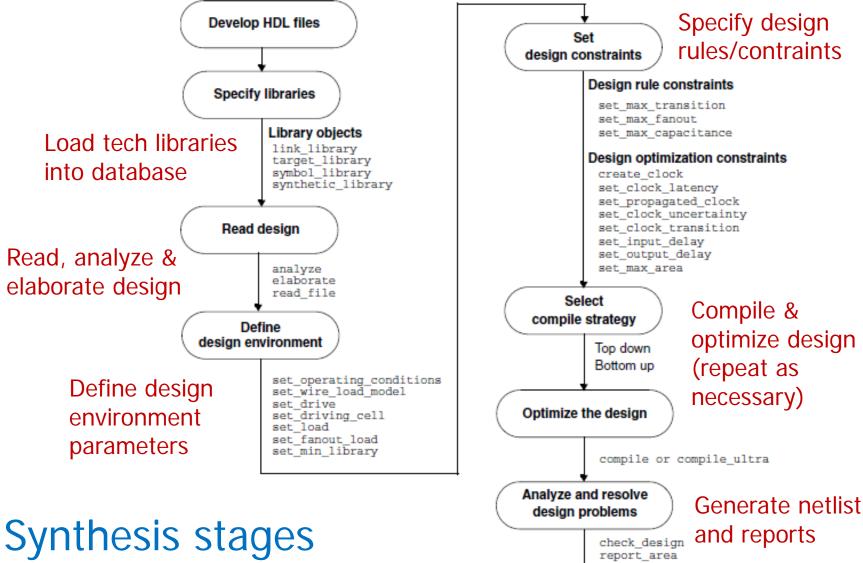

## Synopsys Design Compiler flow

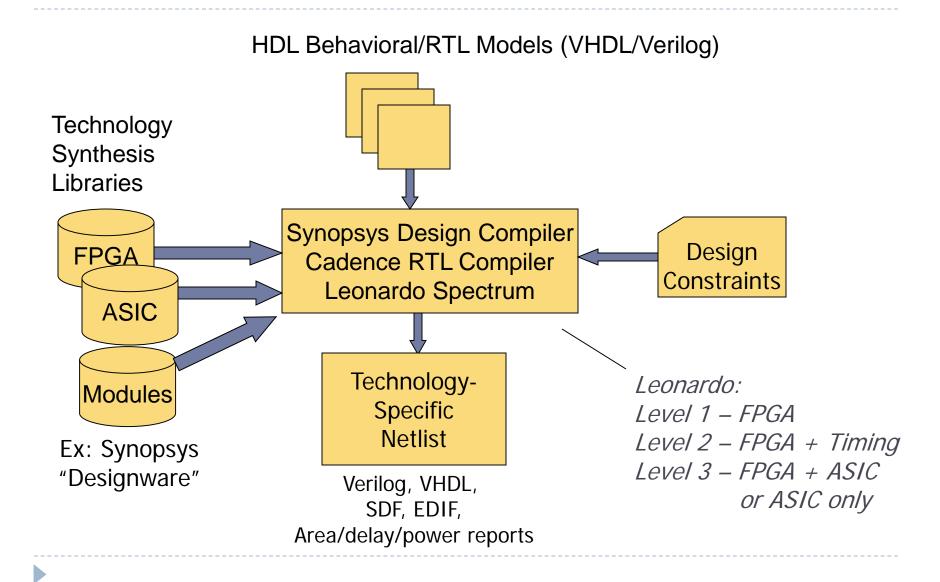

## ASIC synthesis flow\*\*

- target\_library : standard cell database (binary)

- cell area/pins/timing data (for synthesis decisions)

- synthetic\_library: Synopsys DesignWare components

- link\_library : use during linking

- Includes target and link library plus internal data (\*)

- symbol\_library : schematic symbols

- Synopsys installation includes a generic symbol library

- Define in file .synopsys\_dc.setup

### Setup file (8HP): .synopsys\_dc.setup

#### DC reads .synopsys\_dc.setup files in order:

- 1. Synopsys installation directory (all user projects)

- 2. User home directory (all projects for this user)

- 3. Current project directory (this project only)

```

set MyHome [getenv "HOME"]

set SynopsysInstall [getenv "STROOT"]

set CMOS8HP "/class/ELEC6250/cmos8hp/std_cell/v.20130404"

set search_path [list |

[format "%s%s" $CMOS8HP /synopsys/typ_v150_t025] \

[format "%s%s" $CMOS8HP /symbols/synopsys] \

[format "%s%s" $SynopsysInstall /libraries/syn] \

[format "%s%s" $SynopsysInstall /dw/sim_ver] \

[format "%s%s" $SynopsysInstall /dw]]

set target_library [list PnomV1p50T025_STD_CELL_8HP_12T.db]

set synthetic_library [list dw_foundation.sldb]

set link_library [list "*" $target_library $synthetic_library]

set symbol_library [list generic.sdb]

```

#### Synopsys DesignWare Package

- Predesigned components (tech-independent)

- arithmetic, filters, CRC gen's, counters, decoders, FIFOs, flipflop RAMs, etc.

- Let DC choose a component, or instantiate directly

- components chosen to implement arithmetic operators

- Example DW decrementer:

```

module decrementer (in_A, SUM_out);

parameter width = 8;

input [width-1:0] in_A;

output [width-1:0] SUM_out;

DW01_dec #(width) U1( .A(in_A), .SUM(SUM_out));

endmodule;

```

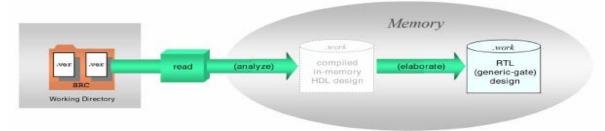

- Analyze syntax check and build database

- ▶ input VHDL and/or Verilog models

- check dependencies & resolve generics/parameters

- ▶ Elaborate synthesize to generic gates and black boxes

- technology-independent gates

- operators (arithmetic, relational, etc.) recognized and implemented with "black boxes" (no logic in them yet)

Read command does analyze + elaborate + pre-optimize

#### Analyze Command

- analyze {fl.v src/f2.v "top file.v"}

- Read and analyze into default memory database library "work"

- ▶ List HDL files in <u>bottom-up</u> order <u>top level last</u>

- Use quotes if embedded spaces in file name: "top file.v"

- Include directory if necessary: src/f2.v

- Analyze command switches:

- -format verilog (or vhdl) [defaultVHDL if file ext = .vhd/.vhdl or Verilog if file ext = .v/.verilog]

- -work lib\_name [lib where design to be stored (default = "work".)

Different libraries might be used for comparing designs]

- Examples:

- analyze {src/f1.v src/f2.vhd} (store in "work")

- analyze {src/f1.v src/f2.vhd} -work lib\_version2

#### Elaborate Command

- "Elaborate" a design currently in the memory database producing tech-independent circuit

- elaborate divider ["divider" = VHDL entity/Verilog module]

- Switches

- -single\_level [only do top level for bottom-up design]

- -architecture a l [if other than most recently analyzed]

- -work lib\_name [if name other than work]

- -generics { size=9 use\_this=TRUE initval="10011" }

- □ List format is { generic=value generic=value .... }

- -parameters [format same as generics]

### Example script

#Design-specific information — create variables for use in commands

```

set myFiles [list ./src/top.v ./src/Muxbig.v ]

set basename TOP

set fileFormat verilog

define_design_lib WORK —path ./syn

```

Unique for each design - not necessary, but convenient for multiple projects

#Design-independent: these commands need not be changed

```

analyze —format $fileFormat -lib WORK $myFiles

elaborate $basename —lib WORK —update

current_design $basename

link (link all design parts)

uniquify (make unique copies of replicated modules)

```

Commands using above design information

#### Read command

- Performs <u>both</u> analyze and elaborate steps

- Useful for single HDL file:

```

read_file —f verilog filename.v

```

Same switches as analyze and elaborate commands, plus (optional):

```

-dont_elaborate {fl.vhd} - do analysis but not elaborate

```

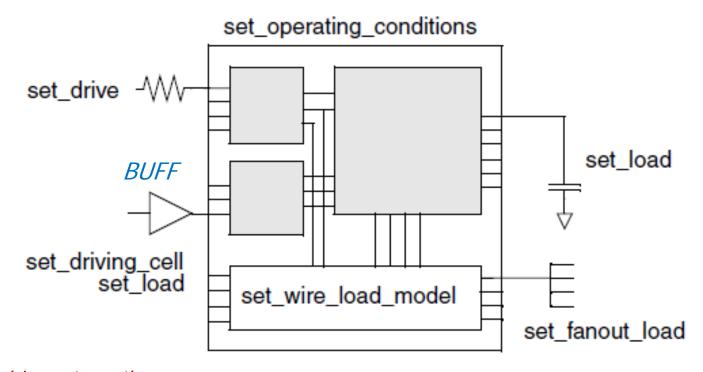

## Design environment

- Technology variables affect delay calculations

- Manufacturing process, temperature, voltage, fanouts, loads, drives, wireload models

- Defaults specified in the technology library

- ▶ 8HP technology libraries on next slide

- Design environment variables can be set

- Use tech library defaults if variables not set

- set voltage 2.5 (volts)

- set temp 40 (degrees celsius/centigrade)

- set process I (process variation # if available)

#### Available 8HP technology files

- Located in: \$CMOS8HP/synopsys/

- Each file contains data for each library cell for a specific operating voltage and temperature

#### Directory / Technology File

```

typ_v120_t025 / PnomV1p20T025_STD_CELL_8HP_12T.db

typ_v150_t025 / PnomV1p50T025_STD_CELL_8HP_12T.db

fast_v132_tm40 / PbcV1p32Tm40_STD_CELL_8HP_12T.db

fast_v132_tm55 / PbcV1p32Tm55_STD_CELL_8HP_12T.db

fast_v160_tm40 / PbcV1p60Tm40_STD_CELL_8HP_12T.db

fast_v160_tm55 / PbcV1p60Tm55_STD_CELL_8HP_12T.db

slow_v108_t125 / PwcV1p08T125_STD_CELL_8HP_12T.db

slow_v140_t125 / PwcV1p40T125_STD_CELL_8HP_12T.db

```

#### Design environment variables/commands

"drive" strength = 1/R of output driver (default 0)

Transition delay= Rdriver\*Cinput "load" = capacitive load (units from tech library) (default 0)

"fanout\_load" = #units (associated with input pins)

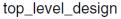

#### Example: define drive characteristics

- current\_design top\_level\_design

- set\_drive 1.5 {I1 I2}

- current\_cell sub\_design2

- set\_driving\_cell -lib\_cell IV {I3}

- set\_driving\_cell -lib\_cell AN2 -pin Z -from\_pin B {14}

- set\_fanout\_load 4 {out1 out2}

(define external input drives)

(resistance units from library)

(define input drivers for U2)

(default pin = IV output)

(arc from AN2 gate input B to output Z)

(#fanout units for output pins)

#### Wire Load Table (not available for 8HP)

- Estimate effects of wire length & fanout on resistance,

capacitance and area of net

- Affects switching times/delays

- Precise delays known only after place and route

- Function of cell sizes, fanouts, wire characteristics

- Wire Load Table may be provided by vendor

- Determined from analysis of previous process runs

- Variables:

- wire\_load\_library name (lib to which designed mapped - or NIL)

- wire\_table name (if named table loaded)

- wire\_tree (best,balanced,worst, or not set)

- wire\_load\_mode (top, segmented)

## Setting design constraints

- Design rule constraints: rules from library vendor for proper functioning of the fabricated circuit

- Must not be violated

- ▶ Common constraints: transition time, fanout load, capacitance

- Design optimization constraints: user-specified timing and area optimization goals

- DC tries to optimize these without violating design rules

- ► Common constraints: timing and area

#### Design rule constraints

- max\_fanout = max #loads a net can drive

- Input pins have fanout\_load attribute.

(load they place on driving nets)

Output pins have max\_fanout attribute.

(max load they can drive)

Example: Pin N drives loads A and B

- Pin A has fanout load value 2.0

- Pin B has fanout\_load value 3.0

- Pin N requires max\_fanout ≥ 5.0 to drive A and B

Otherwise, use different cell or insert a buffer to drive the net.

N

- Change max\_fanout attribute to restrict it more than its default value

set\_max\_fanout 5 [object\_list] (object\_list is list of ports)

- Other design rule constraints:

- max\_transition (output pins): transition time to change logic values

- max\_capacitance (output pins): sum of net and pin capacitances driven by output

#### Design optimization constraints

#### Speed

- path delays (min,max)

- clock specifications (period/frequency/duty)

#### Area

- speed is primary goal

- optimize area if timing constraints met

- target area 0 forces small as possible

- set\_max\_area 2000

- Choose realistic constraints (within 1-10%)

- avoid extra buffers/gates on loaded nets

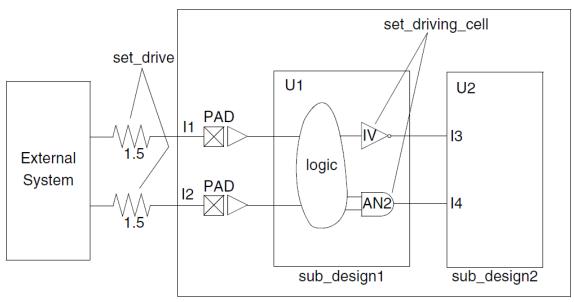

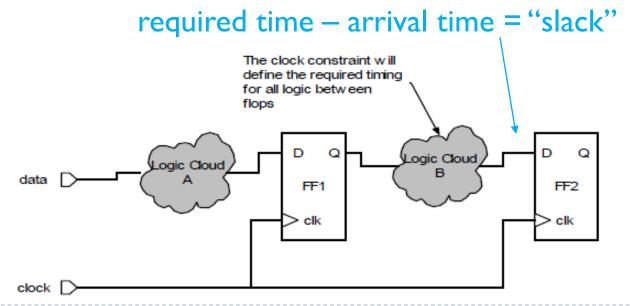

### Timing path types

#### Path delays of interest

- Combinational: primary input to primary output (in2 -> out2)

- 2. Primary input to register input (in1 -> FF1/D1)

- Clock/register output to primary output (clk -> Q2 -> out1)

- 4. Clock/register output to register input (clk -> Q1 -> D2)

### Timing Constraints

- Simple: specify target clock frequency

- Advanced: specify globally or on specific blocks

- Clock: period/frequency, pulse width, duty cycle

- Input: arrival time, transition times, driver strength

- Dutput: required time, transition times

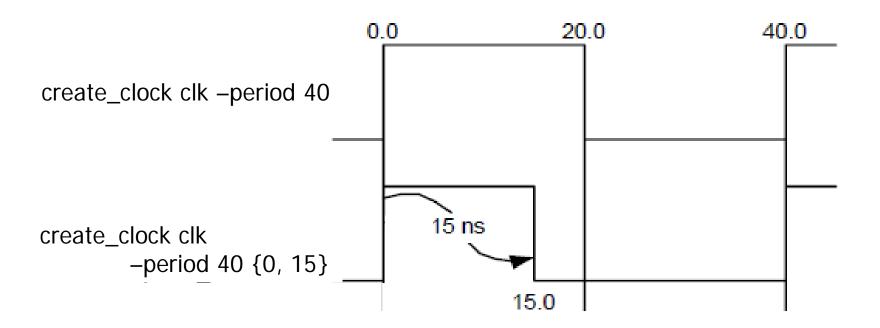

#### Clock specifications

- Define required period/waveform for each clock

- create\_clock ckname —period 5

- create\_clock ckname -period 5 -waveform {2 4}

- ▶ period=5, rise at 2, fall at 4

- DC does not automatically imply clock signals

- create\_clock -name ckname -period 5

- creates a "virtual clock" associated with a port/pin

- Clock latency = delay through clock network

- set\_clock\_latency 2.1 -rise CLK1

- set\_clock\_latency 0.7 -source CLK I

- from clock origin to clock pin

- Clock uncertainty = margin of error to allow variances

- set\_clock\_uncertainty -setup 0.2 CLK I

- set\_clock\_uncertainty —hold 0.2 CLK I

Add 0.2 margin on either side of clock edge to account for variances in clock network

## Clock constraint examples

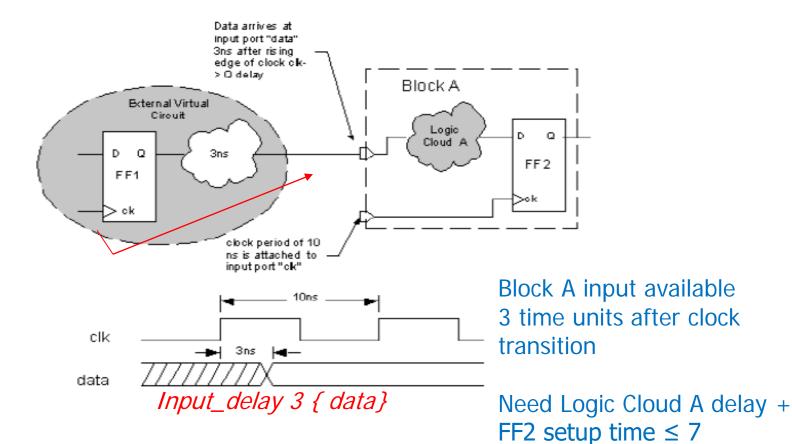

#### Input and output delays

- Delay from clock edge through "external" logic to an input port or internal pin.

- set\_input\_delay 2.3 {in | in 2}

- default input delay = 0

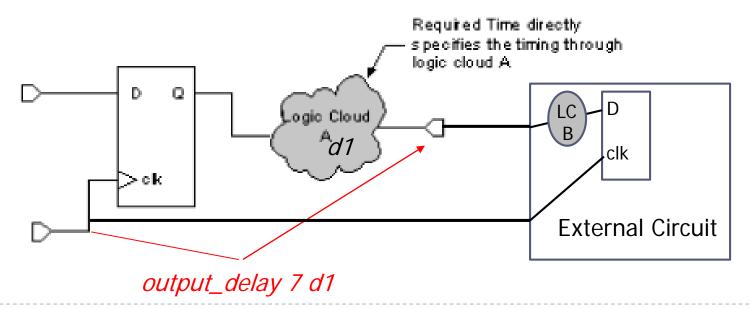

- Time a signal is required at output port by external destination before a clock edge

- external circuit logic delay + external ff setup time

- set\_output\_delay 7 —clock CLK I [all\_outputs]

- default output delay = 0

## Input constraints

- Arrival time from <u>previous</u> ckt to input pin, relative to clock.

- attribute: input\_delay (default is 0)

- command: set\_input\_delay 3 -clock clk dpin

#### Output constraints

Time from clock to valid output at pin, to be used by external ckt

attribute: output\_delay

- command: set\_output\_delay 7 -clock CLK d1

Example: Clock cycle = 20

External ckt flip-flop setup time = 2

External ckt logic cloud (LC B) delay = 11

Output at d1 needed by 20 - (11 + 2) = 7

### Sequential circuit example

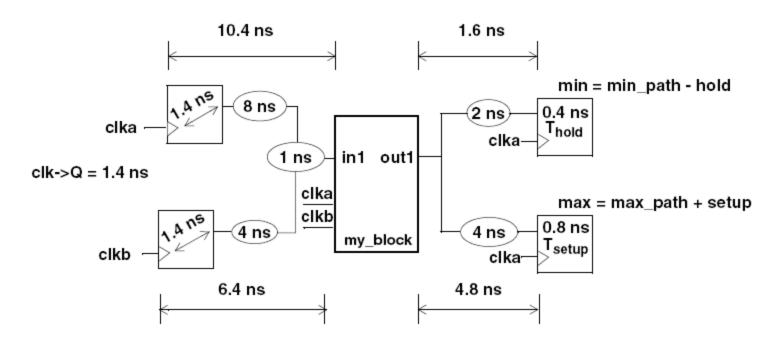

create\_clock -period 20 -waveform {5 15} clka create\_clock -period 30 -waveform {10 25} clkb set\_input\_delay 10.4 -clock clka in1 set\_input\_delay 6.4 -clock clkb -add\_delay in1 set\_output\_delay 1.6 -clock clka -min out1 set\_output\_delay 4.8 -clock clka -max out1

Required clock periods

Arrival at input pin from previous clock edge

Setup time of output pin from next clock edge

#### Path-based commands

- Path startpoint = input pin or register clock pin

- ▶ Path endpoint =output pin or register data pin

- Path constraint

```

set_max_delay -from from-list -to to-list value

```

- to/from-list = port, pin, clock or cell names

- If clock in *from-list*: all paths affected by that clock

- If clock in to-list: all related register data pins

- Register data pin: FFI or FFI/D

- Can specify —rise and/or —fall times

- Can add -through P to capture paths passing through P

- Can specify [all\_outputs] or [all\_inputs]

#### Path delay examples

#### Max delay requirements

- set\_max\_delay 10 -to out1 —from Reset

- set\_max\_delay 5.1 -from {ff1 ff2} -to {o1 o2}

- set\_max\_delay 3 —from busA[\*] —to u I /Z

- set\_max\_delay 6 —to [all\_outputs]

- ▶ If no "from list", constrain paths from all start points

- set\_max\_delay 8 —from [all\_inputs]

- If no "to list", constrain paths to all end points

- Above also applies to: set\_min\_delay

## Compiling the design

#### Compile (and optimize) the design

- compile –map\_effort \$mapEffort I

- design hierarchy preserved

- map\_effort = medium(default) or high

- compile –ungroup\_all –map\_effort \$mapEffort I

- ▶ design "flattened" (ungrouped all levels collapsed)

- compile –incremental\_mapping –map\_effort \$mapEffort2

- work on it some more incremental improvements

#### High-effort compile

- compile\_ultra

- use on high-performance designs, tight time constraints

- specify -no\_autoungroup to preserve hierarchy

#### Synthesis Output Files

- Design.v verilog structural netlist

- change\_names -rules verilog

- write –format verilog –output file.v

- Design.sdf standard delay file for timing simulation

- write\_sdf -version 1.0 file.sdf

- Design.rep synthesis report (timing, area, etc)

- redirect file.rep {report\_timing}

More timing options on

redirect —append file.rep {report\_area —hier } next slide.

- Design.ddc Synopsys database format (to view in DV)

- write —format ddc —hierarchy -o file.ddc

- ▶ **Design.sdc** constraints for Encounter place/route

- write\_sdc file.sdc

- Design.pow power estimate

- redirect file.pow { report\_power }

#### Additional timing report options

#### report\_timing

-to {list of signals}

-from {list of signals}

-through {list of pins}

-max\_paths N

-loops {timing loops}

Inputs/flipflop outputs to these signals

Flip-flop outputs/inputs to these signals

Paths that go through these pins

Number of paths to report

Timing loops (comb. logic feedback)

### Balancing Loads

- Resolve load violations throughout the design

- Fix loads after changing attributes, without rerunning optimize

- Load balancing always done as part of optimize

- ▶ Pays attention to OUTPUT\_LOADS, OUTPUT\_FANOUTS

- Mostly used at boundaries of hierarchical modules

- Optimize balances loads within modules

- Command:

```

balance_loads [design-name] [-single]

```

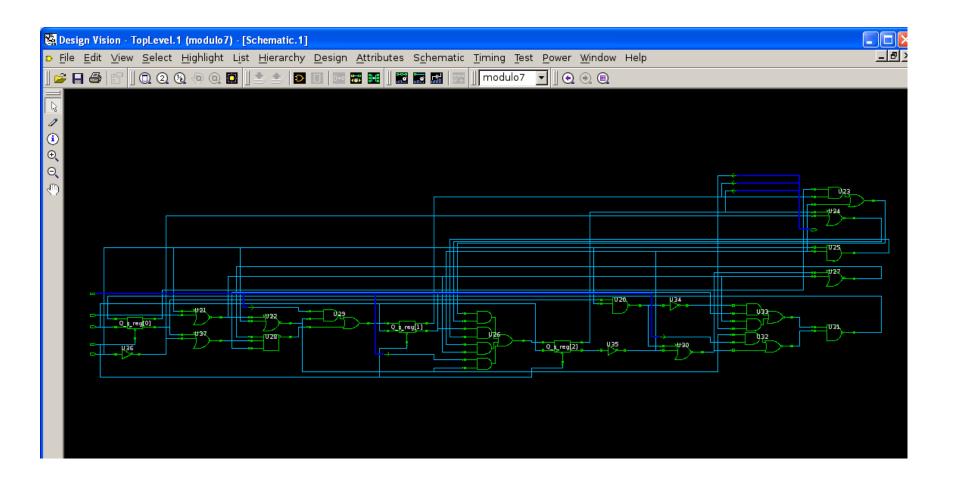

## DesignVision window

## Modulo7 counter in DesignVision