# ASIC Physical Design Top-Level Chip Layout

### References:

- M. Smith, Application Specific Integrated Circuits, Chap. 16

- Cadence Virtuoso User Manual

## Top-level IC design process

- Typically done before individual circuit block layouts

- Top-level netlists usually created before any layout

- Create top-level schematic

- "Components" are functional blocks and I/O pads

- Blocks include IP and user-created modules

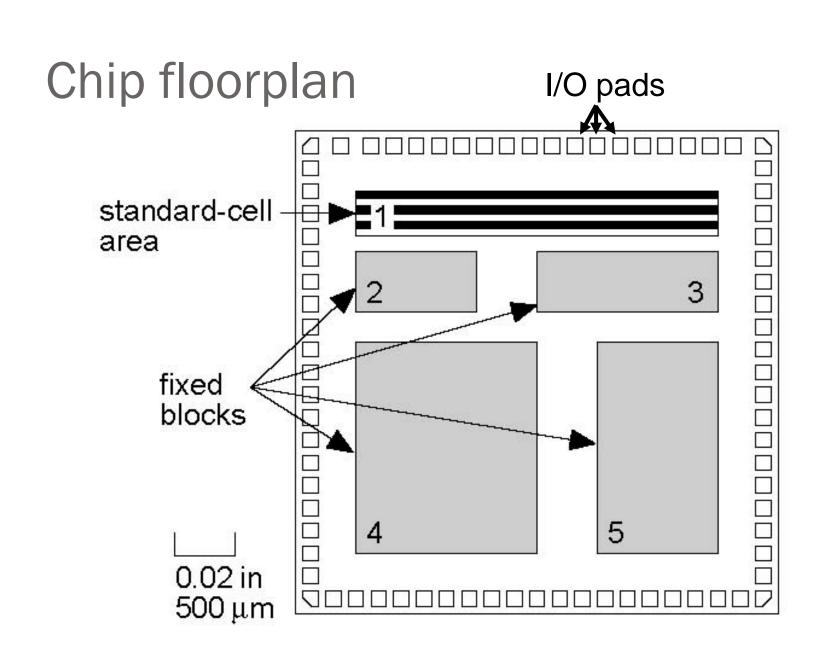

- Create a chip "floor plan" from the schematic

- Place functional blocks and I/O pads

- Connections shown as overflows

- Route top-level connections (automatic or interactive)

- Eliminate overflows, DRC errors, shorts

- Create layouts of user-designed modules

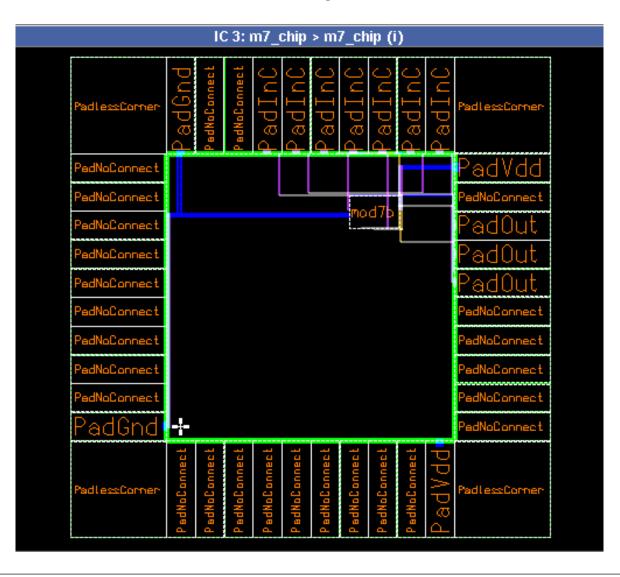

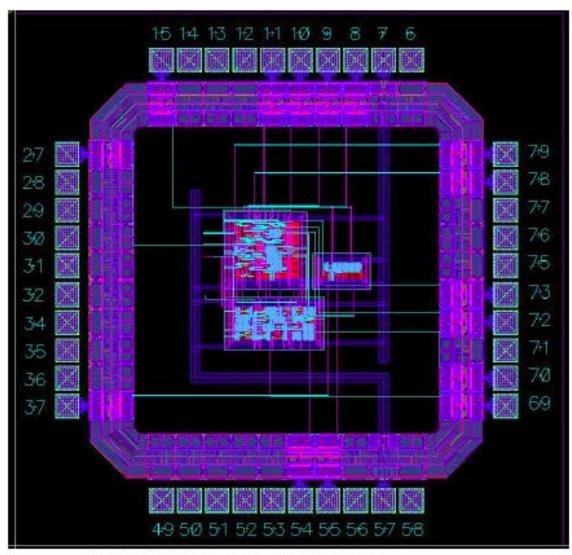

### Modulo-7 counter in pad frame

## Floorplanning (Smith text chap. 15, 16)

- Floorplanning: arrange major blocks prior to detailed layout to optimize chip area

- input is a **netlist of circuit blocks** (hierarchical)

- after system "partitioning" into multiple ICs

- estimate layout areas, shapes, etc.

- Flexible blocks shape can be changed

- Fixed block shape/size fixed

- do initial placement of blocks (keep highly-connected blocks close)

- decide location of I/O pads, power, clock

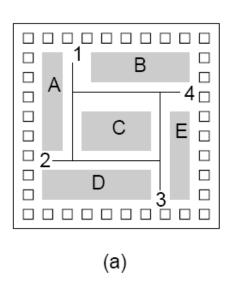

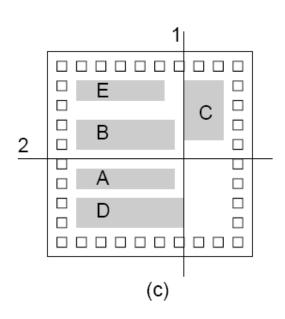

### Floorplan a cell-based IC (Fig. 16.6)

- may have to fit into "die cavity" in a package

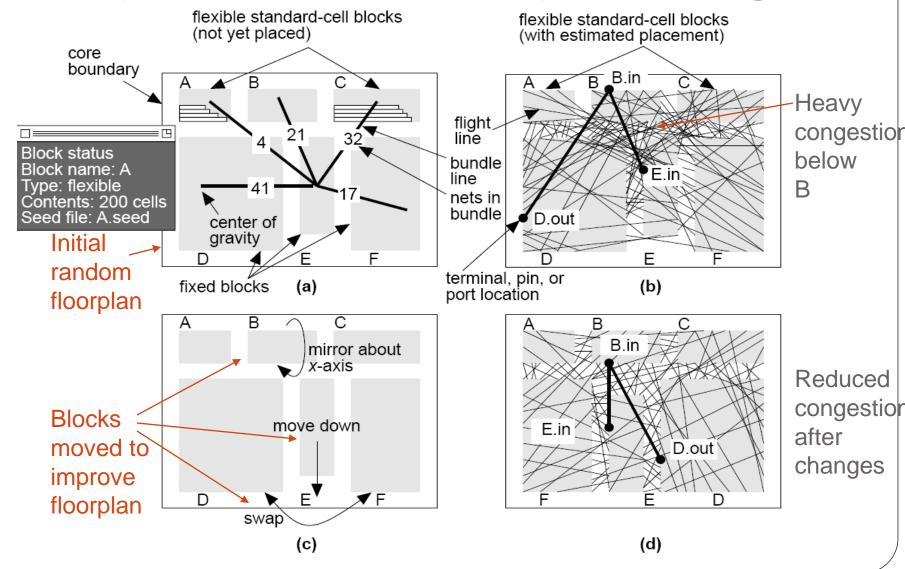

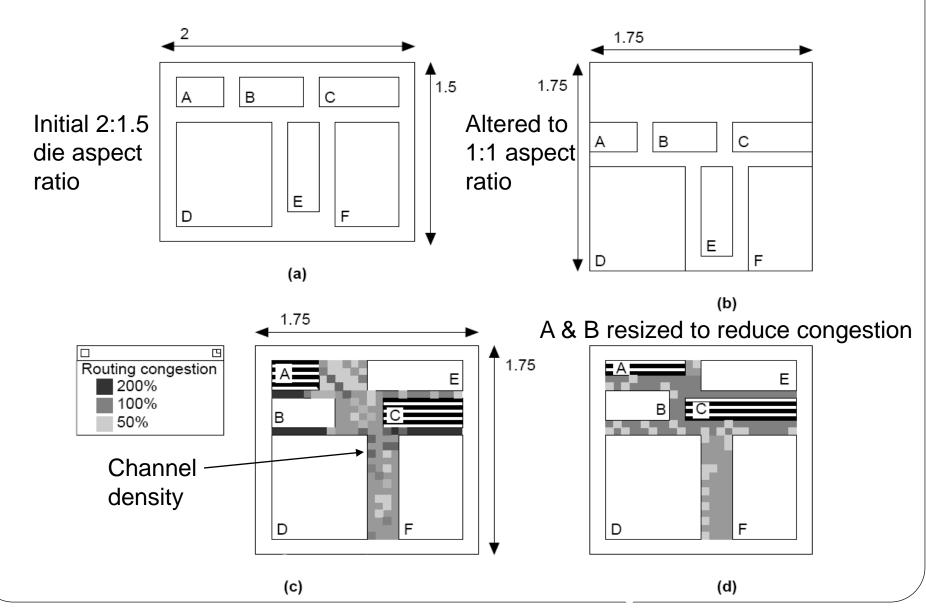

# Congestion analysis (Fig. 16.7)

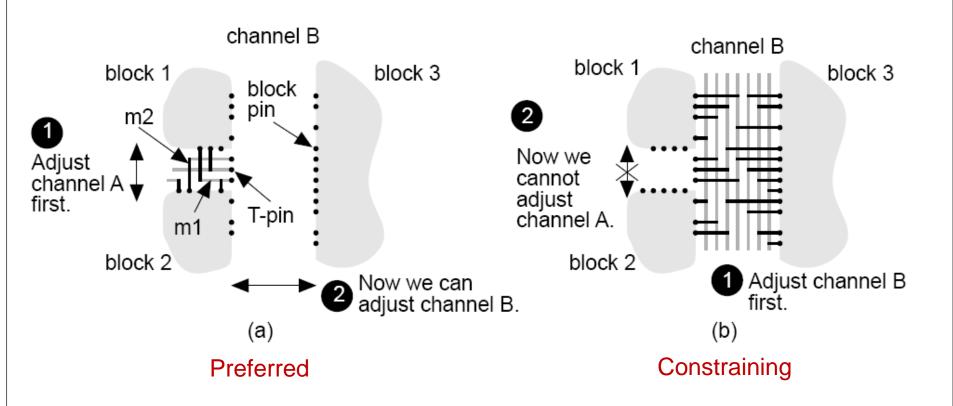

# Routing a T junction

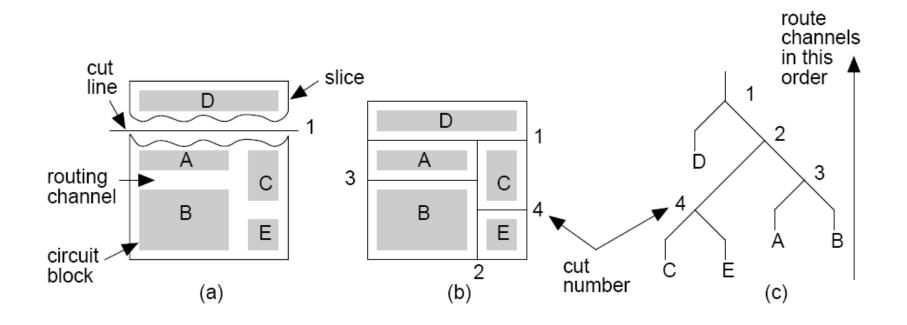

# Define channel routing order

- Make "cuts" (slice in two) to separate blocks

- •Slicing tree, corresponding to sequence of cuts, determines routing order for channels

- route in inverse order of cuts

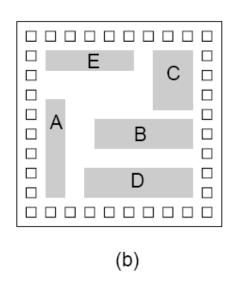

# Non-slicing structure

Cyclic constraint prevents channel routing

Cannot find slicing floorplan without increasing chip area

Slicing floorplan possible, but inefficient in use of chip area

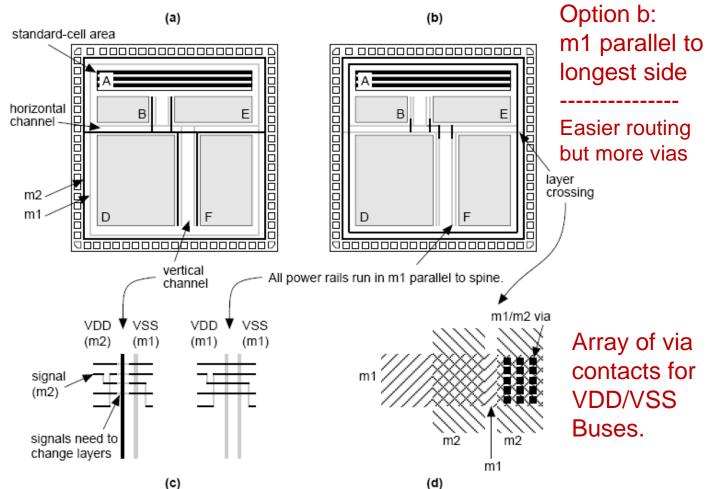

### Power distribution

Uses special power pads, wires, routing

Option a: m1 for VSS m2 for VDD

-----

layers

Potential problems in routing channel

Many layer changes/vias if VDD/VSS on different

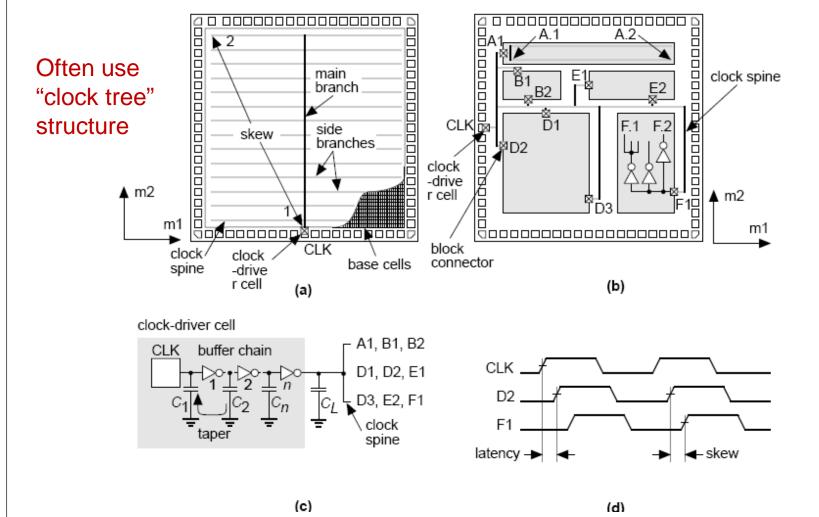

## Clock distribution (minimize skew)

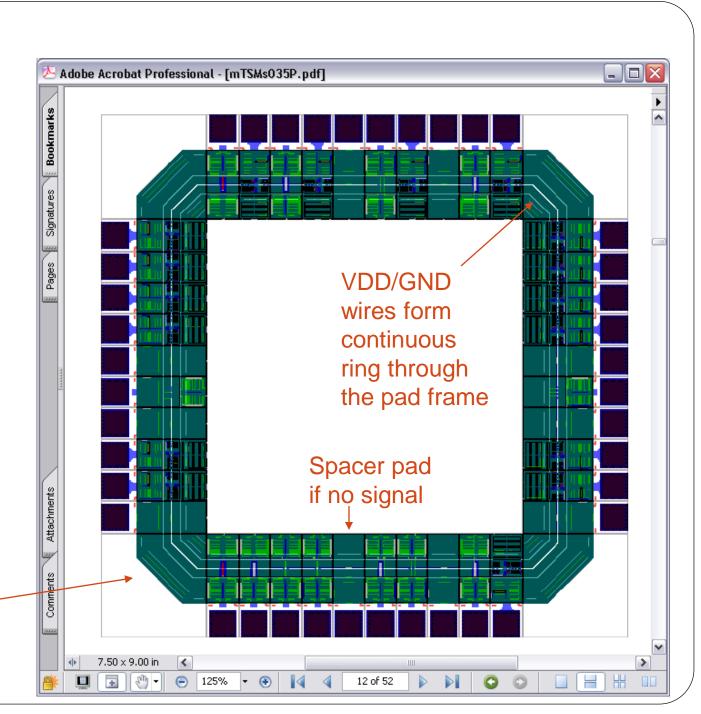

## MOSIS SCMOS Pad Library

- Includes 6 pad types:

- Input & output pads with buffers

- VDD & GND pads with ESD

- Analog IO pad with ESD

- Analog reference pad with ESD

- Assemble into a "frame" in which pads butt against each other

- Allows VDD & GND wires to form a continuous ring

- Special "spacer" and "corner" pads complete the ring

- ADK tools will generate a pad frame from a schematic

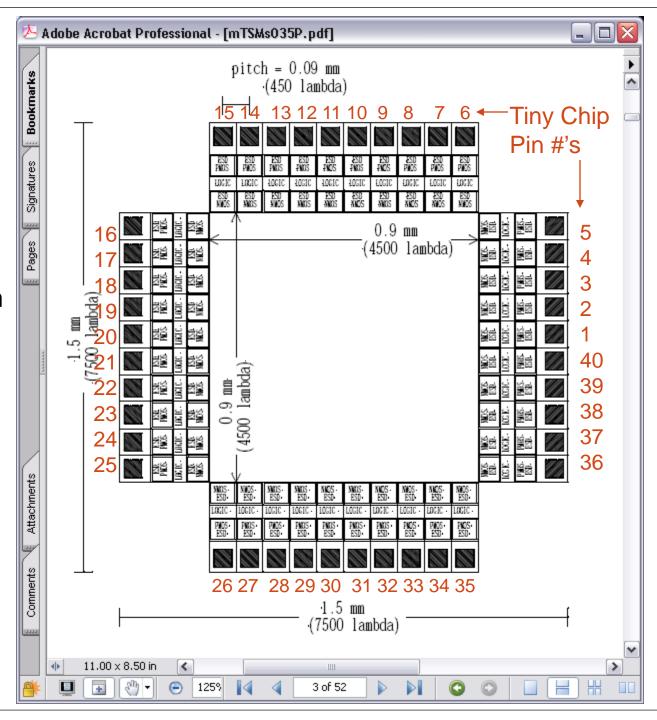

### MOSIS TSMC 0.35um Hi-ESD Pad Frame

(I) lambda=0.30um

MOSIS

TSMC 0.35um

Hi-ESD

Pad Frame

Physical layout

Corner pad (passes VDD/GND)

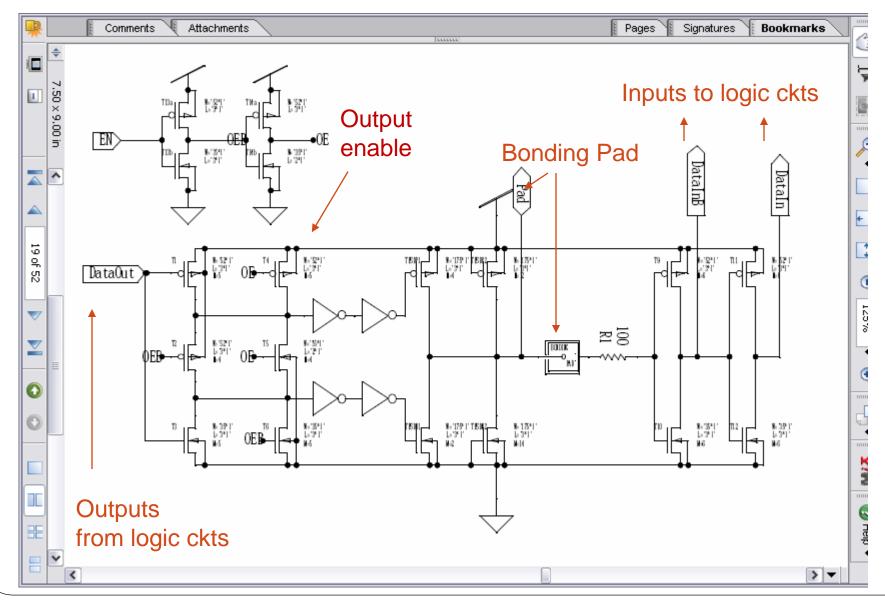

## MOSIS I/O Pad Schematic

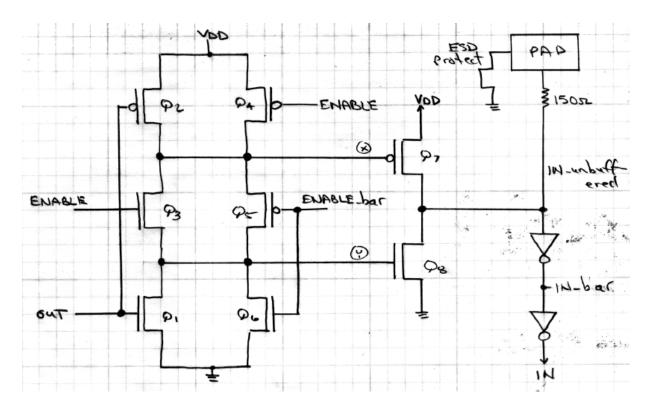

# Simplified pad circuit

| ENABLE = O (ENABLE - har = 1)    | ENABLE = 1                               | _a          |

|----------------------------------|------------------------------------------|-------------|

| 0, 46                            | P3 on - (x)= 0= out => Inverted by 91/90 | >           |

| Of on - pulls to you => P7 off   | O4 off                                   | , C.        |

| 90 of - pulls & to CND => 08 off | TO SEC.                                  |             |

| 96 00 - 6413 0 10 513 28 61      | O6 oft                                   | 11/10/05/01 |

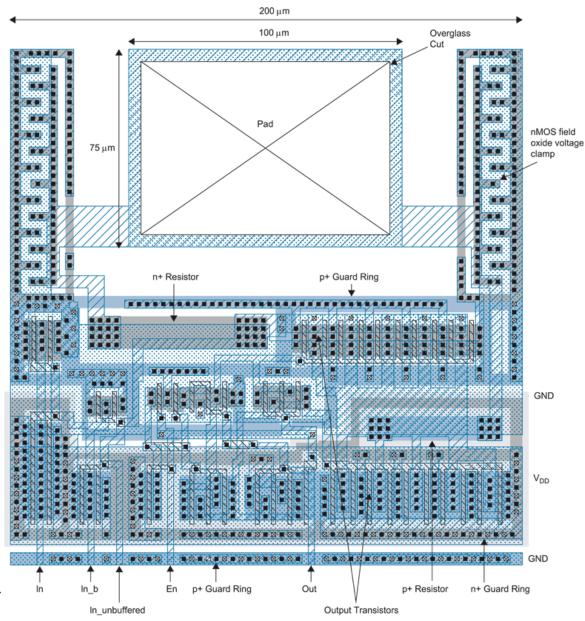

### MOSIS 1.6 um bidirectional pad

Source: Weste, "CMOS VLSI Design"

To Core

FIG 12.23 MOSIS 1.6 µm bidirectional pad. Color version on inside front cover.

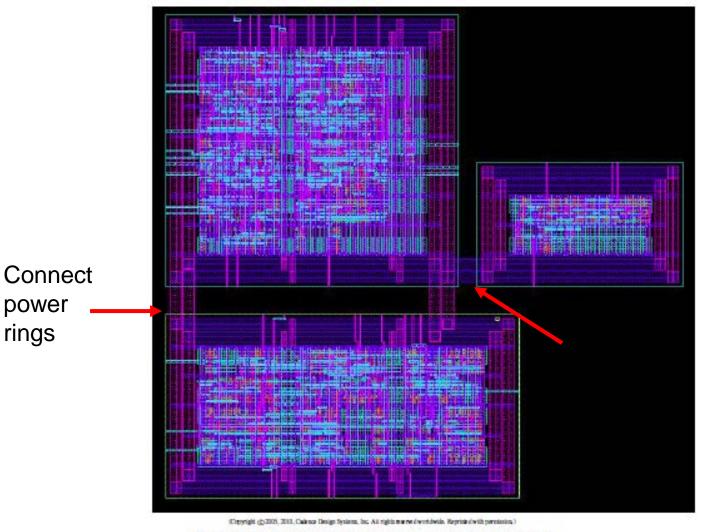

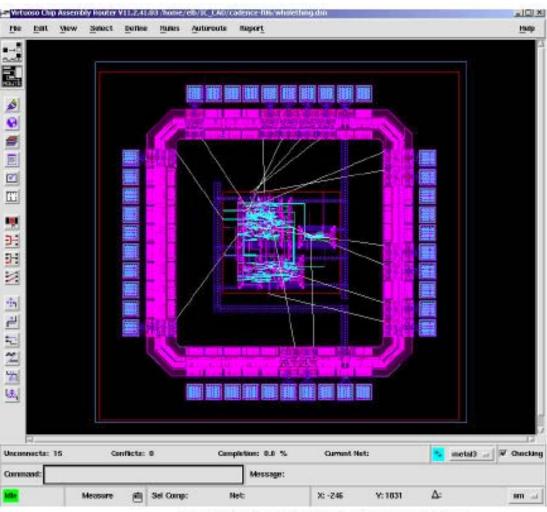

### ASIC frame + core in Virtuoso

#### Process:

- 1. Create "core" block

- 2. Create pad frame

- 3. Connect them

Copyright (c) 2005, 2010, Carlossy Design Systems, Inc. All rights one resolvent devide. Regards dwith parameters.)

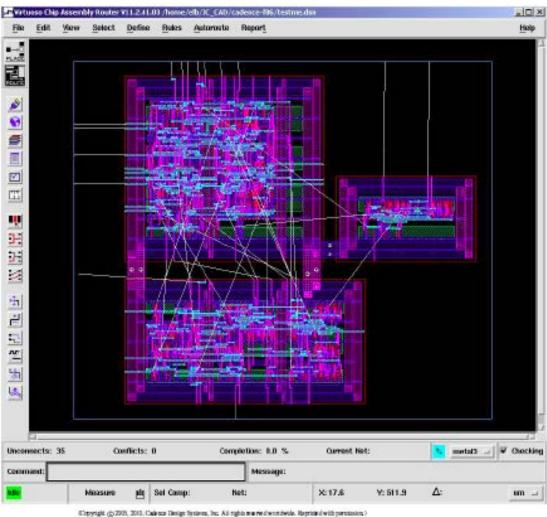

Figure 12.22: Frame and core after routing in Virtuoso

## Top-level bottom-up design process

- Generate block layouts and for <u>each block</u>:

- Import the GDSII (or DEF) stream into a Virtuoso library

- Import the Verilog netlist into the library

- Perform DRC and LVS on each block until "clean"

- Create a schematic symbol from the netlist in the library

- Create a block diagram/schematic in Virtuoso "Composer"

- Create a library for the top-level circuit block and create a schematic view

- Instantiate schematic symbols from the library

- Interconnect with nets and add pins

- Check and save

- Create a layout from the schematic diagram

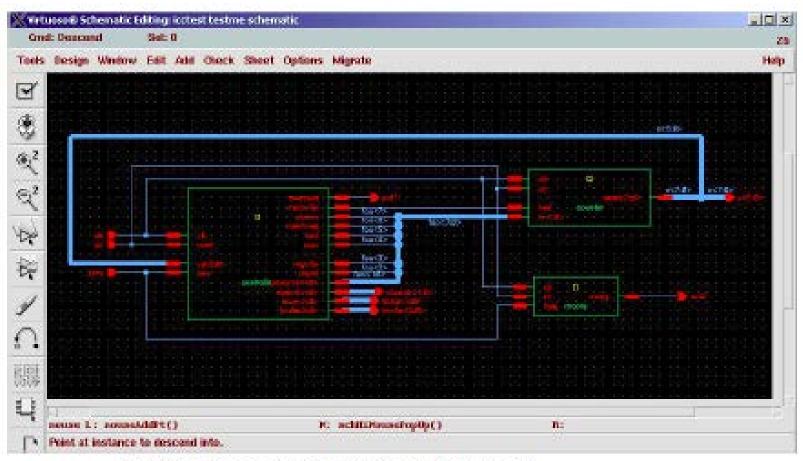

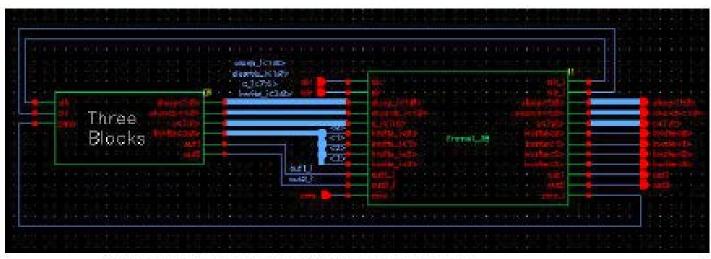

### Top-level block schematic in "Composer"

Copyright (5/2005, 2010, Codence Design Systems, Inc. All rights manned wondwide. Reprint dwith particulous 3

Figure 12.1: Starting schematic showing the three connected modules

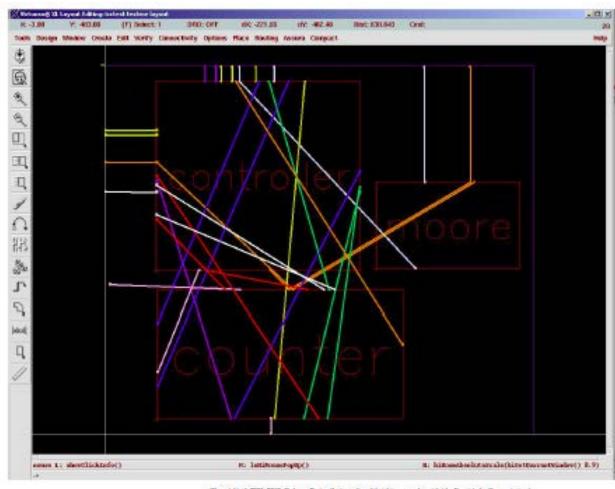

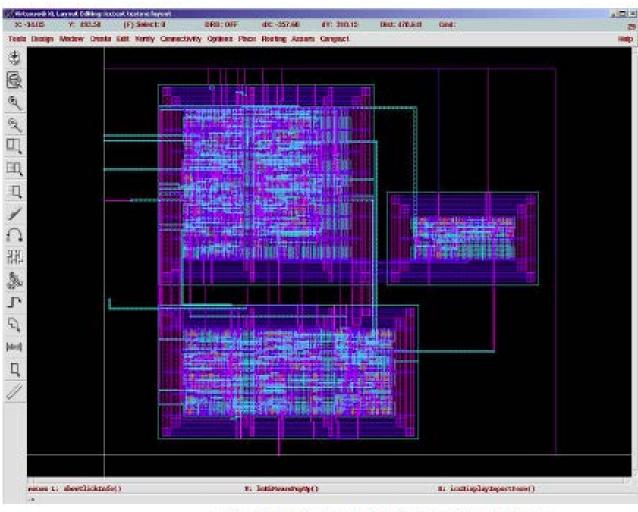

Before module and I/O placement

outside

boundary

Virtuosoff XI. Layout Editing: icchest testme layout Y: 715.65 Dist: Tools Design Window Create Edit Verify Connectivity Options Place Routing Assura Compact Blocks initially nouse L: showtlickInfo() V: leitiNousePopUp() %:hiZogeAbsoluteScale(hi@etGurrent

Copyright ⊕ 2005, 2010, Chale see Design Systems, Inc. All rights married work dwindwide. Reprint dwith parasitation )

Figure 12.3: Initial layout before module and I/O placement

## After placing modules and pins

Clayright (\$200), 2010, Calesco Design Systems, Inc. All rights meaned workfields. Reprinted with permission.)

Figure 12.4: A placement of modules and IO pins with unrouted nets turned on

## Power routing between blocks

Figure 12.5: Layout showing placement and power routing before routing

### Nets shown as "overflows"

Figure 12.7: Initial coar window

### Routed circuit block

Copyright (\$2004, 2010, Codesco Disago Systems, Inc. All rights merved workfeiths. Reprinted with permission.)

Figure 12.10: Final routed circuit (shown in Virtuoso window)

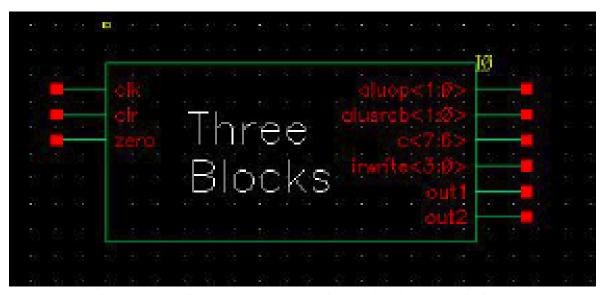

### Block symbol (to connect to I/O pads)

(Copyright (C) 2004, 2010, Cash nor Design Systems, Inc. All rights are ned worldwide. Reprint dwith permission.)

Figure 12.11: Symbol for the Three Blocks example core

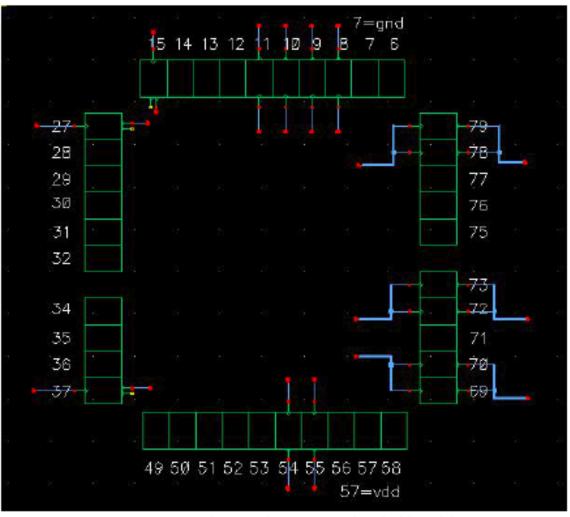

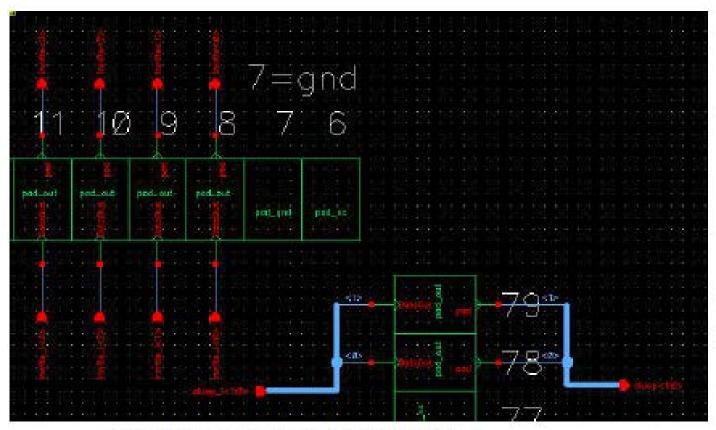

# Pad frame with signal wires

Copyright (\$20%, 2010, Colonce Draign Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 12.12: Pad frame with signal wires

## Zoomed view of pad frame

Copyright (c) 2005, 2010, Cadence Design Systems, Inc. All rights was re-diversified. Reprint divide personnes.)

Figure 12.13: Pad frame with signal wires (zoomed view)

# Schematic: block + pad frame

Copyright (g. 2015, 2011, Cultural Design Systems, Inc. All rights on the deventionine. Reprint dwith permission 3

Figure 12.14: Frame and core components connected together

### Placement of frame and core

Copyright (\$,20%, 2010, Calesco Draigs Systems, Inc. All rights married workly bla. Reprised with permission.)

Figure 12.19: Frame and core placed in Virtuoso-XL

## Power/ground routed manually

Figure 12.20: Frame and core placed in Virtuoso-XL with vdd and gnd routing completed

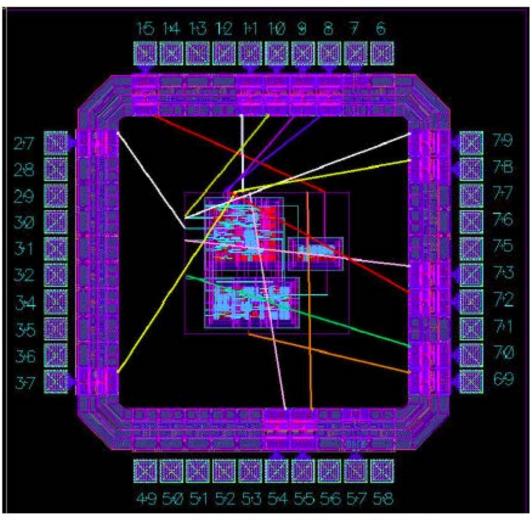

# Before signal routing

Copyrigit (g) 2005, 2010, Cubrace Draign Systems, Inc. All rights moved worshville. Reprinted with permission, 1

Figure 12.21: Frame and core before routing in ccar

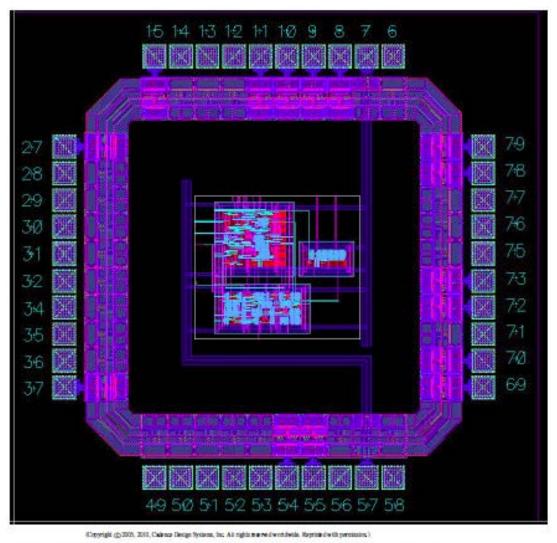

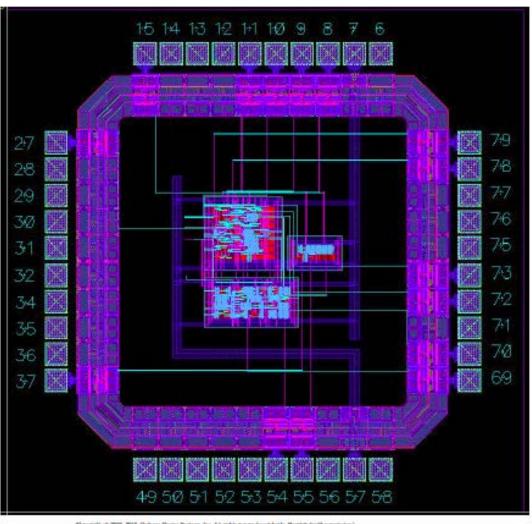

# After routing – final layout

Copyright (c) 2005, 2010, Carbona Classico Systems, Inc. All rights are resolved devide. Reprise (with personnes)

Figure 12.22: Frame and core after routing in Virtuoso