# VHDL 2 – Combinational Logic Circuits

Reference: Roth/John Text: Chapter 2

## Combinational logic

- -- Behavior can be specified as concurrent signal assignments

- -- These model concurrent operation of hardware elements entity Gates is

```

port (a, b,c: in STD_LOGIC;

```

```

d: out STD_LOGIC);

```

```

end Gates;

```

```

architecture behavior of Gates is

```

```

signal e: STD_LOGIC;

```

begin

```

-- concurrent signal assignment statements

e <= (a and b) xor (not c); -- synthesize gate-level ckt</p>

d <= a nor b and (not e); -- in target technology</p>

```

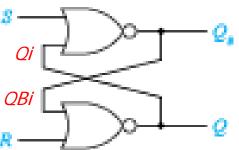

## Example: SR latch (logic equations)

entity SRlatch is port (S,R: in std\_logic; --latch inputs Q,QB: out std\_logic); --latch outputs end SRlatch;

architecture eqns of SRlatch is

signal Qi,QBi: std\_logic; -- internal signals <sup>R</sup> begin

QBi <= S nor Qi; -- Incorrect would be: QB <= S nor Q; Qi <= R nor QBi; -- Incorrect would be: Q <= R nor QB; Q <= Qi; --drive output Q with internal Qi QB <= QBi; --drive output QB with internal QBi "reference" end;

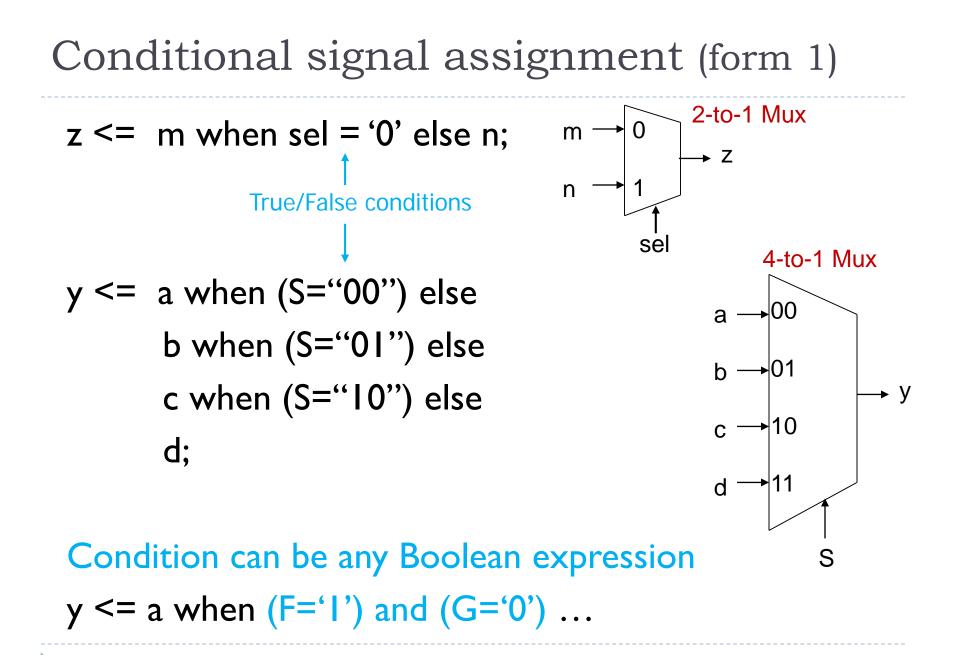

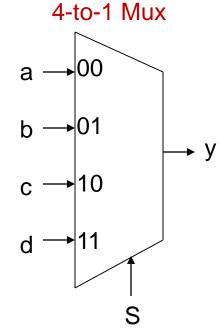

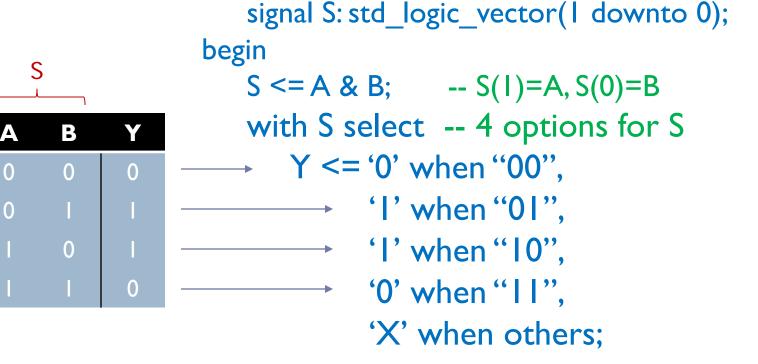

Conditional signal assignment (form 2) -- One signal (S in this case) selects the result signal a,b,c,d,y: std\_logic; signal S: std logic vector(0 to 1); 4-to-1 Mux begin with S select y <= a when "00", b when "01". ► V c when "10", →10 d when "II"; --Alternative "default" \*: d when others;

\* "std\_logic" values can be other than '0' and '1'

32-bit-wide 4-to-1 multiplexer

signal a,b,c,d,y: std logic vector(0 to 31); signal S: std logic vector(0 to 1); begin **→**|00 with S select b —•101 y <= a when "00", b when "01". c when "10", S d when "II":

--y, a,b,c,d can be **any type**, as long as they match

32-bit-wide 4-to-1 multiplexer

-- Delays can be specified if desired signal a,b,c,d,y: std logic vector(0 to 31); 4-to-1 Mux signal S: std logic vector(0 to 1); begin **Optional non-delta** h →01 with S select delays for each option ► V **c** →10  $y \le a a fter I ns when "00",$ d →11 blafter 2 nslwhen "01", clafter I ns when "10", S d when "II";

a->y delay is 1ns, b->y delay is 2ns, c->y delay is 1ns, d->y delay is δ

Truth table model as a conditional assignment

Conditional assignment can model the truth table of a switching function (without deriving logic equations)

& is the concatenate operator, merging scalars/vectors into larger vectors

#### Example: full adder truth table

ADDin <= A & B & Cin; --ADDin is a 3-bit vector

S <= ADDout(0); --Sum output (ADDout is a 2-bit vector)

Cout <= ADDout(1); --Carry output</pre>

with ADDin select ADDout <= "00" when "000", "01" when "001", "01" when "010". "10" when "011", "01" when "100", "10" when "101", "10" when "110", "||" when "|||", "XX" when others;

| ADDout |   |     | ADDin |   |

|--------|---|-----|-------|---|

| Α      | В | Cin | Cout  | S |

| 0      | 0 | 0   | 0     | 0 |

| 0      | 0 | Ι   | 0     | I |

| 0      | I | 0   | 0     | I |

| 0      | I | I   | I     | 0 |

| I      | 0 | 0   | 0     | I |

| I      | 0 | I   | I     | 0 |

| I      | I | 0   | I     | 0 |

| Ι      | I | I   | I     | I |

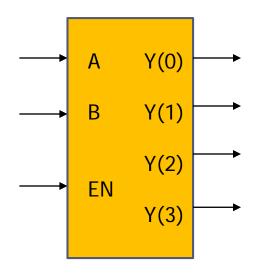

## Example: 2-to-4 decoder

```

library ieee; use ieee.std logic 1164.all;

entity decode2 4 is

port (A,B,EN: in std logic;

Y: out std logic vector(3 downto 0));

end decode2 4;

architecture behavior of decode2 4 is

signal D: std logic vector(2 downto 0);

begin

D <= EN & B & A; -- vector of the three inputs

with D select

Y <= "0001" when "100", --enabled, BA=00

"0010" when "101", --enabled, BA=01

"0100" when "110", --enabled, BA=10

"1000" when "111", --enabled, BA=11

"(0000)" when others; --disabled (EN = 0)

```

Structural model (no "behavior" specified)

architecture structure of full\_add1 is

component xor -- declare component to be used

port (x,y: in std logic;

z: out std\_logic); library entity architecture

end component;

for all: xor use entity work.xor(eqns); -- if multiple arch's in lib. signal x1: std\_logic; -- signal internal to this component begin -- instantiate components with "map" of connections G1: xor port map (a, b, x1); -- instantiate 1<sup>st</sup> xor gate G2: xor port map (x1, cin, sum); -- instantiate 2<sup>nd</sup> xor gate ...add circuit for carry output... Associating signals with formal ports

component AndGate port (Ain I, Ain\_2 : in std\_logic; -- formal parameters Aout : out std\_logic); end component; AndGate begin Ain 1 Aout -- positional association of "actual" to "formal" 71 Ain 2 AI:AndGate port map (X,Y,ZI); -- named association (usually improves readability) A2:AndGate port map (Ain  $2 \ge Y$ , Aout $\ge Z2$ , Ain  $1 \ge X$ ); -- both (positional must begin from leftmost formal) A3:AndGate port map (X, Aout => Z3, Ain\_2 => Y);

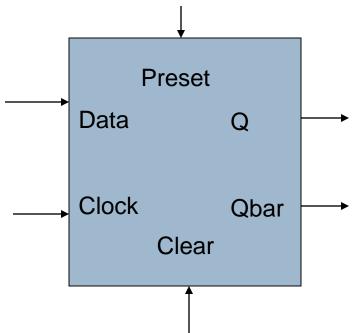

## Example: D flip-flop (equations model)

entity DFF is port (Preset: in std logic; Clear: in std logic; Clock: in std logic; Data: in std logic; Q: out std logic; Qbar: out std logic); end DFF;

## 7474 D flip-flop equations

architecture eqns of DFF is signal A,B,C,D: std\_logic; signal QInt, QBarInt: std\_logic;

begin

A <= not (Preset and D and B) after I ns; B <= not (A and Clear and Clock) after I ns; C <= not (B and Clock and D) after I ns; D <= not (C and Clear and Data) after I ns; Qint <= not (Preset and B and QbarInt) after I ns; QBarInt <= not (QInt and Clear and C) after I ns; Q <= QInt; -- Can drive but not read "outs" QBar <= QBarInt; -- Can read & drive "internals"

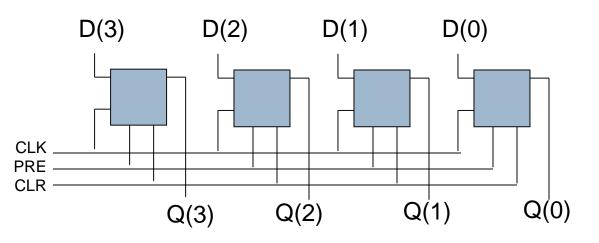

4-bit Register (Structural Model)

entity Register4 is

port ( D: in std\_logic\_vector(0 to 3);

Q: out std\_logic\_vector(0 to 3);

Clk: in std\_logic;

Clr: in std\_logic;

Pre: in std\_logic);

end Register4;

## Register Structure

architecture structure of Register4 is component DFF -- declare library component to be used port (Preset: in std\_logic; Clear: in std logic; Clock: in std logic; Data: in std logic; Q: out std logic; Qbar: out std logic); end component; signal Qbar: std\_logic\_vector(0 to 3); -- dummy for unused FF Qbar outputs begin -- Signals connect to ports in order listed above F3: DFF port map (Pre, Clr, Clk, D(3), Q(3), Qbar(3)); F2: DFF port map (Pre, Clr, Clk, D(2), Q(2), Qbar(2)); F1: DFF port map (Pre, Clr, Clk, D(1), Q(1), Qbar(1)); F0: DFF port map (Pre, CIr, Clk, D(0), Q(0), Qbar(0)); end;

#### Register Structure (with open output)

architecture structure of Register4 is -- declare library component to be used component DFF port (Preset: in std\_logic; Clear: in std\_logic; Clock: in std\_logic; Data: in std logic; Q: out std logic; Qbar: out std\_logic); end component; begin -- Signals connect to ports in order listed above F3: DFF port map (Pre, Clr, Clk, D(3), Q(3), OPEN); F2: DFF port map (Pre, CIr, Clk, D(2), Q(2), OPEN); FI: DFF port map (Pre, Clr, Clk, D(1), Q(1), OPEN); F0: DFF port map (Pre, Clr, Clk, D(0), Q(0), OPEN); end; **Keyword OPEN indicates** an unconnected output

#### VHDL "Process" Construct

(Processes will be covered in more detail in "sequential circuit modeling")

- Process statements are executed in sequence

- Process statements are executed once at start of simulation

- Process halts at "end" until an event occurs on a signal in the "sensitivity list"

- Allows conventional programming language methods to describe circuit behavior

## Modeling combinational logic as a process

```

--<u>All</u> signals referenced in process <u>must</u> be in the sensitivity list.

entity And_Good is

port (a, b: in std_logic; c: out std_logic);

end And Good;

architecture Synthesis Good of And Good is

begin

process (a,b) -- gate sensitive to events on signals a and/or b

begin

c <= a and b; -- c updated (after delay on a or b "events"

end process;

-- This process is equivalent to the simple signal assignment:

c <= a and b:

```

## Bad example of combinational logic

```

-- This example produces unexpected results.

entity And Bad is

port (a, b: in std logic; c: out std logic);

end And Bad;

architecture Synthesis Bad of And Bad is

begin

process (a) -- sensitivity list should be (a, b)

begin

c \leq a and b; -- will not react to changes in b

end process;

end Synthesis Bad;

-- synthesis may generate a flip flop, triggered by signal a

```